Fターム[5F033NN08]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | コンタクトホールへの穴埋め構造 (6,462) | 深さの異なる複数のコンタクトホールの穴埋め (88)

Fターム[5F033NN08]に分類される特許

21 - 40 / 88

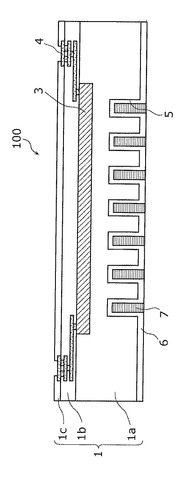

半導体装置及び半導体装置の製造方法

【課題】チップ面積及びコストを増大させることなく、熱抵抗を低減できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】半導体装置100は、半導体層1aと配線層1bとを有する半導体基板1と、半導体層1aの中央部に半導体層1aの表面から所定の深さまで形成された活性領域3と、活性領域3及び活性領域3の周辺の配線層1bに形成され、半導体層1aと電気的に接続された接続用電極4と、半導体層1aから発生する熱を放熱する放熱部とを備え、放熱部は、半導体層1aの裏面から活性領域3の近傍まで凹状に形成された少なくとも1の第1の孔5に充填された放熱体7を有する。

(もっと読む)

半導体装置及び電子機器

【課題】マスク数を増加させることなく、ブラックマスクを用いずに反射型または透過型の表示装置における画素開口率を改善する。

【解決手段】画素間を遮光する箇所は、画素電極167をソース配線137と一部重なるように配置し、TFTはTFTのチャネル形成領域と重なるゲート配線166によって遮光することによって、高い画素開口率を実現する。

(もっと読む)

半導体装置およびその製造方法

【課題】吸湿性の高い絶縁膜を使用してもコンタクト又は配線の劣化を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板10上に第1の絶縁膜15を形成する工程(a)と、第1の絶縁膜15にホール24を形成する工程(b)と、ホール24の側壁上に、第1の絶縁膜15よりも水分を通しにくい第2の絶縁膜17を形成する工程(c)と、工程(c)の後、ホール24に導電体30を埋め込むことにより、プラグ19を形成する工程(d)とを備えている。

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

積層集積回路のための二面の相互接続されたCMOS

半導体装置及びその製造方法

【課題】深さの異なるコンタクトホールを同時に形成することを可能とした半導体装置を提供する。

【解決手段】第1の溝部7内に形成された第1の埋め込み配線11と、第2の溝部12内に形成された第2の埋め込み配線14と、第1の埋め込み配線11上に第1のコンタクトプラグ24が形成される第1のコンタクト形成領域23と、第2の埋め込み配線14上に第2のコンタクトプラグ26が形成される第2のコンタクト形成領域25とを備え、第1のコンタクト形成領域23の上面23aが第1の埋め込み配線11の上面11aよりも高い位置にあり、第2のコンタクト形成領域25の上面25aが第2の埋め込み配線14の上面14aと同じかそれよりも高い位置にあり、第1のコンタクト形成領域23の上面23aが第2のコンタクト形成領域25の上面25aと同じかそれよりも高い位置にある。

(もっと読む)

プロセス均一性及び熱消散を改善するダミーTSV(スルーシリコンビア)

【解決手段】

各々が能動回路領域を含むチップの積層体において、多重チップ積層体内の複数のスルーシリコンビア(TSV)開口をパターニングし、エッチングし、そして熱的伝導性材料で充填することによって、多重チップ積層体からの熱を熱的に伝導させるための複数のTSV構造が形成され、複数のTSV開口は、いずれの能動回路領域をも貫通せずに多重チップ積層体の実質的に全体を通って延びる第1の大きなTSV開口と、能動回路領域まで下に延びるが通過はしない第2の小さい開口と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】層間絶縁膜を除去するエッチング中に、異常エッチングを防止する。エッチング工程において加わる水圧や風圧によりガードリングの形状が変形して剥離し、欠陥が発生することを防止する。

【解決手段】半導体装置は、メモリセル領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた周辺回路領域と、ガードリング及び周辺回路領域上に設けられた支持体膜と、周辺回路領域内に設けられたコンタクトプラグとを有する。ガードリングとコンタクトプラグは、同一の導電材料から構成される。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極と拡散層に接続する共通コンタクトにおけるリークを防ぐ。

【解決手段】半導体装置は、拡散層が形成された基板と、基板上に形成されたゲート電極と、基板上にゲート電極よりも高い位置まで形成された第1絶縁層と、拡散層に電気的に接続され、第1絶縁層を貫通する第1コンタクトと、ゲート電極と電気的に接続された第2コンタクトと、第1絶縁層の上に形成された第2絶縁層とを備える。第1コンタクトと第2コンタクトとは第1絶縁層の上面以上の高さにおいて電気的に接続する。ゲート電極上と拡散層上は異なるコンタクトで形成されているため、ゲート電極のサイドウォールが減少することなく、リークを防ぐことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラートランジスタにおいて、ゲートコンタクトとシリコン基板との間のショートを抑制した半導体装置及びその製造方法を得るという課題があった。

【解決手段】半導体からなる基板1と、一面1aから突出され、前記半導体からなる第1の突出部2と、一面1aに設けられた溝部1cに充填された第1の絶縁体3と、第1の突出部2に隣接して一面3aから突出され、第1の絶縁体3からなる第2の突出部4と、第1の突出部2の側面を覆うゲート絶縁膜5と、ゲート絶縁膜5を覆うゲート電極6と、第1の突出部2に設けられた上部拡散層13と、下部拡散層14と、第2の突出部4の側面を覆うとともにゲート電極6に接続された連結電極60と、第1の突出部2及び第2の突出部4を覆う層間絶縁膜と、前記層間絶縁膜を貫通して連結電極60に接するゲートコンタクト10と、を有する半導体装置及びその製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置及びその製造方法

【課題】階段状に加工された複数の導電層と、各導電層に達し深さの異なる複数のコンタクトホールとの接続構造の信頼性を高めた半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、基板10の第2のコンタクト領域5上に設けられ、第2のコンタクト領域5と第1のコンタクト領域4との間に段差を形成する下地層45bと、下地層45bを覆って基板10上に設けられ、下地層45b上に積層された上段部81が階段状に加工された下層側積層体91と、下層側積層体91における第1のコンタクト領域4上に積層された下段部82の上に設けられ、階段状に加工された上層側積層体92と、階段状に加工された部分を覆う層間絶縁層62と、層間絶縁層62を貫通し階段状に加工された部分の各々の導電層WLに達して形成されたコンタクトホール内に設けられたコンタクト電極51と、を備えた。

(もっと読む)

半導体装置およびその製造方法

【課題】グラフェンのバリスティック伝導性を利用した低抵抗配線を備え、配線と配線接続部材の接続部分の構成の複雑化を抑えた半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、基板と、基板の上方に設けられ、積層された複数のグラフェンナノリボンシート122からなるグラフェンナノリボン層121を含む下層配線12と、複数のグラフェンナノリボンシート122の少なくとも1枚を貫通し、下層配線12と上層配線13とを接続するビア14およびバリアメタル15と、を有する。

(もっと読む)

シリコン貫通ビアのためのESD/アンテナダイオード

概略を述べると、アンテナダイオードが、少なくとも一部がTSVの周囲の排他的区域内に形成され、金属1層の導電体を介してTSV(シリコン貫通ビア)に接続されている。それと同時に、TSVは、排他的区域の外側に位置する1又は複数のトランジスタのゲートポリ又は拡散領域に接続している。 (もっと読む)

半導体装置及びその製造方法

【課題】深さの異なる複数のコンタクトホールの底部径のばらつきを抑制する半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、複数の導電層WL1〜WL4が階段状に加工された階段構造部を有する積層体と、階段構造部を覆って設けられた層間絶縁層43と、層間絶縁層43を貫通し、それぞれが対応する各段の導電層WL1〜WL4に達して形成された複数のコンタクトホール61〜64の内部に設けられたコンタクト電極60とを備え、複数のコンタクトホール61〜64の底部の孔径は略同じであり、下段側の導電層に達するコンタクトホールは、上段側の導電層に達するコンタクトホールよりも深く、上端部の孔径が大きい。

(もっと読む)

半導体集積回路装置

【課題】多層配線の下地半導体基板への配線引き出し部のコンタクト抵抗均一化を図った半導体集積回路装置の提供。

【解決手段】半導体集積回路装置は、半導体基板と、前記半導体基板上に複数層積層形成された配線と、前記配線の引き出し領域に前記配線の延長部として形成されて、所定幅のスペースを介して対向するメタル片対により構成されるフックアップ部73と、前記フックアップ部のメタル片対のスペースを貫通するように埋め込まれたコンタクト導体72とを有し、前記配線の少なくとも2層の間で前記フックアップ部のメタル片対のスペース幅を異ならせた。

(もっと読む)

半導体装置及びその製造方法

【課題】 半導体装置及びその製造方法に関し、埋込導体構造の密着性とCu拡散防止能を両立する。

【解決手段】 半導体基板上に設けた絶縁膜に設けた埋込導体用の凹部内に埋め込まれたCuまたはCuを最大成分とする合金からなるCu系埋込導体層と、前記凹部に露出する前記絶縁膜との間にCoを最大成分とするとともに、少なくともMn、O及びCを含むCoMn系合金層を設ける。

(もっと読む)

半導体装置及びその製造方法

【課題】 信号線の形成位置に関わらず、信号線とMIM構造のキャパシタ11との間で発生する寄生容量が抑制できるようにする。

【解決手段】 MIM構造のキャパシタ11と、絶縁膜12a,12bを介してMIM構造のキャパシタ11を挟む、少なくとも一対の遮蔽部13a,13bとを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】高信頼性でかつ高レイアウト密度配線と混載可能な容量素子を備えた半導体装置及びその製造方法を提供する。

【解決手段】本発明は、容量素子を有する半導体装置であって、アルミニウム合金膜102と、高融点金属膜を含む上層バリア膜103とを含む金属配線200aおよび下部電極200bと、下部電極200b上に形成された容量絶縁膜104と、容量絶縁膜104上に形成された上部電極105とを有する。高融点金属膜の膜厚は、40nm以上、80nm以下であり、容量絶縁膜104は、有機シランを原料としたシリコン酸化膜からなることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極との短絡を抑えたセルフアラインコンタクトを有する、製造コストの低い半導体装置およびその製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置100は、それぞれ半導体基板2上に形成され、それぞれゲート電極4a、4bを有し、互いの間のソース・ドレイン領域8aを共有する隣接したトランジスタ1a、1bと、ゲート電極4a上に形成された絶縁膜11aと、ゲート電極4b上に形成された絶縁膜11aよりも厚さの厚い領域を有する絶縁膜11bと、ソース・ドレイン領域8aに接続され、その中心位置がゲート電極4a、4bの間の中心位置よりもゲート電極4b側に位置するSAC14と、を有する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】ニッケル系メタル・シリサイドとコンタクト用メタル間でのコンタクト抵抗の低抵抗化がホールの微細化に伴って、困難になるという問題がることが、本願発明者の検討により明らかとなった。

【解決手段】本願の一つの発明は、ニッケル系メタル・シリサイドによりソース・ドレイン領域等のシリサイデーションを施したMISFETを有する半導体集積回路装置の製造方法において、プリ・メタル絶縁膜に設けられたコンタクト・ホールにバリア・メタルを形成する前に、シリサイド膜の上面に対して、窒素水素間結合を有するガスを主要なガス成分の一つとして含む非プラズマ還元性気相雰囲気中で、熱処理を実行するものである。

(もっと読む)

21 - 40 / 88

[ Back to top ]