Fターム[5F033NN19]の内容

半導体集積回路装置の内部配線 (234,551) | 層間構造の特徴点 (9,232) | ピラー、ペデスタル (100)

Fターム[5F033NN19]に分類される特許

1 - 20 / 100

半導体装置及び半導体装置の製造方法

半導体装置および半導体装置の製造方法

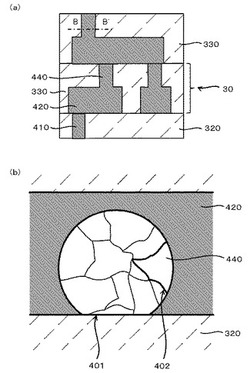

【課題】低抵抗の微細配線構造を有する半導体装置を提供する。

【解決手段】第1配線420は、半導体基板100上に設けられている。第1ビア440は、第1配線420上に設けられている。また、第1ビア440の底面は、第1配線420に接している。第1絶縁層330は、半導体基板100上に設けられ、少なくとも第1配線420の上面および第1ビア440の側面と接している。第1配線420および第1ビア440のうち各々の側面の少なくとも一部は、各々の金属の結晶粒を分断している。

(もっと読む)

半導体装置とその製造方法

【課題】 実施形態は、製造工程が簡便な手法によって製造した半導体装置を提供することを目的とする。

【解決手段】 実施形態の半導体装置は、実施形態にかかる半導体装置は、基板と、基板上に触媒金属膜と、触媒金属膜上にグラフェンと、前記グラフェン上に層間絶縁膜と、前記層間絶縁膜を貫通するコンタクトホールと前記コンタクトホールにカーボンナノチューブを水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した前記触媒金属膜上に又は前記層間絶縁膜を貫通するカーボンナノチューブを水素、窒素、アンモニアと希ガスの中から選ばれる1種以上のガスのプラズマで処理した前記触媒金属膜上に備えることを特徴とする。

(もっと読む)

半導体装置

【課題】半導体装置において、少なくとも容量素子とトランジスタとを有する回路要素が占める面積を小さくする。

【解決手段】第1のトランジスタと第2のトランジスタと容量素子とを有する半導体装置において、第2のトランジスタよりも上方に第1のトランジスタ及び容量素子を配置する。そして、第1のトランジスタのソース又はドレインの一方と、容量素子の一方の電極とを兼ねる共通電極を設ける。さらに、容量素子の他方の電極を共通電極よりも上方に配置する。

(もっと読む)

半導体装置の製造方法

【課題】 金属部材の表面に、再現性よくバリア膜を形成する技術が望まれている。

【解決手段】 基板の上に、下部バリア膜を形成する。下部バリア膜の上にシード膜を形成する。シード膜の一部の領域上に、導電部材を形成する。導電部材をエッチングマスクとして、シード膜をエッチングし、導電部材の形成されていない領域において、下部バリア膜を露出させる。下部バリア膜の表面には堆積しない条件で、導電部材の表面に選択的に上部バリア膜を成長させる。上部バリア膜をエッチングマスクとして、下部バリア膜をエッチングする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】縦型トランジスタの特性を悪化させることなく縦型トランジスタの設置面積を削減できる高集積化に適した半導体装置およびその製造方法を提供する。

【解決手段】一定の間隔を空けて配置された複数のピラー30が備えられ、複数のピラー30が、縦型トランジスタTのチャネルとして機能する半導体層からなるチャネルピラー1と、不純物拡散層からなり、前記チャネルピラー1の下部に接続されて縦型トランジスタTの一方のソースドレインとして機能する下部拡散層4に電気的に接続された引き上げコンタクトプラグ2とを含む半導体装置とする。

(もっと読む)

半導体装置およびその製造方法

【課題】 外部接続用電極の周囲を封止膜で覆ったCSPと呼ばれる半導体装置において、封止膜の上面側を研削するとき、外部接続用電極の上面にバリが発生しないようにする。

【解決手段】 メッキレジスト膜を用いた電解メッキにより外部接続用電極10を形成した後に、サーフェスプレーナーを用いて全ての外部接続用電極10の上部およびそれに対応するメッキレジスト膜の上面側を切って除去し、外部接続用電極10の高さを揃える。この場合、外部接続用電極10の上面にバリが発生することはない。次に、メッキレジスト膜を剥離し、封止膜11を形成し、封止膜11の上面側を研削し、外部接続用電極10上に封止膜11が僅か例えば厚さ数μm〜10μm残るようにする。この場合、外部接続用電極10の上部は研削しないため、外部接続用電極10の上面にバリが発生することはない。次に、外部接続用電極10の上面中央部に対応する部分における封止膜11に、レーザビームを照射するレーザ加工により、開口部12を形成する。

(もっと読む)

半導体装置の製造方法

【課題】異方性エッチングを利用して、1つの銅膜に配線パターンとビアパターンとを同時に形成することが可能な半導体装置の製造方法を提供すること。

【解決手段】バリア膜100上に、銅膜101を形成する工程と、銅膜101上に、第1のマスク材を形成する工程と、第1のマスク材をマスクに用いて、銅膜101をバリア膜100が露出するまで異方的にエッチングする工程と、第1のマスク材を除去した後、異方的にエッチングされた銅膜101上に、第2のマスク材を形成する工程と、第2のマスク材をマスクに用いて、銅膜101をその途中まで異方的にエッチングする工程と、前記第2のマスク材を除去した後、異方的にエッチングされた銅膜101上に、絶縁物を堆積させ、異方的にエッチングされた銅膜101周囲に、層間絶縁膜106を形成する工程と、を具備する。

(もっと読む)

配線基板、半導体装置、及びそれらの作製方法

【課題】集積化が進む配線基板、又は半導体装置において、導通不良を軽減する。信頼性の高い配線基板、又は半導体装置を歩留まり良く作製する。

【解決手段】多層配線構造を有する配線基板、又は半導体装置において、該配線に用いる導電層の接続構造に曲面を有する導電層を用いる。周囲の絶縁層の除去によって露出された下層の導電層の先端部は曲面であり、下層の導電層上に積層する上層の導電層の被覆性を良好とすることができる。曲面な表面を有するレジストマスクを用いて導電層をエッチング加工することによって曲面な表面を有する導電層を形成する。

(もっと読む)

パターン付基板の作製方法、及び半導体装置の作製方法

【課題】隣接する膜パターンの間隔を制御することが可能なパターン付基板の作製方法を

提供する。また、膜パターンの幅の制御が可能で、特に、幅が細く且つ厚みのあるパター

ン付基板の作製方法を提供する。また、アンテナのインダクタンスのバラツキが少なく、

起電力の高い導電膜を有する基板の作製方法を提供することを課題とする。また、歩留ま

り高く半導体装置を作製する方法を提供することを課題とする。

【解決手段】基板、絶縁膜又は導電膜上に珪素及び酸素が結合し且つ前記珪素に不活性な

基が結合する膜を形成した後、珪素及び酸素が結合し且つ前記珪素に不活性な基が結合す

る膜表面に印刷法を用いて組成物を印刷し、組成物を焼成して膜パターンを形成すること

を特徴とする。

(もっと読む)

回路基板及びその製造方法

【課題】配線抵抗が低く配線間の絶縁性の高い回路基板及びその製造方法を提供する。

【解決手段】基板上に、Cuを含む導電性材料の配線構造体を形成し、配線構造体の表面に、Cu−N結合を有する絶縁性の拡散防止膜を形成した後、拡散防止膜が形成された配線構造体を覆うように、絶縁膜を形成する。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】記憶素子の下にあるコンタクトプラグの上面の平坦性を改善し、信頼性の高い半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、半導体基板と、半導体基板上に設けられた複数のスイッチングトランジスタと、隣接する2つのスイッチングトランジスタ間に埋め込まれ、該隣接する2つのスイッチングトランジスタの各ゲートから絶縁されかつ該隣接する2つのスイッチングトランジスタのソースまたはドレインに電気的に接続され、上面がスイッチングトランジスタの上面よりも高い位置にあるコンタクトプラグと、コンタクトプラグの上面上に設けられ、データを記憶する記憶素子と、記憶素子上に設けられた配線とを備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】例えば、開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオン化された被着金属に、0.01eVから250eVの被着エネルギを与えるイオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。更に、その回路基板とその他のチップとを積層して、それらをボンディングワイヤで絶縁基板に支持されないリードへ接続する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】基板を薄板化しても基板の反りを抑制でき、耐熱性、機械特性に優れた絶縁膜で保護された半導体素子及びその製造方法を提供する。

【解決手段】基板1の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板の表面に、芳香族テトラカルボン酸及び芳香族テトラカルボン酸二無水物から選ばれる1種以上のアシル化合物を、前記芳香族ジアミンよりも1モル%以上多く反応して得られるポリアミド酸を含むポリイミド前駆体組成物を塗布し、イミド化して絶縁膜3を形成し、第1表面電極2及び絶縁膜3が少なくとも形成された基板1を、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

半導体素子及び半導体素子の製造方法

【課題】長期にわたって信頼性に優れた半導体素子及びその製造方法を提供する。

【解決手段】基板の一方の面に第1表面電極2を形成し、第1表面電極2が形成された基板1の表面にレジスト組成物を塗布し、プリベークしてレジスト膜10を形成し、該レジスト膜10を貫通して第1表面電極1上にコンタクトホールを形成し、このコンタクトホール内にコンタクト電極4を形成し、第1表面電極2が形成された基板の表面に、熱膨張率が2ppm/℃以上7ppm/℃未満の第1絶縁膜3aを形成し、次いで、該第1絶縁膜3a上に熱膨張率が7ppm/℃以上24ppm/℃以下の第2絶縁膜3bを積層して絶縁膜3を形成し、コンタクト電極4を介して絶縁膜上に第2表面電極5を形成し、第1表面電極2、第2表面電極5及び絶縁膜3が形成された基板の裏面側を支持体に固定し、第1表面電極側からダイシングして素子ユニットを分離して半導体素子を製造する。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

半導体ダイのコンタクト構造および方法

【課題】他の物体によって損傷、剥離、または亀裂を生じることなく、より粗野な処理、運送、および使用を可能にするよりよい緩衝を、半導体デバイスの金属化層に配置された低k誘電体層、ELK誘電体層、および/またはULK誘電体層の半導体ダイのコンタクトを形成するシステム、方法を提供する。

【解決手段】複数の誘電体層および導電層を含む基板101、複数の導電層の最上層115の1つと電気的に接続し、約15,000Åより大きい厚さを有する金属コンタクト105、および金属コンタクトと電気的に接続したコネクタを含む半導体デバイス。

(もっと読む)

半導体装置及びその製造方法

【課題】信頼性の高い半導体基板上の回路基板を低コストで供給する。

【解決手段】開口部101を介してチップ取り出し電極2を含む半導体基板1の一部表面が露出するようメタルマスク100を半導体基板1に被せ、イオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、半導体基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、半導体基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

回路基板

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】例えば、開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオン化された被着金属に、0.01eVから250eVの被着エネルギを与えるイオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

回路基板の製造方法

【課題】信頼性の高い回路基板を低コストで供給する。

【解決手段】開口部101を介してチップ取り出し電極2を含む基板1の一部表面が露出するようメタルマスク100を基板1に被せ、イオンプレーティング法により金属導体を形成した後、メタルマスク100を剥離することによって、基板1の一部表面に形成された金属導体からなる配線層21を形成する。これにより、フォトリソグラフィー法を用いることなく、基板上に配線層21を直接形成することができるため、生産性が高く低コストな回路基板を提供することが可能となる。

(もっと読む)

1 - 20 / 100

[ Back to top ]