Fターム[5F033PP23]の内容

半導体集積回路装置の内部配線 (234,551) | 導電膜の成膜方法 (14,896) | 成膜の方向性制御 (169) | バイアスを印加するもの (37)

Fターム[5F033PP23]に分類される特許

21 - 37 / 37

半導体装置の製造方法及び半導体装置の製造装置

【課題】Al膜の埋め込み性を向上させた半導体装置の製造方法、及び半導体装置の製造装置を提供するものである。

【解決手段】制御部は、ビアホールVHを有したシリコン基板Sの表面に金属膜BM1(Ti膜)と金属窒化膜BM2(TiN膜)を被覆させ、金属窒化膜BM2に被覆されたビアホールVHの内部にCVD法を用いてAl−CVD膜P1を形成させた。そして、制御部は、Al−CVD膜P1を埋め込む前に、ビアホールVHの底部に位置する金属窒化膜BM2の一部をスパッタし、ビアホールVHの底部の側壁に再付着窒化膜BMrを形成させた。

(もっと読む)

半導体装置およびその製造方法

【課題】多層配線構造を備えた半導体装置において、配線溝底面におけるバリアメタル膜の消失を回避しつつ、ビアプラグ下端において下層配線パターンと確実なコンタクトを実現する。

【解決手段】配線溝およびビアホールの側壁面および底面を覆うようにバリアメタル膜をスパッタ法により堆積する際に、前記バリアメタル膜の堆積を、層間絶縁膜主面上における堆積速度がスパッタエッチング速度よりも大きくなる第1の条件で前記バリアメタル膜の堆積を行う第1のスパッタ工程と、前記層間絶縁膜主面上における堆積速度とスパッタエッチング速度がほぼ等しくなる第2の条件で前記バリアメタル膜の堆積を行う第2のスパッタ工程により、実行する。

(もっと読む)

半導体装置

【課題】タンタルからなるバリアメタル膜がダメージを抑制もしくは低減された低比誘電率層間絶縁膜に接して設けられているとともに、Taバリアメタル膜およびこれに覆われた導電体の接続不良も抑制されている半導体装置を提供する。

【解決手段】半導体装置26は、比誘電率が3以下の低比誘電率層間絶縁膜8、バリアメタル膜21、導電体22を具備する。低比誘電率層間絶縁膜8には、開口部17,20が形成されている。バリアメタル膜21は、開口部17,20の内側を覆って設けられているとともに結晶構造が互いに異なるα−Taおよびβ−Taを含むタンタルの膜からなり、かつ、α−Taとβ−Taとの組成比が低比誘電率層間絶縁膜8に接する部分において1以上5以下となっている。導電体22は、開口部17,20に形成されたバリアメタル膜21上に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】バリア膜の構造を工夫することで、銅配線と絶縁膜との密着性を向上させることを可能とする。

【解決手段】基板11上の第1絶縁膜12に形成された第1配線17を被覆する第2絶縁膜21と、前記第2絶縁膜21に形成された配線溝25と、前記配線溝25の底部の前記第2絶縁膜21に形成されたもので前記第1配線17に通じる接続孔26と、前記接続孔26底部を除く前記配線溝25と接続孔26との内面に形成された第1バリア膜31と、前記接続孔26底部の前記第1絶縁膜12上に形成された第2バリア膜34と、前記第1バリア膜31および第2バリア膜を34介して前記配線溝25および前記接続孔26に埋め込まれた第2配線35(含むプラグ36)とを備えたことを特徴とする。

(もっと読む)

薄膜形成方法、銅配線膜形成方法

【要 約】

【課題】コンタクトホールやヴィアホールの導通抵抗を低下させる。

【解決手段】ターゲット20と成膜対象物17の間の空間をアノード電極4で取り囲み、アノード電極4に印加する正電圧と、成膜対象物17に印加する負電圧とを制御し浅穴の底面の堆積速度がエッチング速度よりも大きい状態を維持しながら、深穴の底面では、エッチング速度を堆積速度以上の大きさにする。深穴底面にバリア膜を形成せずに、浅穴底面、及び深穴と浅穴の側面にバリア膜を形成することができるので、銅配線膜が深穴底面下の導電性物質と直接接触でき、導通抵抗が低下する。

(もっと読む)

100%又はそれより大きい段差被覆性を有する相互接続部金属化プロセス

【課題】 構造底部のバリア材料厚と比べると、構造側壁においてより厚いバリア材料被覆範囲を有する相互接続構造体、及び、そのような相互接続構造体を製造する方法を提供すること。

【解決手段】 構造底部のバリア材料厚と比べると、構造側壁においてより厚いバリア材料被覆範囲を有する相互接続構造体、及び、そのような相互接続構造体を製造する方法が提供される。本発明の相互接続構造体は、従来のPVDプロセス、従来のイオン化プラズマ堆積、CVD、又はALDによってバリア材料が形成される従来技術の相互接続構造体と比べると、半導体業界のための改善された技術拡張性を有する。本発明によると、構造底部のバリア材料厚(ht)より厚い、構造側壁のバリア材料厚(wt)を有する相互接続構造体が提供される。すなわち、本発明の相互接続構造体において、wt/ht比は、100%に等しいか又はそれより大きい。

(もっと読む)

成膜方法、プラズマ成膜装置及び記憶媒体

【課題】オーバハング部分を生ぜしめることなく凹部の内壁面に十分な厚さのシード膜やバリヤ層等の薄膜を形成することができる成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器24内でプラズマにより金属ターゲット70をイオン化させて金属イオンを発生させ、前記金属イオンを前記処理容器内の載置台34上に載置した表面に凹部2,4を有する被処理体へバイアス電力により引き込んで前記凹部内を含む前記被処理体の表面に薄膜を形成するようにした成膜方法において、前記バイアス電力を、前記被処理体の表面が実質的にスパッタされない領域下にて変化させるようにする。これにより、オーバハング部分を生ぜしめることなく凹部の内壁面に十分な厚さのシード膜やバリヤ層等の薄膜を形成する。

(もっと読む)

狭いトレンチ中でスーパー第2結晶粒の成長を発生させる方法

【課題】本発明は、小さなトレンチ中で拡大されたCu結晶粒を得るための方法に関する。更には、半導体装置に使用される狭いトレンチおよび/またはビア中に電気化学的に堆積された銅中で、拡大された銅結晶粒を形成する方法、またはスーパー第2結晶粒成長を誘起する方法に関する。

【解決手段】再結晶した電気化学的に堆積された銅(ECD−Cu)により充填された、少なくとも1つのトレンチおよび/または少なくとも1つのビアを含む半導体装置において、再結晶したECD−Cuの少なくとも80%、85%、90%、91%、または92%が、[100]方位で、少なくとも10ミクロンの寸法を有する銅結晶粒からなる。

(もっと読む)

成膜方法、プラズマ成膜装置及び記憶媒体

【課題】メッキ処理を用いることなくプラズマスパッタだけで微細な凹部を金属によりボイドを発生させることなく埋め込むことができる成膜方法を提供する。

【解決手段】処理容器24内でプラズマにより金属ターゲット70をイオン化させて金属イオンを含む金属粒子を載置台34上に載置した被処理体Wにバイアス電力により引き込んで凹部4を埋め込むようにした成膜方法において、バイアス電力を、被処理体の金属ターゲットに対する対向面に関して、金属粒子による成膜レートとプラズマガスによるスパッタエッチングのエッチングレートとが略均衡するような状態になるように設定して凹部内に金属膜を形成する成膜工程と、金属粒子の供給を停止した状態で被処理体を金属膜の表面拡散が生ずる所定の温度範囲に加熱維持することにより金属膜の原子を凹部の底部に向けて移動させる拡散工程とを交互に複数回繰り返す。

(もっと読む)

キャパシタ構造の製造方法及びキャパシタ素子の製造方法

【課題】MIMキャパシタ構造の絶縁膜の静電破壊の原因となる上部電極膜への電荷蓄積を抑制できるキャパシタ構造の製造方法を提供する。

【解決手段】キャパシタ構造の製造方法は、基板10上に下部電極膜71を形成する工程と、下部電極膜71上に絶縁膜72を形成する工程と、アースされた導電性部材であるクランプリング81を絶縁膜72の外周近傍の所定領域に接触させる工程と、スパッタ法によって絶縁膜72上、及び、絶縁膜72上とクランプリング81とを繋ぐ領域に上部電極膜73を形成する工程と、絶縁膜72からクランプリング81を引き離す工程と有する。このようにして、上部電極膜73を形成する際に、上部電極膜73に電子が到達し難くしているので、上部電極膜73に蓄積された電荷を原因とする絶縁膜72の静電破壊の発生率を低下させることができる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】配線と配線を接続する接続部のバリア膜の構造を最適化し、エレクトロマイグレーション特性を向上させる。

【解決手段】半導体基板上の第1層配線M1上に形成された層間絶縁膜TH2中に配線溝HM2およびコンタクトホールC2を形成した後、これらの内部にバリア膜PM2aを、コンタクトホールC2の底部の全周に渡ってコンタクトホールC2の底部の中央部から側壁に向かってその膜厚が増加するよう形成し、このバリア膜PM2a上に銅膜(PM2b、PM2c)を形成した後、CMP法により研磨することにより第2層配線M2と接続部(プラグ)P2を形成する。その結果、接続部(プラグ)P2を介して第2層配線M2から第1層配線M1へ流れる電流の幾何学的な最短経路と、電気的に抵抗が最小となるバリア膜PM2aの薄い部分が一致せず、電流経路を分散することができ、電子の集中を起こりにくくできる。

(もっと読む)

半導体装置の製造方法

【課題】 Low−k絶縁膜のエッチング時の表面荒れを抑制する。

【解決手段】 下層側のCu配線が形成された層、SiC膜1およびSiOC膜2の積層構造に対し、SiOC膜2をエッチングしてSiC膜1に達するビアホール用の開口部5を形成し、開口部5に連通する配線溝6a,6bを形成した後に、その開口部5の底のSiC膜1をエッチングしてビアホールを形成する際に、そのビアホールおよび配線溝6a,6bの表面にエッチング生成物の堆積膜を形成する。この堆積膜によってビアホールおよび配線溝6a,6bが形成されたSiOC膜2のエッチングプラズマに晒された表面を平坦化する。その後は、Ta膜の形成、メッキCuの埋め込みを行ってビアおよび上層側のCu配線を形成する。

(もっと読む)

半導体装置とその製造方法

【課題】

強誘電体キャパシタ上部にWプラグを採用することにより生じた上部電極コンタクト周辺の新たな問題を解決する。

【解決手段】

半導体装置は、半導体基板と、前記半導体基板に形成され、絶縁ゲートとその両側のソース/ドレインを有するMOSトランジスタと、前記半導体基板上方に形成され、下部電極、強誘電体層、上部電極を有する強誘電体キャパシタと、前記上部電極上に形成され、上部電極の厚さの1/2以下の厚さを有し、水素耐性のある金属膜と、前記強誘電体キャパシタと金属膜を埋め込む層間絶縁膜と、前記層間絶縁膜を貫通し、前記金属膜に達し、導電性グルー膜とタングステン体とを含む導電性プラグと、前記層間絶縁膜上に形成され、前記導電性プラグに接続されたアルミ配線と、を有する。

(もっと読む)

成膜方法及びプラズマ成膜装置

【課題】ボイド等を生ずることなく被処理体の凹部を埋め込むことができ、しかもメッキ処理の負担を軽くして、表面の研磨処理の負担も軽減することができる成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器14内でプラズマにより金属ターゲット56をイオン化させて金属イオンを発生させ、金属イオンを処理容器内の載置台20上に載置した被処理体Sにバイアス電力により引き込んで凹部2が形成されている被処理体に金属膜74を堆積させて凹部を埋め込むようにした成膜方法において、バイアス電力を、被処理体の金属ターゲットに対する対向面に関して、金属イオンに対する引き込みによる成膜レートとプラズマガスによるスパッタエッチングのエッチングレートとが略均衡するような状態になるように設定して成膜処理を行う。これにより、ボイド等を生ずることなく被処理体の凹部を埋め込むことができる。

(もっと読む)

半導体装置およびその製造方法

【課題】 ボイドの移動経路となるバウンダリーが顕著に低減されるため、SIV不良の発生を効果的に抑制することができ、信頼性の高い半導体装置を提供する。

【解決手段】 相対的に広幅の第2銅配線110,126の上面において、銅のグレインが数10μm程度と非常に大きい。第2銅配線110,126の配線幅は0.3μm〜数10μm程度であるので、第2銅配線110,126の上面において配線幅方向のバウンダリーが顕著に低減され、第2銅配線110,126とビア113との接続部分にボイドが集中・合一して大きなボイドが形成されることを抑制することができ、SIVの発生が効果的に抑制される。相対的に狭幅の第1銅配線111,127の面方位はEM耐性を向上させるために主にCu(111)であり、相対的に広幅の第2銅配線110,126の面方位はSIV耐性を向上させるために主にCu(200)である。

(もっと読む)

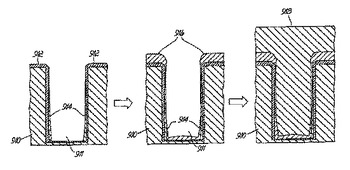

イオン化物理蒸着方法

iPVDシステム(200)は、真空チャンバー(30)内で突出部(14)を最小化または除去しながら、フィールド(10)と底部(15)被覆と比較して側壁(16)被覆性を向上させる処理を用いて、障壁層材料(912)のような均一な材料を半導体基板(21)上の高いアスペクト比のナノサイズの開口部(11)に蒸着するために調整される。そのiPVDシステム(200)は、そのターゲットから材料をスパッタするために、低いターゲットパワーと50mTより高い圧力で動作される。RFエネルギーは、高密度プラズマを生成するそのチャンバーに連結される。小さなRFバイアス(数ボルト未満)は、特に、底部における被覆性を高めることを助けるために印加されることができる。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】低抵抗且つ高バリア性を有するバリアメタルを提供する。

【解決手段】バリアメタル201 が、配線溝16の底面及び側壁の表面に沿って形成された膜厚16nmのTaN0.87膜31と、TaN0.87膜上に形成され、配線溝16に埋め込み形成されたCuダマシン配線17に接する膜厚4nmのTaN1.19膜32とから構成されている。

(もっと読む)

21 - 37 / 37

[ Back to top ]