Fターム[5F033QQ08]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチングの対象 (10,331) | 導電膜 (3,144)

Fターム[5F033QQ08]に分類される特許

2,001 - 2,020 / 3,144

基板処理方法

【課題】パターン形成された基板に対し、基板上のパターンを損傷することなく、基板上のパーティクルを除去できる基板処理方法を提供する。

【解決手段】加圧された気体と薬液を混合し、ミストを形成する2流体ノズルを用いて、パターン形成された基板にミストを吐出する処理を行うことで、基板上のパーティクルを除去することができる。その基板処理において、基板上のパターンのアスペクト比に対応して、気体流量を変更して処理を行う。好適な処理条件の1つとして、Al配線パターンが形成された基板上において、アスペクト比2.2未満のパターンが形成された基板に対して、気体流量80L/minで処理を行う。アスペクト2.2以上のパターンが形成された基板に対して、気体流量60L/minで処理を行う。

(もっと読む)

成膜方法、成膜装置及び記憶媒体

【課題】バリヤ層や補助シード膜等の成膜プロセス条件を適切に選択して凹部の底部を削り取り、削り込み窪み部の底部の電気抵抗上昇の原因となる層を取り除きつつ側面や上面に薄膜を形成することが可能な成膜方法を提供する。

【解決手段】処理容器34内で金属ターゲット78をイオン化させて金属イオンを含む金属粒子を発生させ、載置台44上に載置した被処理体Wにバイアス電力により引き込んで表面に凹部5が形成されている被処理体の表面に薄膜を形成する成膜方法において、凹部の最下層の底部を削って削り込み窪み部12を形成しつつ凹部内の表面を含む被処理体の表面全体に第1の金属を含む薄膜よりなるバリヤ層10を形成するバリヤ層形成工程と、削り込み窪み部の底部を更に削って凹部内の表面を含む被処理体の表面に第2の金属を含む薄膜よりなるメッキ用の補助シード膜14Aを形成する補助シード膜形成工程とを有する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コンタクトプラグを高い歩留まりにて形成し、半導体記憶装置の製造過程における歩留まりを向上させる構造の半導体記憶装置及びその製造方法を提供する。

【解決手段】本発明の半導体記憶装置は、半導体基板と、半導体基板の表面に形成されたMOSトランジスタと、MOSトランジスタのゲート間に配置され、MOSトランジスタのソース及びドレインそれぞれに接続された多結晶シリコン膜のセルコンタクトプラグと、セルコンタクトプラグ上に設けられたパッド金属層と、パッド金属層上に設けられた層間絶縁膜と、層間絶縁膜上に設けられた記憶容量部と、層間絶縁膜を貫通する開口部に配置され、記憶容量部と前記パッド金属層を接続するコンタクトプラグとを有する。

(もっと読む)

エッチング用組成物及びエッチング方法

【課題】

従来のルテニウム用エッチング組成物では、強力な酸化剤が用いられていたため、ルテニウム以外の半導体材料のダメージがあった。

【解決手段】

(a)カルボン酸及び/又はアンモニア,(b)過酸化水素,(c)水を含んでなり、その水溶液が酸性であることを特徴とするルテニウムのエッチング用組成物を用いる。

カルボン酸の含有量が、0.01〜50重量%、アンモニアの含有量が、0.01〜20重量%、過酸化水素の含有量が、0.01〜35重量%、水の含有量が、50〜99.98重量%であることが好ましい。

(もっと読む)

半導体装置およびその製造方法

【課題】分離絶縁膜上の配線と、この配線の側面上に形成されたサイドウォールと、配線と活性領域上の不純物拡散とを接続するシェアードコンタクトを備えた半導体装置であっても、シェアードコンタクから半導体基板へのリーク電流の発生を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板100の主表面上に選択的に形成された分離絶縁膜と、半導体基板100の主表面上において、分離絶縁膜20Aにより規定される活性領域2cと、分離絶縁膜上にて、活性領域3bに達する凹部50と、凹部50を覆うように形成された第1絶縁膜10Aと、第1絶縁膜10A上に形成され、凹部50を充填し、第1絶縁膜10Aと材質の異なる第2絶縁膜10Bと、凹部50と隣り合う位置の活性領域2cの主表面上に形成された不純物拡散層2c1と、不純物拡散層2c1上に形成された導電膜とを備える。

(もっと読む)

基板と基板上の突起電極との間の応力低減

本発明は、基板及び突起電極を有する半導体部品に関するものである。突起電極は、基板に対面する基板面を有し、この基板面は、ギャップによって基板から分離された第1基板面部分を備えている。このギャップは、突起電極の基板に対する応力補償変形を可能にする。突起電極の基板面はさらに、基板に機械的に固定接続及び電気接続された第2基板面部分を備えている。突起電極と基板との機械接続のより小さいフットプリントにより、突起電極は、同量の応力を基板上またはアセンブリ内の外部基板に伝えることなしに、加えられた機械的応力に三次元的に追従することができる。このことは、半導体部品を突起電極によって外部基板に接続したアセンブリの改善された寿命を生じさせる。  (もっと読む)

(もっと読む)

寸法測定パターン、及びその形成方法

【課題】 半導体装置に使用される寸法は、ますます微細化されている。寸法が微細化され、導電膜配線のエッチング時における下地膜のエッチングにより、導電膜配線パターンの寸法測定が正確に行えないという問題がある。

【解決手段】本発明の寸法測定パターンは、導電膜配線の寸法測定点となる導電膜配線の両端部を含む領域における下地膜を、導電膜配線のエッチングガスに対しエッチングされない材料とする。そのため測長SEMにて観察した時の2次電子画像のコントラスト波形が配線幅にあたるピークのみを安定して得られ、正確に導電膜配線の寸法測定が実施できる。

(もっと読む)

半導体装置

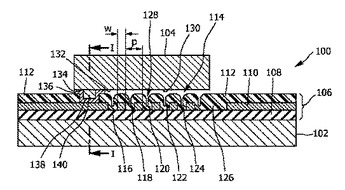

【課題】 本発明は、同一基板上に同時に異なるLDD構造を有する生産性の高いTFTの作製方法およびその構造を提供することを目的としている。即ち、本発明はTFTの新規な構造と生産性の高い製造工程を提供するものである。

【解決手段】 耐熱性の高いTa膜またはTaを主成分とする膜を配線材料に用い、さらに保護層で覆うことで、高温(400〜700℃)での加熱処理を施すことが可能となり、且つ保護層をエッチングストッパーとして用いることで周辺駆動回路部においては、サイドウォール126を用いた自己整合プロセス(セルフアライン)によるLDD構造を備えたTFTを配置する一方、画素マトリクス部においては、絶縁物125を用いた非自己整合プロセス(ノンセルフアライン)によるLDD構造を備えたTFTを配置する

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電流の局所集中による半導体基板への部分放電を抑制し得る半導体装置を提供する。

【解決手段】半導体装置は、半導体基板(1,5)と、半導体基板(1,5)に埋め込まれたゲート電極(9A,9B)と、ゲート電極(9A,9B)の更に内側に埋め込まれた導電体(15A,15B)と、導電体(15A,15B)と接続されるように半導体基板(1,5)の内部に形成された配線層(3)と、ゲート電極(9A,9B)と導電体(15A,15B)との間に配置された絶縁膜(14)とを備える。導電体(15A,15B)は、半導体基板(1,5)の表面よりも高くなるように形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】フルシリサイド化されたゲート電極を有する半導体装置の製造方法において、活性領域と素子分離領域との段差による影響を受けることなく、活性領域上と素子分離領域上とに形成されたそれぞれのゲート電極形成膜及びゲート配線形成膜の露出を精度良う。

【解決手段】活性領域11を囲む素子分離領域12が形成された半導体基板10の上に形成された保護膜15a及び保護膜15bを覆うように下地保護膜19及び層間絶縁膜20を形成した後、化学機械研磨(CMP)法により、保護膜15aの上面が露出するまで、層間絶縁膜20、下地保護膜19及び保護膜15bを研磨除去する。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。また、それらの表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】導電層を形成する際、形成したいパターンの外側(パターンの輪郭、端部に相当する)に液状の導電性材料を含む組成物を付着させ、枠状の第1の導電層(又は絶縁層)を形成する。枠状の第1の導電層の内側の空間を充填するように、液状の第2の導電性材料を含む組成物を付着させ第2の導電層を形成する。第1の導電層及び第2の導電層は接して形成され、第2の導電層の周囲を囲むように第1の導電層が形成されるので、第1の導電層及び第2の導電層は連続した一つの導電層として用いることができる。

(もっと読む)

半導体装置

【課題】本発明は、COP構造を採用することなしにセル面積の縮小と強誘電体キャパシタ面積の増加を実現することを最も主要な特徴とする。

【解決手段】基板51と、拡散領域54Aと、その上に形成された層間絶縁膜55と、層間絶縁膜55に形成され、拡散領域54Aに通じるホール57A及び57Bと、ホール57A及び57B内に形成され、拡散領域54Aと電気的に接続された下部電極59と、下部電極59上に形成された強誘電体膜60と、強誘電体膜60上に形成された上部電極61とを有し、下部電極59、強誘電体膜60及び上部電極60でそれぞれ強誘電体キャパシタが構成されている。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。また、それらの表示装置を構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】マスク層を形成する際、形成したいパターンの外側(パターンの輪郭、端部に相当する)に液状のマスク層形成材料を含む組成物を付着させ、枠状の第1のマスク層を形成する。枠状の第1のマスク層の内側の空間を充填するように、液状の第2のマスク層形成材料を含む組成物を付着させ第2のマスク層を形成する。第1のマスク層及び第2のマスク層は接して形成され、第2のマスク層の周囲を囲むように第1のマスク層が形成されるので、第1のマスク層及び第2のマスク層は連続した一つのマスク層として用いることができる。

(もっと読む)

半導体装置及びその製造方法

【課題】生産効率が高く、信頼性及び歩留まりの高い半導体装置の製造方法を提供する。

【解決手段】半導体基板1の裏面研削(バックグラインド)を行い、半導体基板1を薄くする。次に、裏面研削で生じたダメージ層7の除去をこの段階では行わずに、レジスト層8を半導体基板の裏面に選択的に形成する。次に、レジスト層8をマスクとして半導体基板1をエッチングし、ビアホール9を形成する。次に、当該エッチング工程で利用したエッチング装置内に半導体基板1を配置したまま、ビアホール9形成と連続的にレジスト層8を除去する。このように、エッチング工程とその後のアッシング工程とを一つの処理装置で連続的に行う。次に、半導体基板1の裏面のダメージ層7の除去及び、ビアホール9の内壁面の平坦化工程についても、上記アッシング工程と同一装置で連続的に行う。

(もっと読む)

液晶表示装置の製造方法

【課題】半導体層及び高融点金属膜とAlまたはAl合金からなる低抵抗金属膜との積層

金属膜をパターン形成するに当たり、工程を複雑化することなく、AlまたはAl合金の

耐腐食性を改善する。

【解決手段】Al(合金)と高融点金属の積層膜パターン24、25をエッチングマスク

であるフォトレジスト51から後退して形成し、この状態でAl(合金)膜の側面に保護

膜38を形成する。このため、半導体層23のエッチングやチャネルエッチング時にAl

(合金)膜の側面が塩素系ガスやフッ素系ガスのプラズマに曝されにくくなり、Al(合

金)膜の腐食を抑制することができる。

(もっと読む)

アクティブ型液晶表示パネル

【課題】アクティブ型液晶表示パネルにおいて、薄膜トランジスタのソース電極形成用のCr膜のサイドエッチング量を低減する。

【解決手段】Cr膜11SおよびAl系金属膜12Sからなるソース電極17は、画素電極9の図1の下辺部のほぼ全体の上面およびその近傍におけるゲート絶縁膜5の上面に形成されている。すると、Cr膜11Sの平面の面積が大きくなり、ひいてはCr膜11Sの周囲面の面積(周囲長×膜厚)も大きくなる。そして、このCr膜11Sの周囲面の面積の増大により、Cr膜11Sのサイドエッチング量を低減することができる。

(もっと読む)

半導体装置の側壁修復方法および半導体装置

【課題】絶縁膜上に接触して形成された層の側壁を選択的に修復できるようにする。

【解決手段】第1の導電層6の側壁をエッチング処理や当該処理時の反応生成物の除去処理等により除去することで第1の導電層6の下部のY方向の幅がその上部のY方向の幅よりも狭く形成される。その後、除去された領域に対して選択成長技術により外壁部6bを形成する。

(もっと読む)

表示装置の製造方法

【課題】表示品質の優れた表示装置を生産性よく製造することができる表示装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る表示装置の製造方法は、TFT108を備える基板100を有する表示装置に関する方法である。まず、TFT108を備える基板100上にスルーホール11を有する平坦化膜10を成膜する。次に、スルーホール11を介してTFT108のドレイン部と接続され、画素電極の少なくとも一部となる透明導電膜12を成膜する。そして、透明導電膜12を成膜後、TFT108を備える基板100に対してプラズマによる第1の表面処理を行う。さらに、プラズマによる第1の表面処理後、反射膜13を成膜する。

(もっと読む)

半導体装置及びその製造方法

【課題】リソグラフィの解像限界以下の配線パターンと、それ以外の任意の寸法の配線パターン等を簡易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】被エッチング部材であるポリシリコン膜25上に第1ハードマスク30が形成され、更にこの上にアモルファスシリコンからなる第2ハードマスク40が形成される。第2ハードマスク40の所望の一部にボロン等のイオン注入を行った後、第2ハードマスク40をマスクとして第1ハードマスク30をエッチングする。ウエットエッチングにより第2ハードマスク40のイオン注入されていない部分をエッチング除去する。第1ハードマスク30の側壁に側壁膜70を形成した後、第2ハードマスク40に覆われず上部が露出している第1ハードマスク30を選択的にエッチング除去する。

(もっと読む)

半導体装置、その製造方法および検査方法

【課題】外部接続端子を有する半導体装置に、電気特性試験とバーンイン試験と外部接続端子の形成とをウェハ状態で一括して、かつ各部に損傷を与えることなく行うことが出来る電極構造を具備させる。

【解決手段】半導体基板1の電極パッド2上に形成する突起電極4を、上面中央部に位置する第1の平坦領域14aと、それを囲んで上面外周部近傍に位置する第2の平坦領域14bと、両領域14a,14bの間の第1の凸領域14cとを有する構造とする。これにより、凹凸形状の突起電極4上で電気特性検査を行うことで電極パッド2下へのダメージを避けることができる。電気特性検査によって不良と判定された半導体装置を共通配線から電気的に切り離す際に第1の平坦領域14aのみに不導体被膜6を形成することができ、バーンイン試験および外部接続端子の形成を確実に安定して行うことが可能となる。

(もっと読む)

2,001 - 2,020 / 3,144

[ Back to top ]