Fターム[5F033QQ16]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | 異方性エッチング (964)

Fターム[5F033QQ16]の下位に属するFターム

斜めエッチング (8)

Fターム[5F033QQ16]に分類される特許

201 - 220 / 956

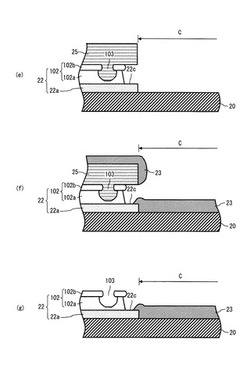

パターン形成方法、及び半導体装置の製造方法

【課題】下地の性能を犠牲にすることなく、リフトオフ層が下地から剥離することを防止できるパターン形成方法、及び半導体装置の製造方法を提供すること。

【解決手段】本発明にかかるパターン形成方法は、基板上にカバー絶縁膜22を形成し、第1のレジストパターン104をマスクとして、金属膜パターン形成領域を取り囲むようカバー絶縁膜22に凹部103を形成する工程と、凹部103内に入り込むよう、カバー絶縁膜22上にリフトオフ層となる第2のレジストパターン25を形成する工程と、第2のレジストパターン25をマスクとして、金属膜パターン形成領域のカバー絶縁膜22に開口部を形成する工程と、第2のレジストパターン25の上から基板表面に金属膜を成膜し、第2のレジストパターン25とともに第2のレジストパターン25上の金属膜を除去して金属膜パターンを形成する工程とを備えるものである。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】ダマシン配線形成時に、シード膜を配線用溝の側壁に確実に形成する。

【解決手段】下地絶縁膜1の上にプラズマシリコン窒化膜2、プラズマTEOS酸化膜3を形成する。プラズマTEOS酸化膜3は、高周波電源および低周波電源を用いる2周波励起プラズマCVD装置により、膜密度が上部に行くほど小さくなるように形成される。配線用溝をRIE法により形成した後、ウェットエッチングで膜密度が小さい部分を速くエッチングすることでテーパ形状の配線用溝3aを形成する。スパッタでバリアメタル膜4を形成する際に配線用溝3aの側壁にも確実に形成でき、銅膜5のメッキをボイドなしに形成できる。

(もっと読む)

導体トラック配列の製造方法

【課題】従来例に比べて結合容量が低下し、さらに機械的または電気的特性を向上させた導体トラック間のエアギャップの製造方法を提供する。

【解決手段】基材1、2と、少なくとも2つの導体トラック4と、空洞6と、導体トラック4を覆い、空洞6を塞ぐレジスト層5とを含む、導体トラック配列とする。導体トラック4の幅B1よりも小さい幅B2のキャリアトラックTBを形成することにより、結合容量と信号遅延を低減するためのエアギャップが、導体トラック4の下にその側面に沿ってセルフアライン技術により形成される。

(もっと読む)

半導体素子の製造方法

【課題】簡単な工程設備を用いて短い工程時間内に半導体素子のビアを形成できる半導体素子の製造方法を提供すること。

【解決手段】基板101に絶縁膜107と拡散防止膜109で内壁を被覆したビアホール105を形成する。荷電された金属粒子113を、電気力又は磁気力を利用して移動させて、このホールを金属粒子で充填する。ビアホールの下部から上方へ充填されるので、内部に空隙が発生することを抑制できる。従来技術による銅電気メッキ方式と比較すると、非常に短時間内に大きくて深いビアホールを金属粒子で充填できるため、シリコン貫通ビア(TSV)の工程コスト、及び工程時間を短縮することが出来る。また、従来技術の樹脂成分が多く含まれているメタルペーストを用いる乾式充填方式と比較すると、荷電された金属粒子を用いることで、より密なTSV金属配線を形成できる。

(もっと読む)

配線基板及び配線基板の製造方法

【課題】 貫通電極と配線層との間における電気抵抗の増加を抑制できる配線基板及び半導体装置を提供する。

【解決手段】 半導体基板と、半導体基板の少なくとも上面に形成され、導体層及び第1絶縁層を有する配線層と、半導体基板及び配線層の第1絶縁層を貫通する貫通電極と、半導体基板と貫通電極との間に形成された第2絶縁層と、を備える配線基板であって、貫通電極は、配線層の第1絶縁層を貫通する第1導電部と、半導体基板を貫通し、第1導電部と電気的に接続し、第1導電部の断面積よりも大きい断面積を有し、且つ導体層と電気的に接続する段差面を含む第2導電部と、を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】設計基準を遵守しつつ容量値を向上しうる容量素子を有する半導体装置及びその製造方法を提供する。

【解決手段】複数の電極パターンをそれぞれ有し、積み重ねるように配置された複数の配線層と、複数の配線層の間にそれぞれ設けられ、隣接する配線層の複数の電極パターンのそれぞれを電気的に接続する複数のビア部と、複数の配線層及び複数のビア部の間隙に形成された絶縁膜とを有する容量素子を有し、ビア部は、電極パターンの中心に対して、電極パターンの延在方向と交差する方向にずらして配置されており、電極パターンは、ビア部が接続された部分において線幅が太くなっており、隣接する電極パターンとの間の間隔が狭まっている。

(もっと読む)

半導体装置及びその製造方法

【課題】温度変化に起因したパッシベーションクラックを適切に防止することができる半導体装置の提供。

【解決手段】本発明による半導体装置1は、絶縁膜11と、絶縁膜11上に形成されるバリア層16と、バリア層16上に配されるアルミ配線12と、アルミ配線12の上部に設けられるキャップメタル18又は防腐処理部21と、アルミ配線12の側部に設けられるサイドウォール17と、を備えることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラートランジスタにおいて、ゲートコンタクトとシリコン基板との間のショートを抑制した半導体装置及びその製造方法を得るという課題があった。

【解決手段】半導体からなる基板1と、一面1aから突出され、前記半導体からなる第1の突出部2と、一面1aに設けられた溝部1cに充填された第1の絶縁体3と、第1の突出部2に隣接して一面3aから突出され、第1の絶縁体3からなる第2の突出部4と、第1の突出部2の側面を覆うゲート絶縁膜5と、ゲート絶縁膜5を覆うゲート電極6と、第1の突出部2に設けられた上部拡散層13と、下部拡散層14と、第2の突出部4の側面を覆うとともにゲート電極6に接続された連結電極60と、第1の突出部2及び第2の突出部4を覆う層間絶縁膜と、前記層間絶縁膜を貫通して連結電極60に接するゲートコンタクト10と、を有する半導体装置及びその製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置およびその製造方法

【課題】MRAMを含む半導体装置において、MRAMの特性を向上することができる技術を提供する。

【解決手段】配線L3およびデジット配線DLを形成した層間絶縁膜IL3の表面に対してプラズマ処理を実施する。まず、半導体基板1Sをチャンバ内に搬入し、窒素を含有する分子(アンモニアガス)と窒素を含有しない不活性分子(水素ガス、ヘリウム、アルゴン)とからなる混合ガスをチャンバ内に導入する。このとき、窒素を含有する分子の流量よりも窒素を含有しない不活性分子の流量が多い条件で、混合ガスを導入し、混合ガスをプラズマ化してプラズマ処理を実施する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】縦型MOSトランジスタを備えた半導体装置を形成する際のゲート電極とコンタクトプラグとの短絡を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、前記半導体基板上にシリコン窒化膜(SiN膜)からなるマスク窒化膜のパターンを形成したのちに、溝および半導体ピラーを前記半導体基板に形成する第一工程と、前記マスク窒化膜を残存させたまま、前記溝を覆うゲート絶縁膜を形成したのちに前記半導体ピラーよりも低い高さのゲート電極を形成する第二工程と、前記溝を覆うように、シリコン酸窒化膜(SiON膜)からなるライナー膜を形成したのちに、前記ライナー膜上を覆い、かつ、前記溝内を充填するように層間膜(SOD膜)を形成する第三工程と、前記マスク窒化膜をエッチングにより選択的に除去する第四工程と、を採用する。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極およびこれと一体的に形成された裏面電極を有する半導体装置において、貫通電極の膜厚と裏面電極の膜厚とを独立に制御することにより、貫通電極の剥離の問題と裏面配線の剥離の問題を同時に解消することができる半導体装置およびその製造方法を提供する。

【解決手段】半導体基板10と、半導体基板の上方に形成された少なくとも1層からなる配線層13と、半導体基板の裏面から配線に達する貫通電極30と、半導体基板の裏面に設けられて貫通電極に接続された裏面配線40と、裏面配線に接続された外部端子50と、を含む半導体装置であり、裏面配線は、少なくとも外部端子との接続部を含む部分の膜厚が、貫通電極の膜厚よりも厚く形成されている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】 デュアルダマシン法を用いて銅の埋め込み配線および接続プラグを形成するとき、接続プラグ中のボイド発生を防止する。

【解決手段】 Low−k膜13、15、ELK膜14、TEOS膜16からなる層間絶縁膜にプラグとなる接続孔19aを形成した後、酸素プラズマ処理を行って変質層20を形成し、この層を薬液処理により選択的に除去すると、ELK膜14が多孔質であることに起因してその側壁21にLow−k膜13、15などより大きい角度のテーパーが形成される。次に配線埋め込み用の溝の底面がELK膜14中にくるように形成して、プラグ開口の入口が広がる形状にした後、銅膜を埋め込む。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置の製造方法を提供することにある。

【解決手段】側壁にサイドウォール絶縁膜が形成されたゲート配線20を形成する工程と、第1の応力膜38を形成する工程と、第1の応力膜上にエッチングストッパ膜40を形成する工程と、エッチングストッパ膜をエッチングし、第1の応力膜のうちのサイドウォール絶縁膜を覆う部分上にエッチングストッパ膜を選択的に残存させる工程と、第2の領域4を露出する第1のマスクを用いて第2の領域内の第1の応力膜をエッチングする工程と、第2の応力膜42を形成する工程と、第1の領域2を露出する第2のマスクを用いて第1の領域内の第2の応力膜をエッチングする工程と、第1の領域と第2の領域との境界部におけるゲート配線に達するコンタクトホール46aを形成する工程とを有している。

(もっと読む)

3次元半導体メモリ装置及びその製造方法

【課題】3次元半導体メモリ装置及びその製造方法を提供する。

【解決手段】本装置は、積層された導電パターン、導電パターンを貫通する活性パターン及び導電パターンと活性パターンとの間に介在される情報貯蔵膜を含む少なくとも1つのメモリ構造体を含み、活性パターンは積層された下部及び上部貫通ホールを各々満たす下部及び上部半導体パターンを含むことができる。1つのメモリ構造体を構成する情報貯蔵膜は同一の工程段階を利用して実質的に同時に形成され、1つのメモリ構造体を構成する下部及び上部貫通ホールは互いに異なる工程段階を利用して順に形成され得る。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置における被研磨面の平坦性を向上させる。

【解決手段】凸状パターンが形成された下地の上に埋め込み層を形成して前記凸状パターンを埋め込む工程と、前記凸状パターンの上の前記埋め込み層に異方性エッチングを施して、前記凸状パターンの上の前記埋め込み層に凹部を形成する工程と、前記絶縁膜の表面を化学機械研磨により研磨する工程と、を備えたことを特徴とする半導体装置の製造方法が提供される。

(もっと読む)

半導体装置のパターン構造物及び半導体装置のパターン構造物の形成方法

【課題】半導体装置のパターン構造物及び半導体装置のパターン構造物の形成方法を提供すること。

【解決手段】半導体装置のパターン構造物は、延長ラインと延長ラインの端部に連結されるパッドとを具備する。パッドは、延長ラインの幅より広い幅を有することができる。パッドは、パッドの側部から延長する突出部を含むことができる。パターン構造物は、単純化された工程を通じて製造されることができ、微細パターンとパッドを含む多様な半導体装置に適用することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】深さの異なる複数のコンタクトホールの底部径のばらつきを抑制する半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置は、複数の導電層WL1〜WL4が階段状に加工された階段構造部を有する積層体と、階段構造部を覆って設けられた層間絶縁層43と、層間絶縁層43を貫通し、それぞれが対応する各段の導電層WL1〜WL4に達して形成された複数のコンタクトホール61〜64の内部に設けられたコンタクト電極60とを備え、複数のコンタクトホール61〜64の底部の孔径は略同じであり、下段側の導電層に達するコンタクトホールは、上段側の導電層に達するコンタクトホールよりも深く、上端部の孔径が大きい。

(もっと読む)

配線パターン形成方法および半導体装置の製造方法、半導体装置、データ処理システム

【課題】2回のリソグラフィ工程によるSADP法(Self Align Double Patterning)を用いて、第1配線パターン形成領域には解像限界未満のパターンを含む第1配線パターンを形成し、第2配線パターン形成領域には解像限界以上の通常パターンからなる第2配線パターンを簡便に形成する方法を提供する。

【解決手段】解像限界未満の寸法を有する複数の配線を含む第1配線パターンを、第1リソグラフィ工程と第1リソグラフィ工程の後に実施される第2リソグラフィ工程を用いて形成し、第1のリソグラフィ工程で形成されたパターンに対してのみサイドウォールの形成および除去処理を行い、その後、解像限界以上のパターンを生成する第2リソグラフィ工程を実施する。第2のリソグラフィ工程で形成される解像限界以上の通常パターンに対しては、単純なリソグラフィ工程とすることが可能となる。

(もっと読む)

半導体素子及びその形成方法

【課題】半導体素子及びその形成方法を提供する。

【解決手段】本発明の半導体素子の形成方法は、基板上に半導体構造物及び絶縁パターンを形成し、絶縁パターンの一面によって定義される側壁と半導体構造物の底によって定義される底を有するオープニングを形成し、オープニングを満たす第1金属膜を形成し、第1金属膜を湿式エッチングしてオープニングの側壁を少なくとも一部露出させ、第1金属膜上に第2金属膜を選択的に形成することを含む。

(もっと読む)

201 - 220 / 956

[ Back to top ]