Fターム[5F033QQ16]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ドライエッチング (6,179) | 異方性エッチング (964)

Fターム[5F033QQ16]の下位に属するFターム

斜めエッチング (8)

Fターム[5F033QQ16]に分類される特許

941 - 956 / 956

ビット線構造およびその製造方法

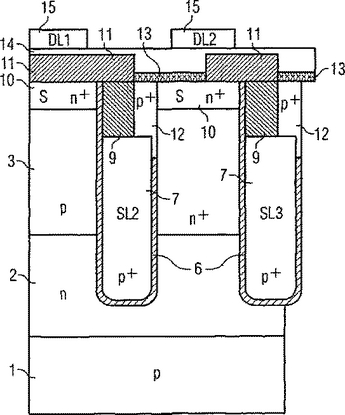

本発明は、表面ビット線(DLx)および埋め込みビット線(SLx)を備えたビット線構造に関するものである。これに関して、埋め込みビット線(SLx)は、トレンチ絶縁層(6)を備えたトレンチに形成されており、トレンチの上部に設けられた被覆接続層(12)と自動調心電極層(13)とを介して形成された接触部とともに、ドープ領域(10)に接続されている。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

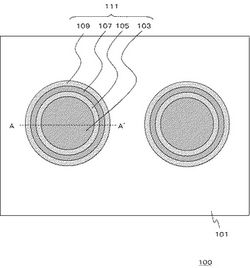

【課題】 貫通電極を有する半導体装置において、少ない面積で高密度に貫通電極を設ける。

【解決手段】 半導体装置100において、シリコン基板101を貫通する孔に充填された多重貫通プラグ111を設ける。多重貫通プラグ111は、円柱状で中実の第一の貫通電極103、第一の貫通電極103の円筒面を覆う第一の絶縁膜105、第一の絶縁膜105の円筒面を覆う第二の貫通電極107、および第二の貫通電極107の円筒面を覆う第二の絶縁膜109からなり、これらは同じ中心軸を有する。また、第一の絶縁膜105、第二の貫通電極107および第二の絶縁膜109の上断面は円環状とする。

(もっと読む)

線幅の狭い半導体素子の製造方法

【課題】セルの周辺領域における線状パターンのCDを減少させることができる半導体素子の製造方法を提供する。

【解決手段】セル領域及び周辺領域が画定された基板200上にシリコン窒化膜201Aを形成する工程、シリコン窒化膜上に反射防止膜としてシリコン酸窒化膜202Aを形成する工程、セル領域では最終パターンの線幅W1Aより広い幅W1を有し、周辺領域ではパターンの崩れの発生を抑える最小の線幅W2を有するようにシリコン酸窒化膜上にフォトレジストパターン203を形成する工程、フォトレジストパターンをエッチングマスクとしてシリコン酸窒化膜とシリコン窒化膜とをエッチングする処理を、残留するシリコン酸窒化膜202Bとシリコン窒化膜201Bとの線幅W1A,W2Bがフォトレジストパターンの線幅W1,W2に比べて狭くなるまで行う工程、及び残留するシリコン窒化膜を過度エッチングする工程を含む。

(もっと読む)

半導体装置の製造方法

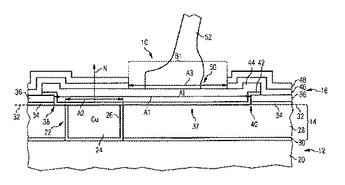

【課題】半導体装置の製造方法において、ネガレジスト層及び配線層のパターニング工程における信頼性の向上を図る。

【解決手段】 半導体基板10の裏面に開口部10wを形成した後、それらの上に配線層18及び第3のレジスト層19を形成する。次に、開口部10wの底部のダイシングラインDLの上方にマスク20を配置する。次に、開口部10wの側壁から当該底部に反射する光がマスク20に対応する第3のレジスト層19を固着させない光エネルギーを以って、第3のレジスト層19を露光する。次に、現像によりマスク20に対応する第3のレジスト層19を除去する。次に、第3のレジスト層19の全面を再び露光する。この第3のレジスト層19をマスクとして配線層18のエッチングを行う。最後に、ダイシングラインDLに沿って、半導体基板10を複数の半導体チップにダイシングする。

(もっと読む)

半導体装置の配線構造体及びその形成方法

【課題】 半導体装置の配線構造体およびその形成方法を提供する。

【解決手段】 この半導体装置は半導体基板100上に配置された層間絶縁膜、前記層間絶縁膜を貫通する第1コンタクト構造体181および第2コンタクト構造体182、前記層間絶縁膜上に配置されて前記第1コンタクト構造体と前記第2コンタクト構造体に連結される金属配線220を具備する。この際、前記第1コンタクト構造体は順次に積層された第1プラグおよび第2プラグ200を含み、前記第2コンタクト構造体は前記第2プラグを含む。

(もっと読む)

半導体装置の製造方法

【課題】 工程を大幅に増加させずに導電層を形成しやすい形状のコンタクトホールの形成、特にウェットエッチング後にドライエッチングをより確実に行うことによってコンタクトホールの形状不良を低減することができる半導体装置の製造方法を提供する。

【解決手段】 シリコン基板1上に形成されている層間絶縁膜2上に第1マスク3を形成する第1マスク形成工程と、層間絶縁膜2の途中までエッチングして第1凹部4aを形成する第1エッチング工程と、第1マスク3を除去する第1マスク除去工程と、第1エッチング工程により形成された第1凹部4a内に開口部を有するように第2マスク5を形成する第2マスク形成工程と、層間絶縁膜をシリコン基板1の表面に達するまでエッチングしてコンタクトホール4を形成する第2エッチング工程と、第2マスク5を除去する第2マスク除去工程とを有する。

(もっと読む)

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

下にあるバリア層への多孔性低誘電率膜の接着を促進する手法

下にあるバリア層に対する多孔性低誘電率膜の接着は、その上にある多孔性低誘電率膜より炭素含量が低く、シリコン酸化物が豊富な中間層を形成することにより向上する。この接着層は、多数の手法のうち一つを単独で又は組み合わせて利用して形成されてもよい。一つのアプローチでは、接着層は、低誘電率材料の堆積直前にO2/CO2/などの濃酸化ガスを導入してSi前駆体を酸化することにより形成することができる。別のアプローチでは、α−テルピネン、シメン及びその他の酸素非含有有機物などの熱的に不安定な化学物質が、低誘電率膜の堆積前に除去される。また別のアプローチでは、ハードウェア又はシリコン非含有成分を導入する方式などの処理パラメータが変更されて、低誘電率膜の堆積の前に酸化物界面の形成を可能とすることもできる。さらに別のアプローチでは、吸収量、エネルギー又は熱アニール処理の使用などの電子ビーム処理のパラメータが制御され、バリアと低誘電率膜との間の界面で炭素種を除去することもできる。さらなるアプローチでは、低誘電率堆積の前に前処理プラズマが導入されバリア界面の加熱を増進することにより、低誘電率堆積ガスが導入され、低誘電率膜が堆積される時、薄い酸化物界面を形成することもできる。 (もっと読む)

サイドウォールスペーサの形成方法

本発明により、基板(201)上のフィーチャ(206)に隣接するサイドウォールスペーサ(217、218)を形成することができる。フィーチャ(206)は1つ以上の保護層(220、207)に覆われる。スペーサ材料層(211)はフィーチャ(206)上に蒸着され、異方性エッチングされる。異方性エッチングに使用されるエッチング液はスペーサ材料を選択的に除去することに適しており、一方で1つ以上の保護層(220、207)はこのエッチング液による影響を実質的に受けない。その結果、1つ以上の層(220、207)はフィーチャがエッチング液にさらされるのを保護する。  (もっと読む)

(もっと読む)

マスキング方法

本発明はマスキング方法を包含する。1つの実施において、ホウ素ドープアモルファスカーボンを含むマスキング材料が、半導体基板上に形成されたフィーチャーを覆って形成される。マスキング材料は少なくとも約0.5原子パーセントのホウ素を含む。マスキング材料は実質的に異方的にエッチングされ、ここでそのエッチングはホウ素ドープアモルファスカーボンを含む異方的にエッチングされたサイドウォールスペーサをフィーチャーのサイドウォール上に形成するのに有効である。次に、スペーサに最も近い基板が、ホウ素ドープアモルファスカーボンを含むスペーサをマスクとして用いながら加工される。スペーサに最も近い基板を加工した後、ホウ素ドープアモルファスカーボンを含むスペーサが基板からエッチングされる。他の実施および面も考えられる。 (もっと読む)

集積接続部およびその製造方法

本発明は、電気的に導電性ではない絶縁層(34,36)における切り欠き部(37)に、少なくとも部分的または全体的に配置された外部導電構造部(44)を有する接続部に関する。切り欠き部(37)の底部には、導電性の内部導電構造部(22)が、絶縁層(34,36)の一方側に配置され、コンタクト領域において外部導電構造部と境界を形成している。コンタクト面は、切り欠き部(37)の他方側において、外部導電構造部(44)に配置されている。コンタクト領域とコンタクト面とは、互いに重ならないか、部分的にのみ重なっている。切り欠き部(37)の底部は、法線方向から見ると、コンタクト面の少なくとも半分または全面に重なるように配置されている。その結果、絶縁層(34、36)の段状部分は、コンタクト面と内部導電構造部(22)との間に延びる主要電流路の外側において、切り欠き部(37)の端部に位置する。  (もっと読む)

(もっと読む)

多層配線構造部及びその製造方法

【課題】配線容量を低減した多層配線構造部。

【解決手段】下地11と、下地11上に設けられている第1の配線層12と、下地11上に第1の配線層12を被覆するように設けられていて、互いに隣接する第1の配線層12間に凹部22bを有するライナー絶縁膜22と、凹部22bに設けられている埋込み絶縁膜24と、埋込み絶縁膜24を被覆しているキャップ絶縁膜26と、キャップ絶縁膜26上に設けられている第2の配線層14とを具えていて、埋込み絶縁膜24は、ライナー絶縁膜22及びキャップ絶縁膜26よりも低い誘電率を有する絶縁性材料から構成されている。

(もっと読む)

半導体集積回路装置の製造方法

【課題】 アルミニウムを主成分とする導体膜パターンを有する半導体集積回路装置の信頼性を向上させる。

【解決手段】 アルミニウムを主成分とする導体膜16dを有する第1層配線L1をドライエッチング法によってパターニングした後、その加工側壁の側壁保護膜18およびエッチングマスクとして使用したフォトレジストパターン17aをプラズマアッシング処理によって除去する。続いて、絶縁膜15bおよび第1層配線L1の表面に付着した塩素成分を、酸素ガスとメタノールガスとの混合ガスを用いたプラズマアッシング処理によって除去する。この際、フォトレジストパターン17a等のアッシング除去処理時は、ウエハの主面温度が相対的に低くなるようにし、塩素成分の除去処理時は、ウエハの主面温度が相対的に高くなるようにする。また、それらのプラズマアッシング処理を別々の処理室で行う。

(もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

多層配線構造及びその製造方法

【課題】 多層配線構造において、エレクトロマイグレーション耐性の向上及びより一層の微細化を図る。

【解決手段】 下層配線Aは、第1のチタニウム膜102、第1の窒化チタン膜103、第1のAl−Cu膜104、第2のチタニウム膜105及び第2の窒化チタン膜106からなる。ヴィアコンタクトBは、第1の密着層109(チタニウム膜)、第2の密着層110(窒化チタン膜)及びタングステンプラグ111(タングステン膜)からなる。第2のチタニウム膜105及び第2の窒化チタン膜106には、ヴィアコンタクトBの平面形状よりも小さい開口部が形成され、ヴィアコンタクトBは開口部において第1のAl−Cu膜104と接続している。第1及び第2の密着層109、110は、側壁部の下端から内側に張り出す張り出し部において、第2の窒化チタン膜106における開口部の周辺領域と接続している。

(もっと読む)

多層スピンオン多孔性誘電体からなるlow−k配線構造

【課題】その中にマイクロトレンチを含まない低誘電体層間絶縁膜金属導体配線構造およびそのような構造の形成方法を提供する。

【解決手段】導体抵抗に対する制御は、第1の原子組成を有する多孔性の低誘電体層間絶縁膜の線とバイア誘電体層との間に位置する第2の原子組成を有する埋込みエッチング停止層により行われる。本発明の配線構造は、また、二重波形模様タイプの配線構造を形成する際に助けになるハードマスクを含む。第1および第2の組成は、エッチング選択性が少なくとも10:1またはそれ以上になるように選択され、特定の原子組成および他の発見できる量を有する多孔性の低誘電体層間絶縁膜有機材料または無機材料の特定のグルーブから選択される。

(もっと読む)

941 - 956 / 956

[ Back to top ]