Fターム[5F033QQ19]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ウェットエッチング (1,982)

Fターム[5F033QQ19]の下位に属するFターム

エッチング液 (265)

Fターム[5F033QQ19]に分類される特許

201 - 220 / 1,717

パターン化金属膜及びその形成方法

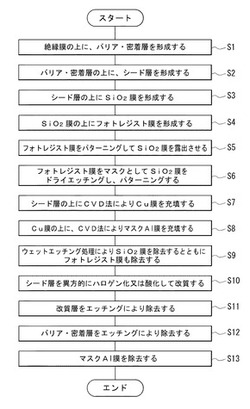

【課題】ドライエッチングが困難な遷移金属の膜を、サイドエッチングが極力生じないようにパターニングする。

【解決手段】絶縁膜の上にバリア層・密着層を形成し(S1)、その上に遷移金属からなるシード層を形成する(S2)。シード層の上にSiO2膜及びフォトレジスト膜を順次形成し(S3、S4)、フォトレジスト膜、SiO2膜をパターニングして開口を形成し(S5,S6)、開口内にCu膜及びマスクAl膜を積層する(S7、S8)。次に、SiO2膜をエッチング(S9)、露出したシード層をその膜厚方向に異方的に改質し(S10)、改質されたシード層、露出したバリア・密着層、及びマスクAl膜を順次エッチングにより除去することにより(S10〜S13)、パターン化金属膜を得る。

(もっと読む)

表示装置用金属配線膜

【課題】Si半導体層および/または透明導電膜との間のバリアメタル層を省略しても、低抵抗のオーミック特性を有する電気的接触を確保でき、更に十分な耐熱性を有する表示装置用金属配線膜を提供する。

【解決手段】Moを20原子%以上含有しており、且つ、Si、Nd、Ni、Mn、Mg、Fe、及びZnよりなる群から選択される少なくとも一種を5原子%以上含有しているAl合金膜53と、純CuまたはCu合金膜28,29とからなる積層膜であって、前記Al合金膜が、半導体層33と直接接続していると共に、前記CuまたはCu合金膜が透明導電膜55と直接接続している表示装置用金属配線膜。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】周辺回路における回路動作の遅延を低減できる不揮発性半導体記憶装置を提供する。

【解決手段】半導体基板11上に所定間隔を空けて形成され、ゲート絶縁膜1、浮遊ゲート電極2、ゲート間絶縁膜3、及び制御ゲート電極4をそれぞれ有する複数のメモリセルMCと、メモリセルMCの浮遊ゲート電極2の側面、ゲート間絶縁膜3の側面、及び制御ゲート電極4の側面に形成され、空隙を有する側壁絶縁膜18Bと、基板11上に形成され、ゲート絶縁膜1、第1ゲート電極2、ゲート間絶縁膜3、及び制御ゲート電極4を有する周辺トランジスタPTと、周辺トランジスタPTの第1ゲート電極2の側面、ゲート間絶縁膜3の側面、及び制御ゲート電極4の側面に形成され、空隙19Aを有する側壁絶縁膜18Aとを備える。基板11上の最も低い位置にある空隙19Aの上端は、ゲート間絶縁膜3より基板11上の低い位置にある。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】レンチ2内に埋め込まれた埋め込み絶縁膜3の一部を除去することで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1を形成し、空隙AG1は、制御ゲート電極8下に潜るようにしてトレンチ2に沿って連続して形成する。

(もっと読む)

不揮発性半導体記憶装置および不揮発性半導体記憶装置の製造方法

【課題】隣接する浮遊ゲート電極間の間隔を増大させることなく、隣接する浮遊ゲート電極間の寄生容量を低減する。

【解決手段】トレンチ2内に埋め込まれた第2の埋め込み絶縁膜4の一部が除去されることで、ワード線方向DWに隣接する浮遊ゲート電極6間に空隙AG1が形成され、浮遊ゲート電極6間が完全に埋め込まれないようにして制御ゲート電極8間にカバー絶縁膜10が掛け渡されることで、ビット線方向にDBに隣接する浮遊ゲート電極6間に空隙AG2が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート電極の幅を十分に確保して、ゲート電極の抵抗値を小さくすることが可能で、かつゲート電極間の容量を小さくすることの可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板に設けられ、Y方向に延在する第1の溝15と、半導体基板に設けられ、第1の溝15と交差するXの方向に延在する第2の溝25と、第1及び第2の溝15,25に囲まれ、第2の溝25に露出された対向する第1及び第2の側面26a,26bを有するピラー26と、ゲート絶縁膜28を介して、ピラー26の第2の側面26bに接触するように、第2の溝25の下部に設けられた1つのゲート電極29と、ゲート電極29の側面とピラーの第1の側面26aとの間に配置された空隙と、を有する。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

電子機器

【課題】本発明は、アクティブマトリクス型の表示装置において、配線の断面積を増大させることなく、相性の悪い2つの膜(ITO膜とアルミニウム膜)からなる配線や電極等を接続し、且つ、大画面化しても低消費電力を実現することを課題とする。

【解決手段】本発明は、配線または電極をアルミニウム合金膜の単層とし、そのアルミニウム合金膜の組成を調節してITOとの良好なオーミック接合を目指すのではなく、3層構造とすることで課題を解決する。本発明は、アルミニウム原子のチャネル形成領域への拡散を防止するために、TiまたはMoからなる第1導電層を設け、その上に電気抵抗値の低いアルミニウム単体(純アルミニウム)からなる第2導電層を設ける。さらに、その第2導電層の上に、ITOと反応しないアルミニウム合金からなる第3導電層を設け、配線又は電極を3層構造としてITOと接合させる。

(もっと読む)

半導体装置及びその製造方法

【課題】モリセル領域内と周辺回路領域内およびそれらとの間に実施的に段差がない状態でメタル積層配線を形成し、段差部でメタル積層配線が断線する問題を回避する。センスアンプを構成するNMOSトランジスタとPMOSトランジスタのアンバランス動作を解消して動作遅延を軽減する。

【解決手段】半導体装置は、半導体基板上にメモリセル領域と周辺回路領域とを有し、メモリセル領域と周辺回路領域に跨って延在し、メモリセル領域ではビット線を構成し、周辺回路領域では周辺回路用配線の一部とゲート電極の一部を構成するメタル積層配線を有する。メモリセル領域に配置されるメタル積層配線の底面の半導体基板上面からの高さが、周辺回路領域に配置されるメタル積層配線の底面の半導体基板上面からの高さと実質的に同じである。

(もっと読む)

貫通配線基板の製造方法及び貫通配線基板

【課題】貫通孔の底面部付近において、導電層をカバレッジ良く形成し、接触不良がなく、電気的な安定性を向上させた貫通配線を、工程やコストを増加することなく形成する。

【解決手段】半導体基板の一方の面に第一絶縁層を介して導電部を形成する第一工程、ドライエッチング法により半導体基板の他方の面側から第一絶縁層が露呈するように貫通孔を形成する第二工程、貫通孔の内壁面および底面に第二絶縁層を形成する第三工程、第二絶縁層及び第一絶縁層のうち貫通孔の底面に位置する部分を除去し導電部を露呈する第四工程、第二絶縁層上に導電層を形成し該導電層を導電部と電気的に接続する第五工程、を有し、第四工程において、第二絶縁層に続いて導電部の一部をエッチングすると共に、エッチングにより除去された第一金属成分とエッチングガス成分とからなる第一副生成物を、貫通孔の底面部及びその近傍に位置する内壁面部に堆積させ、テーパー部を形成する。

(もっと読む)

貫通配線基板の製造方法

【課題】貫通配線基板の両面に実装するデバイスの電極配置が多様で且つ高密度である小型のデバイスであっても、実装するデバイス間の電極を自由度高く電気的に接続することが可能な貫通配線基板及びその製造方法の提供。

【解決手段】第1面1と第2面2とを有する基板と;第1面及び第2面の間を貫通する貫通孔内に、導電性物質を充填又は成膜して形成された複数の貫通配線12a,12bと;を備え、貫通配線同士は、互いに離間し、且つ基板の平面視において、重なり部分を少なくとも1つ備え、基板の第1面側又は第2面側からレーザー照射して、貫通孔を形成する領域を改質する工程Aと;前記改質された領域を除去して、貫通孔を形成する工程Bと;を含み、工程Aにおいて、複数の貫通孔形成領域のうち、レーザーの入射面から遠い方の重なり部分をレーザー照射した後に、レーザーの入射面から近い方の重なり部分をレーザー照射する貫通配線基板の製造方法。

(もっと読む)

薄膜トランジスタおよびその製造方法

【課題】保護膜(Al2O3)の膜質変化に起因するTFT特性のばらつきを軽減することが可能な薄膜トランジスタの製造方法を提供する。

【解決手段】TFT1の製造プロセスにおいて、ソース・ドレイン電極15上に、第1保護膜16(Al2O3層)とAl層とをこの順に、スパッタリングにより連続的に成膜する。各層のスパッタリングでは、いずれもターゲットとしてアルミニウムを用いるが、Al2O3層の成膜過程では、反応ガスとして使用する酸素ガスによってターゲット表面が変質し易い。その後、連続してAl層を成膜する(酸素ガスを使用しないスパッタリングを行う)ことで、ターゲット表面が改質される(成膜処理の度に、ターゲット表面が改質される)。従って、成膜処理回数が増しても、保護膜における膜厚や屈折率が変化しにくい。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の電気的な接続信頼性を向上させる。

【解決手段】(a)半導体基板の主面上に、主導体膜(下地膜)7Aおよび主導体膜7A上のストッパ絶縁膜(被測定膜)6sを積層する工程、(b)ストッパ絶縁膜6sに開口部8を形成する工程、を含んでいる。また、(c)開口部8に電子ビーム(励起線)EBを照射して、特性X線を放出させる工程、および(d)特性X線を検出し、特性X線の検出結果に基いて開口部8の底部8Bにおけるストッパ絶縁膜6sの有無または膜厚を判定する工程、を含んでいる。また、(d)工程では、特性X線に含まれる複数の元素成分の比率により、ストッパ絶縁膜6sの有無または膜厚を判定する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】縦型トランジスタの特性を悪化させることなく縦型トランジスタの設置面積を削減できる高集積化に適した半導体装置およびその製造方法を提供する。

【解決手段】一定の間隔を空けて配置された複数のピラー30が備えられ、複数のピラー30が、縦型トランジスタTのチャネルとして機能する半導体層からなるチャネルピラー1と、不純物拡散層からなり、前記チャネルピラー1の下部に接続されて縦型トランジスタTの一方のソースドレインとして機能する下部拡散層4に電気的に接続された引き上げコンタクトプラグ2とを含む半導体装置とする。

(もっと読む)

半導体装置の製造方法

【課題】的確かつ効果的にパターンを形成することが可能な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、下地領域上に、第1のピッチで配置された複数のダミーラインパターン21cを形成する工程と、ダミーラインパターン21cの両長側面に形成された所定マスク部分を有し、ダミーラインパターンを囲む閉ループ形状のマスクパターン25cを形成する工程と、ダミーラインパターン21cを除去する工程と、マスクパターン25cの両端部分を除去して所定マスク部分を残す工程と、所定マスク部分をマスクとして用いて下地領域をエッチングする工程とを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】センシング部を複数の基板で封止した半導体装置において、基板の平面方向に配線を設けたとしても、配線のレイアウトを簡略化することができる構造、およびその製造方法を提供する。

【解決手段】キャップ部300は、センサ部100に設けられた第1固定部と第2固定部とを電気的に接続したクロス配線部323を備え、クロス配線部323はキャップ部300の一面301に配置されたクロス配線322を備えている。また、キャップ部300は、キャップ部300を貫通し、一端がクロス配線322に電気的に接続され、他端がキャップ部300の他面302に配置された貫通電極344を備えている。これにより、貫通電極344を介してクロス配線322の電位、すなわち、センサ部100の第1固定部および第2固定部の電位をキャップ部300の他面302に取り出すことができる。

(もっと読む)

半導体装置及びその製造方法、並びにデータ処理システム

【課題】メモリセル領域に埋め込みゲート電極を有し、周辺回路領域にプレーナ型ゲート電極と貫通電極を有する半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、半導体基板50のメモリセル領域の溝部内に第一のゲート絶縁膜を介して、ワード線を埋め込み形成する工程と、周辺回路領域の前記半導体基板50上に、第二のゲート絶縁膜を介して周辺ゲート電極を形成する工程と、前記半導体基板50の主面上に層間絶縁膜と金属膜とを形成したのちに、前記金属膜をパターニングして、前記メモリセル領域の容量コンタクトパッドと前記周辺回路領域の局所配線127とを同時に形成する工程と、前記局所配線127の下面127a側を露出する開口151を形成したのちに導電体を充填することにより貫通プラグを形成する工程と、を採用する。

(もっと読む)

半導体装置の製造方法

【課題】より視認が容易なアライメントマークを簡素な工程で形成することが可能な、半導体装置の製造方法を提供する。

【解決手段】半導体基板SUBの主表面上に、主表面に対して段差を有するパターンMKが形成される工程と、パターンMK上に、半導体材料を含む第1の半導体層PS1が形成される工程と、第1の半導体層PS1上に、半導体材料を含む第2の半導体層PS2が形成される工程と、第2の半導体層PS2上にレジストパターンRSが形成される工程とを備えている。レジストパターンRSが形成される工程において、パターンMKが位置合わせマークとして用いられる。

(もっと読む)

薄膜トランジスタ及び液晶表示装置の作製方法

【課題】作製工程を大幅に削減し、低コストで生産性の良い液晶表示装置を提供する。消費電力が少なく、信頼性の高い液晶表示装置を提供する。

【解決手段】ゲート配線上の一部を含む半導体層のエッチングと、画素電極とドレイン電極を接続するためのコンタクトホールの形成を、同一のフォトリソグラフィ工程及びエッチング工程で行うことで、フォトリソグラフィ工程を削減する。これにより露出したゲート配線の一部を絶縁層で覆い、これに液晶層の間隔を維持するスペーサを兼ねさせる。フォトリソグラフィ工程を削減することにより、低コストで生産性の良い液晶表示装置を提供することができる。また、半導体層に酸化物半導体を用いることで、消費電力が低減され、信頼性の高い液晶表示装置を提供することができる。

(もっと読む)

表示装置

【課題】画素電極上に金属膜を形成して積層構造とする際に、1つのレジストマスクを用

いて、画素電極及び金属膜を形成することを課題とする。

【解決手段】画素電極となる導電膜と金属膜を積層させる。金属膜上に半透部を有する露

光マスクを用いて、膜厚の厚い領域と該領域よりも膜厚が薄い領域とを有するレジストパ

ターンを形成する。レジストパターンを用いて画素電極と、画素電極上の一部に接する金

属膜を形成する。以上により、1つのレジストマスクを用いて、画素電極及び金属膜を形

成することが可能となる。

(もっと読む)

201 - 220 / 1,717

[ Back to top ]