Fターム[5F033QQ19]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | ウェットエッチング (1,982)

Fターム[5F033QQ19]の下位に属するFターム

エッチング液 (265)

Fターム[5F033QQ19]に分類される特許

141 - 160 / 1,717

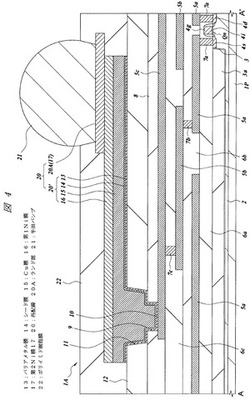

半導体集積回路装置およびその製造方法ならびにそれを用いた電子システム

【課題】再配線のランド部にバンプ電極が接続された半導体集積回路装置において、再配線と半田バンプとの接着強度を向上させる。

【解決手段】再配線20のランド部20Aは、再配線20を構成する5層の金属膜(バリアメタル膜13、シード膜14、Cu膜15、第1Ni膜16および第2Ni膜17)のうち、最上層の第2Ni膜17の面積が他の金属膜(バリアメタル膜13、シード膜14、Cu膜15、第1Ni膜16)の面積よりも大きくなるように構成され、この第2Ni膜17の表面に半田バンプ21が接続されている。そして、半田バンプ21の端部では、第2Ni膜17の直下にポリイミド樹脂膜22が形成されている。

(もっと読む)

トランジスタアレイ、およびその製造方法

【課題】簡略化された構成を有するトランジスタアレイを、簡易的に製造することが可能なトランジスタアレイの製造方法を提供することを主目的とする。

【解決手段】金属基板を用い、上記金属基板上に、絶縁性材料からなり、貫通孔を有する絶縁層を形成する絶縁層形成工程と、上記絶縁層上に、ドレイン電極が上記絶縁層に形成された貫通孔を介して上記金属基板に接続されるように薄膜トランジスタを形成する、薄膜トランジスタ形成工程と、上記金属基板をパターニングすることにより、上記金属基板を画素電極とする画素電極形成工程と、を有することを特徴とする、トランジスタアレイの製造方法を提供することにより、上記課題を解決する。

(もっと読む)

配線の形成方法

【課題】配線が微細化された場合でも、所望の高さの配線を得ることができる配線の形成方法を提供する。

【解決手段】実施形態によれば、まず、絶縁膜11上に形成した犠牲導体膜12に配線形成用溝12a,12bを形成する。ついで、配線形成用溝12a,12bが形成された犠牲導体膜12上の全面にCuを堆積し配線形成用溝12a,12b内に流動するようにリフローさせて、配線形成用溝12a,12b内にCu膜14bを形成する。その後、犠牲導体膜12とCu膜14bを通電層としてめっき法によって配線形成用溝12a,12b内のCu膜14b上にCu膜14cを積み増す。ついで、Cu膜14b,14cからなるCu配線14をCMP処理して平坦化した後、犠牲導体膜12を除去する。その後、Cu配線14が形成された絶縁膜11上に絶縁膜15を形成する。

(もっと読む)

Ti合金バリアメタルを用いた配線膜および電極、並びにTi合金スパッタリングターゲット

【課題】ウエットエッチングによる加工性に優れた特性を有する新規な金属配線用膜を提供すること。

【解決手段】表示装置またはタッチパネルセンサーの配線用膜であって、合金成分としてX群元素(Xは、希土類元素、Ge、Si、Sn、Hf、Zr、Mg、Ca、Sr、Al、Zn、Mn、Co、Fe、及びNiよりなる群から選択される少なくとも一種の元素)を3〜50原子%、および/または酸素を0.2〜3.0質量%含有し、残部Tiおよび不可避不純物からなるTi合金層(第1層)と、Al系膜からなる第2層とを含む積層構造を有することに要旨を有する配線用膜。

(もっと読む)

半導体装置およびその製造方法

【課題】SOGで平坦化した半導体装置であっても水分による閾値変動を抑制した半導体装置を提供する。

【解決手段】SOG平坦化後にSOGを除去したMOSトランジスタ領域を単層配線とし、SOGを残した非MOSトランジスタ領域を多層配線とすることで、SOGを介したMOSトランジスタへの水分の影響が無くなり、MOSトランジスタの閾値変動を抑制できる。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、製造コストの増大を抑制しつつ、簡易な構成で、絶縁膜とさらに上部に形成された絶縁膜との界面の電荷を低減することができる半導体装置の製造方法の提供を目的とする。

【解決手段】本発明にかかる半導体装置の製造方法は、(a)SiC半導体を用いた基板を用意する工程と、(b)前記基板の表層部において、前記基板の素子領域を囲むように、リセス構造と前記リセス構造の下部にガードリング層とを形成する工程と、(c)前記ガードリング層を覆って、第1絶縁膜を形成する工程と、(d)前記第1絶縁膜を覆って、前記第1絶縁膜とは異なる材質の第2絶縁膜を形成する工程と、(e)前記第1絶縁膜上に蓄積する電荷とは逆電荷のイオンを、前記工程(d)の前、又は、前記工程(d)中、又は前記工程(d)の後に照射する工程とを備える。

(もっと読む)

ホール形成方法、並びに該方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステム

【課題】プロセス再現性が高く、微細なホールを効率よく低コストで形成することができるホール形成方法、並びに、該ホール形成方法を用いてビアホールを形成した多層配線、半導体装置、表示素子、画像表示装置、及びシステムの提供。

【解決手段】基材上にピラー形成液を付与してピラーを形成するピラー形成工程と、前記ピラーが形成された基材上に絶縁膜形成材料を付与して絶縁膜を形成する絶縁膜形成工程と、前記ピラーを除去して前記絶縁膜に開口部を形成するピラー除去工程と、前記開口部が形成された絶縁膜を熱処理する熱処理工程とを含むホール形成方法である。

(もっと読む)

半導体装置の製造方法

【課題】膜厚の薄い抵抗体もつ抵抗素子を形成する際に、抵抗体の断線に対して強い抵抗素子を提供する。

【解決手段】バリアメタル膜とアルミ電極膜からなる積層電極の先端領域を単層のバリアメタル電極とし、並列するバリアメタル電極間に電気的に接続する抵抗体をリフトオフ法にて形成する。

(もっと読む)

室温金属直接ボンディング

【課題】外からの圧力を用いることなく、低温または室温でウエーハーを貼り合わせる。

【解決手段】貼り合わされたデバイス構造であって、デバイスまたは回路に接続された第1の組の金属ボンディングパッドおよび第1の基板10上の金属ボンディングパッドに隣接する第1の非金属領域を有する第1の基板、デバイスまたは回路に接続された第1の組の金属ボンディングパッドに隣接する第2の組の金属ボンディングパッド、および第2の基板13上の金属ボンディングパッドに隣接する第2の非金属領域を有する第2の基板、および第2の非金属領域に対して第1の非金属領域を接触ボンディングさせることにより形成される第1と第2の組の金属ボンディングパッドの間の接触ボンディングされた界面を含むボンディングされたデバイス構造。第1と第2の基板の少なくとも一方は弾性的に変形され得る。

(もっと読む)

貫通孔基板、貫通配線基板、電子部品、基板の製造方法、及び貫通孔の検査方法

【課題】貫通孔内の状態を確認できる貫通孔基板、貫通配線基板、電子部品、基板の製造方法、及び貫通孔の検査方法の提供。

【解決手段】(1)基板1の一面1aから他面1bにかけて貫通孔4が形成され、一面1aにおける貫通孔4の開口部5を覆う導電パターン2が配された貫通孔基板であって、導電パターン2には、貫通孔4を一面1a側から観察可能な切抜き3が形成されていることを特徴とする貫通孔基板。(2)切抜き3において、開口部5の縁が観察可能であることを特徴とする(1)に記載の貫通孔基板。

(もっと読む)

不揮発性半導体記憶装置の製造方法

【課題】選択ゲート電極および当該選択ゲート電極に隣接する他のゲート電極間の間隔を所望の距離に調整できるようにした不揮発性半導体記憶装置の製造方法を提供する。

【解決手段】複数本のラインパターンのうち選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてマスクした条件にて複数本のラインパターンの側壁面をスリミングし、選択ゲート電極の形成領域のラインパターンから他のゲート電極の形成領域のラインパターンにかけてパターン間膜を埋込むと共にスリミングされたラインパターンの側壁面に沿ってパターン間膜を形成し、選択ゲート電極の形成領域のラインパターンをマスクした条件にて当該ラインパターン以外のラインパターンを除去しマスクされたラインパターンを残留させ、パターン間膜および残留したラインパターンをマスクとして第1膜を異方性エッチングし、第1膜をマスクとして導電膜をエッチングする不揮発性半導体記憶装置の製造方法を提供する。

(もっと読む)

半導体装置

【課題】配線及びビア間接続の信頼性を向上させた半導体装置を提供する。

【解決手段】実施形態に係る半導体装置は、半導体基板と、前記半導体基板上の異なる高さに配置され、配線が形成された複数の配線層と、前記配線層の積層方向に延びる柱状に形成され、異なる複数の前記配線層の配線間を電気的に接続するビアとを備える。前記配線の一部は、前記ビアの中間部において前記ビアに接触する中間配線であり、所定の前記配線層の中間配線は、前記ビアを前記積層方向に直交する方向で貫通し、且つ、上面、下面及び両側面において前記ビアと接触していることを特徴とする。

(もっと読む)

半導体装置の製造方法及び半導体ウエハ

【課題】 導電体部を有し、複数の絶縁膜を除去して形成される半導体装置において、金属汚染を抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】 導電パターンを有する配線層と、導電パターンの側面を囲む第1の絶縁膜を含む複数の絶縁膜と、を有する半導体装置の製造方法において、半導体ウエハ上に複数の絶縁膜を形成する工程と、配線層を形成する工程と、を有する。そして、半導体ウエハ上に複数の絶縁膜を形成する工程及び配線層を形成する工程の後に、複数の絶縁膜の一部の領域を除去し、開口を形成する工程と、を有する。ここで、第1の絶縁膜は、導電パターンの配置位置のうちウエハの最外周に最も近い位置よりも半導体ウエハの外周に近い位置まで配置されている。

(もっと読む)

半導体装置

【課題】プロセス加工性と信頼性に優れた半導体装置を提供する。

【解決手段】必要な回路が形成された半導体表面に、エポキシ樹脂、エポキシ樹脂硬化剤及び平均一次粒子径1μm以下の有機フィラーの成分を含む樹脂組成からなる絶縁層を1層又は複数層備え、かつ同一層内及び層間接続の配線導体として銅を用いた回路3を任意の箇所に形成してなる半導体装置。

(もっと読む)

半導体装置

【課題】高い耐電圧特性、および耐リーク特性を有する配線構造を備える半導体装置、およびその製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置は、半導体素子が設けられた半導体基板と、前記半導体基板上に形成された、上下層の導電部材を電気的に接続する接続部材と、前記接続部材と同じ層に形成された第1の絶縁膜と、前記接続部材の上面の一部と接する第1の領域、および前記第1の領域上に位置し、前記第1の領域よりも幅の広い第2の領域を含む配線と、前記第1の絶縁膜上に、前記配線の前記第1の領域の側面の上側から少なくとも一部、および前記第2の領域の底面に接して形成された第2の絶縁膜と、を有する。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】コストが低い半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体記憶装置の製造方法は、絶縁膜及び電極膜が交互に積層された積層体を形成する工程と、前記積層体上に、サイズが相互に異なる複数のホールが形成されたハードマスクを形成する工程と、マスク材料を堆積させることにより、最も小さい前記ホールを閉塞させると共に、その他の前記ホールを小さくする工程と、前記マスク材料及び前記ハードマスクをマスクとしてエッチングを施すことにより、前記その他のホールの直下域において、各所定枚数の前記絶縁膜及び前記電極膜を除去して、コンタクトホールを形成する工程と、前記コンタクトホールを介してエッチングを施すことにより、前記電極膜の一部分を除去して隙間を形成する工程と、前記隙間内に絶縁材料を埋め込む工程と、前記コンタクトホール内に導電材料を埋め込む工程と、を備える。

(もっと読む)

半導体装置の製造方法、半導体装置、および電子機器

【課題】配線層の露出面において、ダイシングの工程等で水が接触することにより生じ、配線層の露出面における接合強度の低下や外観不良等の原因となる腐食の発生を抑制する。

【解決手段】半導体基板の一方の面側にて、標準電極電位が互いに異なる2種以上の金属を含む合金により形成された配線層を露出させる工程(パッドを開口する工程(S10))と、前記配線層の露出面を含む範囲に、N2/Arプラズマを照射するプラズマ処理を行う工程(N2/Arプラズマ処理を行う工程(S30))と、を含む方法を用いる。

(もっと読む)

絶縁膜の形成方法

【課題】均一で高い充填密度を有し、かつ欠陥が少ない絶縁膜を形成することができる方法の提供。

【解決手段】基板表面に、二酸化ケイ素微粒子と、ポリマーと、界面活性剤と、分散媒とを含む二酸化ケイ素分散液を塗布し、次いでポリシラザン組成物を塗布した後、加熱して絶縁膜を形成させる、絶縁膜の形成方法。

(もっと読む)

半導体装置

【課題】プロセス数を増大させることなく、応力を緩和できる構造を有する半導体装置を提供する。

【解決手段】一方の面に埋め込み酸化層と半導体層がこの順で積層される半導体基板10を加工して作製され、前記一方の面側で他の基板に接合される半導体装置であって、前記埋め込み酸化層及び前記半導体層を加工して形成される半導体素子20と、前記埋め込み酸化層及び前記半導体層を加工して形成され、前記半導体素子に接続される配線部と、前記配線部の端部に連続する前記半導体層によって構成され、当該半導体層の下側の埋め込み酸化層が除去されて前記半導体基板との間に空隙が形成されるパッド部40と、前記パッド部と前記他の基板を接合する接合部とを含む。

(もっと読む)

配線又は電極の形成方法、電子デバイス及びその製造方法

【課題】下地にダメージを与えず、また、電極材料のゴミの再付着も防止される配線又は電極の形成方法と、この配線又は電極の形成方法により配線又は電極を形成する電子デバイス及びその製造方法を提供する。

【解決手段】下地2上に第1のレジスト層1を形成し、開口部5を形成し、導電材料層3を成膜する。導電材料層3の全体を覆う第2のレジスト層4を形成し、該開口部5以外の導電材料層3上の第2のレジスト層4を除去することにより、該開口部5の導電材料層3を覆う保護レジスト層4’を形成する。該保護レジスト層4’で覆われていない導電材料層3を除去し、次いで保護レジスト層1,4’を除去することにより、残留した導電材料3よりなる配線又は電極を形成する。

(もっと読む)

141 - 160 / 1,717

[ Back to top ]