Fターム[5F033QQ31]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチバック (992)

Fターム[5F033QQ31]に分類される特許

201 - 220 / 992

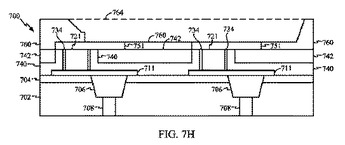

磁気トンネル接合を含む上部および下部電極を有するデバイスの製造および統合

電子デバイス製造プロセスは、下部電極層を堆積する段階を含む。次いで、電子デバイスが下部電極層上に製造される。下部電極層をパターニングする段階は電子デバイスを製造する段階後に、上部電極をパターニングする段階とは個別のプロセスで実施される。第1誘電体層は次いで、電子デバイスおよび下部電極層上に堆積され、上部電極層がそれに続く。上部電極は次いで、下部電極とは別のプロセスでパターン化される。上部および下部電極の別々のパターニングにより、電子デバイス間の誘電体材料におけるボイドが減少することによって収率が向上する。その製造プロセスが適切な1つの電子デバイスが、磁気トンネル接合(MTJ)である。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 埋め込み配線を形成する時に、埋め込み不良が生じにくい半導体装置の製造方法を提供する。

【解決手段】

(a)コンタクトプラグ25を有する第1層間絶縁膜24上に第2層間絶縁膜27を積層する工程と、(b)前記第2層間絶縁膜27に前記コンタクトプラグ25の上面を露出するトレンチ28aを形成する工程と、(c)前記トレンチ28a内で、開口端側に空間部を形成し、前記コンタクトプラグ側に、レジスト29cを埋め込む工程と、(d)等方性エッチングにより、前記第2層間絶縁膜27bのうち前記トレンチ28aの空間部で挟まれる前記第2層間絶縁膜27b部分の側壁を側方に後退させて、前記トレンチ28aの開口端側の幅よりも開口端側の幅が大きな加工トレンチ28bを形成する工程と、(e)前記レジスト29cを除去し、前記加工トレンチ28b内に配線金属層を埋め込む工程と、を含むことを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】3Dピラートランジスタにおいて、ゲートコンタクトとシリコン基板との間のショートを抑制した半導体装置及びその製造方法を得るという課題があった。

【解決手段】半導体からなる基板1と、一面1aから突出され、前記半導体からなる第1の突出部2と、一面1aに設けられた溝部1cに充填された第1の絶縁体3と、第1の突出部2に隣接して一面3aから突出され、第1の絶縁体3からなる第2の突出部4と、第1の突出部2の側面を覆うゲート絶縁膜5と、ゲート絶縁膜5を覆うゲート電極6と、第1の突出部2に設けられた上部拡散層13と、下部拡散層14と、第2の突出部4の側面を覆うとともにゲート電極6に接続された連結電極60と、第1の突出部2及び第2の突出部4を覆う層間絶縁膜と、前記層間絶縁膜を貫通して連結電極60に接するゲートコンタクト10と、を有する半導体装置及びその製造方法を用いることにより、上記課題を解決できる。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】縦型MOSトランジスタを備えた半導体装置を形成する際のゲート電極とコンタクトプラグとの短絡を防止することが可能な半導体装置及びその製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、前記半導体基板上にシリコン窒化膜(SiN膜)からなるマスク窒化膜のパターンを形成したのちに、溝および半導体ピラーを前記半導体基板に形成する第一工程と、前記マスク窒化膜を残存させたまま、前記溝を覆うゲート絶縁膜を形成したのちに前記半導体ピラーよりも低い高さのゲート電極を形成する第二工程と、前記溝を覆うように、シリコン酸窒化膜(SiON膜)からなるライナー膜を形成したのちに、前記ライナー膜上を覆い、かつ、前記溝内を充填するように層間膜(SOD膜)を形成する第三工程と、前記マスク窒化膜をエッチングにより選択的に除去する第四工程と、を採用する。

(もっと読む)

半導体装置とその製造方法、及び電子機器

【課題】積層される半導体ウェハにより、量産性向上、コスト低減を図った、固体撮像装置等の半導体装置とその製造方法を提供する。

【解決手段】半製品状態の回路を備えた半導体ウェハ31,45を複数積層して貼り合わせ、複数の半導体ウェハ31,45からなる積層体を形成し、積層体のうち、上層の半導体ウェハ31の半導体層を薄肉化する。また、上層の半導体ウェハ31側から最下層の半導体ウェハ45に形成された配線に達する貫通開口部77を形成し、最下層の半導体ウェハ45に形成された配線を露出させることにより電極パッド部78を形成する。これにより、貫通開口部77は、半導体ウェハ31,45の脆弱な接合面を貫通して形成され、電極パッド部78は、脆弱な接合面よりも下層の半導体ウェハ45の配線において形成される。これにより、電極パッド部78における外部配線との配線時に、脆弱な接合面に係る応力を低減することができる。

(もっと読む)

半導体装置の製造方法。

【課題】本発明は、埋込みビットラインの抵抗を減少させ高速動作に有利な半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、ハードマスク膜をバリアとして半導体基板をエッチングし、複数の活性領域を画定するトレンチを形成するステップと、ハードマスク膜が突出部となるように前記トレンチ内部を一部ギャップフィルするギャップフィル膜を形成するステップと、突出部の両側側壁を覆うスペーサを形成するステップと、ドープドエッチング障壁膜をエッチングバリアとしてスペーサのうち何れか1つのスペーサを除去するステップと、残留するスペーサをエッチングバリアとして前記ギャップフィル膜をエッチングし、活性領域の一側側壁を露出させる側壁トレンチを形成するステップと、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、高速動作を具現することができる埋込型ビットラインを備える半導体装置、およびその製造方法を提供する。

【解決手段】このための本発明の半導体装置は、トレンチを備える基板と、前記基板内に形成され前記トレンチ側壁に接する金属シリサイド膜と前記トレンチ側壁に形成され前記金属シリサイド膜と接する金属性膜からなる埋込型ビットラインとを備えており、上述した本発明によれば、金属シリサイド膜と金属性膜からなる埋込型ビットラインを提供することによって、従来のシリコン配線形態の埋込型ビットラインに比べて、その抵抗値を顕著に減少させることができるという効果がある。

(もっと読む)

半導体素子

半導体素子(例えば、フリップチップ)は、介在層によってドレインコンタクトから分離されたサブストレートを含む。前記介在層を通じて延びる前記素子の動作時において、トレンチ状のフィードスルー要素を用いて、前記ドレインコンタクトおよび前記サブストレートを電気的に接続する。 (もっと読む)

半導体装置の製造方法および半導体装置

【課題】 デュアルダマシン法を用いて銅の埋め込み配線および接続プラグを形成するとき、接続プラグ中のボイド発生を防止する。

【解決手段】 Low−k膜13、15、ELK膜14、TEOS膜16からなる層間絶縁膜にプラグとなる接続孔19aを形成した後、酸素プラズマ処理を行って変質層20を形成し、この層を薬液処理により選択的に除去すると、ELK膜14が多孔質であることに起因してその側壁21にLow−k膜13、15などより大きい角度のテーパーが形成される。次に配線埋め込み用の溝の底面がELK膜14中にくるように形成して、プラグ開口の入口が広がる形状にした後、銅膜を埋め込む。

(もっと読む)

半導体装置

【課題】SRAMのメモリセルの面積を減少させる。

【解決手段】半導体装置は、基板上のメモリセル領域内に設けられた第1活性領域と、第1活性領域と素子分離により分離され、第1活性領域内よりもメモリセル領域の中心に近い位置に設けられた第2活性領域と、第1活性領域を横断する第1ゲート電極と、第1ゲート電極と離間し、第1活性領域および第2活性領域を横断する第2ゲート電極と、第1活性領域で、第1ゲート電極と第2ゲート電極との間の第1ドレイン部と、第2活性領域で、第2ゲート電極の第1ドレイン部側の第2ドレイン部と、第1ドレイン部と第2ドレイン部とを接続する第1配線と、第1ゲート電極および第2ゲート電極と離間し、端部が第1ゲート電極の第2活性領域側の端部と対向する第3ゲート電極と、第2ドレイン部と第3ゲート電極とを接続する第2配線とを備え、第3ゲート電極の上面と第2配線の上面はほぼ同じ高さに形成されている。

(もっと読む)

半導体装置の製造方法及びそれを用いた半導体装置

【課題】MIPS構造を採るメタル膜とコンタクトプラグとの界面抵抗を低減できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を形成し、形成したゲート絶縁膜3の上に、TiN膜4及びポリシリコン膜5を順次形成する。続いて、ポリシリコン膜5にTiN膜4を露出するコンタクトホール5aを形成する。続いて、ポリシリコン膜5における第1のコンタクトホール5aの少なくとも底面及び壁面上に金属膜7を形成する。

(もっと読む)

電子部品の製造方法

【課題】側壁転写プロセスにより複数層に形成された配線層を有する電子部品を簡便且つ安価な方法で得ること。

【解決手段】パターン27の側壁に沿った閉ループを有する側壁膜30を形成し、このパターン27を除去して前記側壁膜30を残存させた後この側壁膜30をマスクとして下地材料を選択的に除去する側壁転写プロセスを用いて下層配線層21を形成する第1の工程と、前記下層配線層21の上層に、前記側壁転写プロセスを用いて1層以上の上層配線層41,51を他の層22,23,24,42,43,44を介して形成する第2の工程と、前記下層配線層21および前記上層配線層41,51のそれぞれを切断するエッチングを一括で行うことにより、前記下層配線層21と前記上層配線層41,51に対して閉ループカットを施す第3の工程と、を含む。

(もっと読む)

集積回路構造

【課題】導電ビア(TSV)に接続されるウェハ背部の相互接続構造を有する集積回路構造を提供する。

【解決手段】集積回路構造は、正面と背面を有する半導体基板と、半導体基板を貫通する導電ビアと、半導体基板の背面上の金属構造と、を備える。金属構造は、導電ビアを被覆して、接触する金属パッド、及び、導電ビア上の金属線を含む。金属線は、デュアルダマシン構造を含む。集積回路構造は、更に、金属線上のバンプを具備する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】レーザートリミング加工を行うヒューズ素子を有する半導体集積回路装置の信頼性を向上させる。

【解決手段】隣り合うヒューズ素子に接続する第1層目のアルミニウム配線間のスペース幅を第1層目の金属間絶縁膜の側壁厚さの2倍未満とすることで、吸湿性のSOGの露出を防止する。また、第1層目のアルミニウム配線側面にサイドスペーサーを設けることでより一層の信頼性向上を図る。

(もっと読む)

3次元半導体メモリ装置及びその製造方法

【課題】3次元半導体メモリ装置及びその製造方法を提供する。

【解決手段】本装置は、積層された導電パターン、導電パターンを貫通する活性パターン及び導電パターンと活性パターンとの間に介在される情報貯蔵膜を含む少なくとも1つのメモリ構造体を含み、活性パターンは積層された下部及び上部貫通ホールを各々満たす下部及び上部半導体パターンを含むことができる。1つのメモリ構造体を構成する情報貯蔵膜は同一の工程段階を利用して実質的に同時に形成され、1つのメモリ構造体を構成する下部及び上部貫通ホールは互いに異なる工程段階を利用して順に形成され得る。

(もっと読む)

マスクパターンの形成方法及び半導体装置の製造方法

【課題】SWPにおいて、側壁部の形状の対称性を高め、被エッチング膜をエッチングするときの加工精度を向上させることができるマスクパターンの形成方法を提供する。

【解決手段】基板上の被エッチング膜の上に形成されたシリコン膜よりなる第1のライン部が配列したシリコン膜パターンの表面を等方的に被覆するように、カーボン膜を成膜する成膜工程S18と、カーボン膜を第1のライン部の上部から除去すると共に、第1のライン部の側壁部として残存するように、カーボン膜をエッチバックするエッチバック工程S19と、第1のライン部を除去し、側壁部が配列したマスクパターンを形成するシリコン膜除去工程S20とを有する。

(もっと読む)

薄膜抵抗素子、および、その製造方法

【課題】安定して配線と抵抗体薄膜との接触が可能な接続構造をもつ薄膜抵抗素子を実現する。

【解決手段】互いに離間する2つの電極配線(3A,3B)に、抵抗体薄膜5を接続させている。2つの電極配線の各々が、主配線部3mと、当該主配線部3mのコア配線部3cより酸化されにくい導電材料で側面に形成されている側壁導電膜3sとを有する。抵抗体薄膜5は、2つの電極配線の各々に対して、側壁導電膜3sを介して電気的に接続している。

(もっと読む)

配線パターン形成方法および半導体装置の製造方法、半導体装置、データ処理システム

【課題】2回のリソグラフィ工程によるSADP法(Self Align Double Patterning)を用いて、第1配線パターン形成領域には解像限界未満のパターンを含む第1配線パターンを形成し、第2配線パターン形成領域には解像限界以上の通常パターンからなる第2配線パターンを簡便に形成する方法を提供する。

【解決手段】解像限界未満の寸法を有する複数の配線を含む第1配線パターンを、第1リソグラフィ工程と第1リソグラフィ工程の後に実施される第2リソグラフィ工程を用いて形成し、第1のリソグラフィ工程で形成されたパターンに対してのみサイドウォールの形成および除去処理を行い、その後、解像限界以上のパターンを生成する第2リソグラフィ工程を実施する。第2のリソグラフィ工程で形成される解像限界以上の通常パターンに対しては、単純なリソグラフィ工程とすることが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、収納容器に半導体ウエハを長期間保管しても、パッド部にフッ化物などの汚染物質が付着することを防止できる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、スクライブライン及びスクライブラインの内側に位置する製品チップ領域を有する半導体ウエハ上に絶縁膜を形成する工程(S12)と、製品チップ領域上に位置する第1のパッド部及びスクライブライン上に形成された評価用素子に接続された第2のパッド部を絶縁膜上に形成する工程8(S13)と、絶縁膜上、第1及び第2のパッド部の上にパッシベーション膜を形成する工程(S14)と、半導体ウエハを、収納容器に保管する工程(S15)と、収納容器から半導体ウエハを取り出し、パッシベーション膜をエッチングすることにより、パッシベーション膜に第1のパッド上に位置する開口部を形成する工程(S17)とを具備することを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】同一の半導体基板上に、高性能な低電圧MISFET、高信頼なMONOS型不揮発性メモリおよび高電圧MISFETを形成する。

【解決手段】ロジック回路などに使用される低電圧MISFETの形成領域において、キャップ酸化膜をマスクにすることによってダミーゲート電極上にシリサイドが形成されるのを防ぎ、ダマシンプロセスを用いて低電圧MISFETのゲートをhigh−k膜18およびメタルゲート電極20で形成する際の形成工程を簡略化する。また、ダミーゲート電極除去時のRIEによりダメージを受けたゲート絶縁膜を一旦除去し、新たにゲート酸化膜17を形成することで素子の信頼性を確保する。

(もっと読む)

201 - 220 / 992

[ Back to top ]