Fターム[5F033QQ31]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチバック (992)

Fターム[5F033QQ31]に分類される特許

121 - 140 / 992

半導体装置、およびその製造方法、ならびにデータ処理装置

【課題】テーパー部を有する溝を備えた半導体装置を容易に形成する。溝内に空洞が形成されるのを防止すると共に、製造歩留まりの低下を抑制する。

【解決手段】半導体装置は、第1の面を有する材料層と、材料層内に設けられ、第1の面に開口部を有する溝を備える。溝は、開口部に接し1以上のスキャロップ形成溝を有するテーパー部と、おおむね垂直な側壁を有する垂直部を有する。スキャロップ形成溝の幅は、垂直部の溝幅よりも大きくなっている。

(もっと読む)

半導体装置及びその製造方法

【課題】容量素子の良好な特性と高い信頼性を実現することが可能な半導体装置を提供する。

【解決手段】半導体基板上に第1の絶縁膜を介して形成されている下部電極と、この下部電極の周囲に形成され、下部電極の表面よりも高い表面を有するダミー電極と、下部電極上にダミー電極の最上表面よりも表面が低い位置にある誘電体膜を介して形成された上部電極と、ダミー電極に周囲を囲まれた窪みを埋める第2の絶縁膜とを具備して成る半導体装置を構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】更なる微細化に対応した高集積度のDRAMを得ることが可能な半導体装置及びその製造方法を提供する。

【解決手段】半導体基板2の表層に、第1の方向Yに延在する第1の溝部3と、第2の方向Xに延在し且つ第1の溝部3よりも深くなる第2の溝部5と、第1の溝部3と第2の溝部5との交差部分において第2の溝部5よりも深くなる第3の溝部7と、第1の溝部3と第2の溝部5との間から突出されたピラー部8と、ピラー部8に形成された下部拡散層9、チャネル領域10及び上部拡散層11と、第2の溝部5の内側において第2の方向Xに延在するビット配線層と、第1の溝部3の内側においてピラー部8の側面を覆うゲート絶縁膜と、第1の溝部3の内側においてゲート絶縁膜を介してピラー部8の側面を横切るように第1の方向Yに延在するワード配線層とを備える。

(もっと読む)

グラフェン配線およびその製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】グラフェン配線は、配線溝を有する絶縁膜13と、前記配線溝内の両側面の前記絶縁膜上に形成された第1触媒膜15と、前記配線溝内の両側面の前記第1触媒膜上に形成され、両側面に対して垂直方向に積層された複数のグラフェンシートで構成された第1グラフェン層16と、を具備する。

(もっと読む)

不揮発性記憶装置およびその製造方法

【課題】より低抵抗な配線層を有する不揮発性記憶装置を提供する。

【解決手段】実施形態の不揮発性記憶装置は、書き替え可能な複数の不揮発性メモリセルと、前記複数のメモリセルのそれぞれに電気的に接続可能な配線層と、を備えた不揮発性半導体記憶装置である。前記配線層は、絶縁層に設けられたトレンチ内に設けられ、前記配線層は、第1導電層と、前記第1導電層の上に設けられた第2導電層と、を有し、前記配線層が充填されていない前記トレンチに対する前記第1導電層の埋め込み性は、前記配線層が充填されていない前記トレンチに対する前記第2導電層の埋め込み性よりも高く、前記第2導電層の比抵抗は、前記第1導電層の比抵抗よりも低い。

(もっと読む)

半導体装置の製造方法

【課題】メタルゲートプロセスにおけるプリメタル層間絶縁膜の平坦性を向上できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を介在させてゲート電極4を形成する。その後、半導体基板1にゲート電極4をマスクとしてソース・ドレイン領域を形成する。続いて、ゲート電極4を覆うように半導体基板1上の全面に第1の酸化シリコン膜10を形成する。その後、ゲート電極4をストップ膜とするCMP法により、第1の酸化シリコン膜10を平坦化する。続いて、ゲート電極4を含む第1の酸化シリコン膜10の上に、第2の酸化シリコン膜11を形成する。その後、ゲート電極4をストップ膜とするCMP法により、第2の酸化シリコン膜10を平坦化する。さらに、ゲート電極4を含む第2の酸化シリコン膜10の上に、第3の酸化シリコン膜12を形成する。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】1つの実施形態は、絶縁膜に形成された溝に導電物質を容易に埋め込むことができる半導体装置の製造方法、及びそのような製造方法に適した半導体装置を提供する。

【解決手段】1つの実施形態によれば、コンタクトプラグを形成し、コンタクトプラグを覆うエッチングストッパー膜を形成し、エッチングストッパー膜を覆う絶縁膜を形成し、絶縁膜及びエッチングストッパー膜にコンタクトプラグの表面を露出する溝を形成し、エッチングストッパー膜のエッチングレートに対し絶縁膜のエッチングレートの方が高くなる条件で、コンタクトプラグとコンタクトプラグの周辺とを含む領域を選択的にエッチバックし、エッチバックを行った後に溝に導電物質を埋め込んでラインパターンを形成する。

(もっと読む)

半導体装置の製造方法

【課題】めっき工程の埋設不良を抑制する。

【解決手段】半導体基板100上に設けられた層間絶縁膜320に開口部を形成する工程と、開口部上面にバリア層340を形成するバリア層形成工程と、バリア層340上に配線シード層を形成する配線シード層形成工程を有する。また、バリア層形成工程は、選択成膜工程と、スパッタエッチング工程を有する。バリア層340の選択成膜工程は、バリア層340を、開口部の平面部342のみに選択的に成膜する。次いで、バリア層340のスパッタエッチング工程は、平面部342のバリア層340をスパッタエッチングしながらバリア層340のスパッタ粒子を開口部の側壁部344に堆積させる。

(もっと読む)

半導体装置の製造方法

【課題】容量コンタクトパッドと容量コンタクトプラグが一体となった構造を形成する。これにより、従来は2回、必要だったフォトリソグラフィ工程を1回に削減して、製造コストを低減する。

【解決手段】半導体装置の製造方法では、層間絶縁膜上に、開口を有するマスクパターンを形成する。このマスクパターンを用いて、層間絶縁膜をエッチングすることにより、開口の下の層間絶縁膜内に容量コンタクトホールを形成する。湿式エッチングにより、マスクパターン内の開口を大きくした後、開口内に導電材料を埋め込むことにより、それぞれ容量コンタクトプラグ及び容量コンタクトパッドを形成する。この後、容量コンタクトパッド上にキャパシタを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】メモリセル領域の周辺に金属電極を有するアンチフューズを製造歩留り良く形成する。

【解決手段】MOSトランジスタを備えたメモリセルを有するメモリセル領域と、アンチフューズを備えた周辺回路領域とを有する半導体装置において、メモリセルを構成するコンタクトプラグ又はビット配線と同層に形成される周辺回路のコンタクトプラグ又は配線を用いて、アンチフューズの電極を形成する。

(もっと読む)

パターン形成方法及びデバイス製造方法

【課題】露光装置の解像限界よりも微細な非周期的な部分を含むパターンを、露光装置を用いて形成する。

【解決手段】パターン形成方法は、ウエハW上に第1L&Sパターン71を形成し、第1L&Sパターン71を覆うように第1保護層48、周期方向が直交する第2L&Sパターン78、及びフォトレジスト層60を形成し、第2L&Sパターン78の一部と重なるように、フォトレジスト層60に第1開口部60A,60Bを有する第3パターンを形成し、第1開口部60A,60Bを介して第1保護層48に第2開口部48A,48Bを形成し、第2開口部48A,48Bを介して第1L&Sパターン71の一部を除去する。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で横方向に成長するシリコン膜が連結されることを防ぎつつ、活性領域上に十分な厚みのシリコン膜を形成可能とした半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上に第1のシリコン膜12aを選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に第1のシリコン膜12aを覆うのに十分な厚みでマスク絶縁膜を埋め込んだ後、このマスク絶縁膜を第1のシリコン膜12aの表面が露出するまでエッチングにより除去する工程と、第1のシリコン膜12a上に第2のシリコン膜12bを選択的にエピタキシャル成長させる工程とを含む。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、微細化された埋め込みビット線を容易に形成可能であると共に、埋め込みビット線の抵抗値を低くすることで高性能化を実現可能な半導体装置及びその製造方法を提供することを課題とする。

【解決手段】半導体基板13の主面13aに形成された第1の溝15と、第1の溝15の底面15a、及び第1の溝15の底部15Aに位置するピラー26の側壁面26a,26bに設けられ、側壁面26aを露出する第1の開口部16A、及び側壁面26bを露出する第2の開口部16Bを有した絶縁膜16と、第1の開口部16Aから露出された側壁面26aに形成された半導体基板と反対導電型の下部不純物拡散領域18と、絶縁膜16を介して、第1の溝15の底部15Aに設けられ、第1及び第2の開口部16A,16Bを埋め込むと共に、下部不純物拡散領域18及び側壁面26bと接触し、かつ金属膜よりなる埋め込みビット線21と、を有する。

(もっと読む)

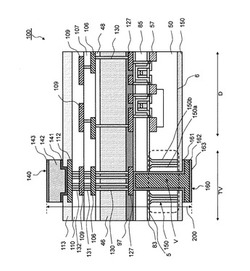

トレンチゲートMISデバイスの構造及び製造方法

【課題】より単純に製造でき、かつ平坦なトポロジを得ることができ、更にトレンチの上部曲がり部における降伏電圧の問題が解消されたトレンチゲートMISデバイスを提供すること。

【解決手段】トランジスタセルを含む活性領域と、トランジスタセルを含まないゲート金属領域と、ゲート金属層とを含み、半導体チップの表面のパターンに、活性領域からゲート金属領域に至るトレンチが形成されており、このトレンチが絶縁材料の層で裏打ちされた壁部を有し、導電性ゲート材料がトレンチ内に設けられており、導電性ゲート材料の上面が半導体チップの上面より下側に位置し、非導電層が活性領域及びゲート金属領域の上に位置し、ゲート金属領域におけるトレンチの一部の上側の非導電層に開口が形成されており、ゲート金属がトレンチ内の接触領域のゲート材料と接触するように、開口が前記ゲート金属で満たされているトレンチゲートMISデバイス。

(もっと読む)

導電材埋め込み方法及び半導体装置の製造方法

【課題】 従来の方法と比較して、短時間で凹部の全体に導電材を埋め込むことができる技術を提供する。

【解決手段】 本願に係る導電材の埋め込み方法は、半導体装置の製造過程において表面に形成される凹部22に導電材を埋め込む方法に関する。この方法は、凹部22の少なくとも底面に露出する下地層10の表面に不純物24aを定着させる不純物定着工程と、不純物24aが定着した下地層10を利用して導電材をVLS成長させて、凹部の全体に導電材を埋め込むVLS成長工程とを有する。この方法では、VLS成長によって凹部22に導電材を埋め込むため、短時間で導電材を埋め込むことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】接続不良の発生を抑制することのできる、信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、所定ピッチで所定の幅の素子領域が形成された半導体基板と、半導体基板上に積層された層間絶縁膜と、層間絶縁膜の上面から半導体基板の素子領域にかけて設けられ素子領域に接続される第1コンタクトとを備える。第1コンタクトは、素子領域上の層間絶縁膜に形成された素子領域の幅よりも大きい径を有するコンタクトホールと、コンタクトホールの底部に設けられ、素子領域に達する開口を有するスペーサ膜と、スペーサ膜の開口を介して素子領域に接続されるようにコンタクトホール内に埋め込まれたコンタクトプラグとを有する。

(もっと読む)

微細パターンの形成方法

【課題】側壁部の形成の基礎となるパターンをレジストにより形成する場合であっても、側壁部の傾きを抑制できる微細パターンの形成方法を提供する。

【解決手段】基板上に形成されたエッチング対象層の上に有機膜を形成する有機膜形成ステップと、有機膜上にレジスト膜を形成し、このレジスト膜をパターニングするパターニングステップと、パターニングされたレジスト膜から露出する有機膜と、パターニングされたレジスト膜とを覆うように酸化シリコン膜を常温にて堆積する堆積ステップと、基板を加熱して酸化シリコン膜に引っ張り応力を生じさせる加熱ステップと、処理ステップの後に、パターニングされたレジスト膜の側壁に酸化シリコン膜が残るように当該酸化シリコン膜をエッチングする第1のエッチングステップと、パターニングされたレジスト膜を除去する除去ステップとを含む、微細パターンの形成方法が開示される。

(もっと読む)

半導体素子及びその半導体素子のパターン形成方法

【課題】 フォトリソグラフィ工程の解像限界内で、具現可能なサイズのパターンを利用して超微細な幅及び間隔を持つ高密度パターンを形成できる配置構造を持つ半導体素子及びその半導体素子パターン形成方法を提供する。

【解決手段】 半導体素子は、コネクション領域に隣接するメモリセル領域を含む基板、メモリセル領域からコネクション領域まで第1方向に延びて配され、第1ライン幅及び第1ライン間隔を持つ複数の第1導電ライン、第1導電ラインそれぞれに連結されるように配され、第2ライン幅及び第2ライン間隔を持つ複数の第2導電ライン、コネクション領域に配され、第1導電ラインに電気的に連結された複数のパッド、を備える。半導体素子上のパターン形成方法は、微細ライン幅及び間隔を提供するために2段階のスペーサ形成工程を含むことができる。

(もっと読む)

半導体装置

【課題】低抵抗かつ微細化が可能なグラフェン配線を有する半導体装置およびその製造方法を提供する。

【解決手段】一実施の形態によれば、半導体装置は、配線と前記配線に接続されるコンタクトプラグを有する。前記配線は、長さ方向の両側面に触媒層を有する基体と、前記基体の前記両側面上に前記触媒層と接して形成され、前記基体の前記両側面と垂直に積層された複数のグラフェンを有するグラフェン層を有する。

(もっと読む)

カーボンナノチューブ配線の製造方法

【課題】配線構造における電気特性の向上を図る。

【解決手段】カーボンナノチューブ配線の製造方法は、第1導電層200上に、絶縁膜18を形成し、前記絶縁膜内に、前記絶縁膜を貫通するホール40を形成し、前記ホール内の底面の前記第1導電層上および前記ホール内の側面の前記絶縁膜上に、触媒下地膜19を形成し、前記ホール内の側面の前記触媒下地膜上に、触媒不活性膜20を形成し、前記ホール内の底面の前記触媒下地膜上および前記ホール内の側面の前記触媒不活性膜上に、触媒膜21を形成し、前記ホール内の底面の前記触媒膜上から複数のカーボンナノチューブ22を成長させる。

(もっと読む)

121 - 140 / 992

[ Back to top ]