Fターム[5F033QQ31]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチバック (992)

Fターム[5F033QQ31]に分類される特許

141 - 160 / 992

半導体素子用パターン構造物の形成方法

【課題】ラインパターン構造物の形成方法を提供すること。

【解決手段】ラインパターン構造物及びその形成方法において、ラインパターン構造物は切断部位を含むライン形状を有する少なくとも1つの第1ラインパターンを含む。最外郭に位置する前記第1ラインパターンと隣り合って前記第1ラインパターンと平行した延在ラインと、前記第1ラインパターンの切断部位と隣接する領域で前記第1ラインパターン方向へ向かうように前記延在ラインから突出された少なくとも1つの突出パターンを含む2つの第2ラインパターンを含む。前記ラインパターン構造物は不良が減少し、簡単な工程を通じて形成されてもよい。

(もっと読む)

半導体装置及びその製造方法

【課題】ストレッサ膜を有する半導体装置及びその製造方法に関し、ストレッサ膜からの応力を効率よくチャネル領域に印加してMISFETの電流駆動能力を向上しうる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板に、素子領域を画定する素子分離絶縁膜を形成し、素子領域上に、ゲート絶縁膜を介してゲート電極を形成し、ゲート電極の両側の半導体基板内にソース/ドレイン領域を形成し、ゲート電極及びソース/ドレイン領域が形成された半導体基板上に第1の絶縁膜を形成し、素子分離絶縁膜の端部に生じた窪み内に第1の絶縁膜が残存するように第1の絶縁膜をエッチバックし、半導体基板上に、半導体基板の表面に平行な方向に応力を印加する第2の絶縁膜を形成する。

(もっと読む)

半導体装置およびその製法

【課題】トレンチ構造のトランジスタセルがマトリクス状に多数個形成され、そのゲート電極に金属膜からなるゲート配線がコンタクトされる半導体装置でも、ゲート耐圧を充分に高くすることができる構造の半導体装置を提供する。

【解決手段】半導体層1に凹溝11が形成され、その凹溝11内にゲート酸化膜4が形成され、その凹溝11内にポリシリコンなどからなるゲート電極5が設けられるトレンチ構造のトランジスタセルがマトリクス状に配列されたセル領域10を有している。そして、金属膜からなるゲート配線9とコンタクトするため、ゲート電極5と連続してゲートパッド部5aが設けられるが、そのゲートパッド部5aが凹溝11と同時に設けられる凹部12内に形成されている。

(もっと読む)

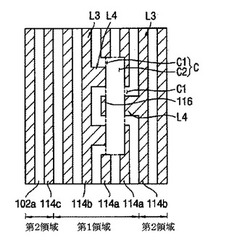

薄膜トランジスタ表示板の製造方法

【課題】エッチング工程時に銅が露出して不純物が発生することを最小化できる薄膜トランジスタ表示板の製造方法を提供する。

【解決手段】絶縁基板の上にゲート線124、ゲート絶縁膜140、第1非晶質シリコン膜154、第2非晶質シリコン膜164、第1金属膜174a、及び第2金属膜174bを順次形成する段階と、第2金属膜174bの上に第1部分と第1部分より厚さの厚い第2部分とを有する感光膜パターン52を形成する段階と、感光膜パターン52をマスクとして第2金属膜174b及び第1金属膜174aをエッチングして、第2金属パターン及び第1金属パターンを形成する段階と、第2金属パターンにSF6気体またはSF6とHeの混合気体で前処理する段階とを含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】接続孔の内壁に絶縁膜を形成することにより、接続孔の径を小さくする場合において、接続孔内に導電膜を十分に埋め込むことができるようにする。

【解決手段】接続孔210,220の内壁上に絶縁性の第1膜300を形成し、接続孔210,220の径を細らせる。次いで、第1膜300が形成された接続孔210,220内に、第2膜50を埋め込む。次いで、絶縁膜200の表層を、CMP法を用いて除去する。次いで、接続孔210,220から第2膜50を除去する。次いで、接続孔210,220の第1膜300上および接続孔210,220の底面上にバリアメタル膜330を形成し、さらに接続孔210,220内に導電膜からなるコンタクト310,320を埋め込む。

(もっと読む)

垂直型トランジスタと埋め込みビットラインとを有する半導体メモリ素子及びその製造方法

【課題】垂直型トランジスタのドレイン領域と埋め込みビットラインとの間に抵抗接点(ohmic contact)を形成しつつも、その製造工程が簡単な半導体メモリ素子及びその製造方法を提供すること。

【解決手段】基板に形成されたトレンチによって上部へ突出した形のアクティブ領域と、アクティブ領域の上部に配置される第1の不純物領域と、アクティブ領域の下部に配置される第2の不純物領域と、第1の不純物領域と第2の不純物領域との間のアクティブ領域の側面に沿って配置されるゲート絶縁膜と、ゲート絶縁膜上に配置されるゲート電極膜と、そして、トレンチの下部でライナー膜によって第2の不純物領域と離隔するように配置される金属膜と、金属膜上で前記第2の不純物領域と直接接触されるように配置されるポリシリコン膜とからなる埋め込みビットラインとを備えることを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】高さのばらつきが低減された埋め込みビット線を有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板内にビット線とワード線を有する半導体装置の製造方法において、半導体基板をエッチングして第1の方向に延在する第1の溝を形成することによって、複数の第1の半導体ピラーを形成する工程と、第1の半導体ピラーの側面の一部に拡散層を形成する工程と、隣接する前記第1の半導体ピラー間の前記第1の溝に、拡散層に接続するビット線を形成する工程と、第1の半導体ピラーと前記ビット線を覆う第1の絶縁膜を形成する工程と、第1の半導体ピラーの少なくとも一部が露出するように前記第1の絶縁膜に、第1の方向に直交する第2の方向に延在する第2の溝を形成する工程と、露出した第1の半導体ピラー上にエピタキシャル層を成長させて第2の半導体ピラーを形成する工程と、を有することを特徴とする。

(もっと読む)

半導体装置

【課題】ゲートコンタクトプラグ形成のためのコンタクトホールの深さを適切に制御可能とする。

【解決手段】半導体装置1は、活性領域ARを囲む第1の絶縁体ピラー21と、第1の絶縁体ピラー21の活性領域AR側の側面21sとy方向に相対向する側面22sを有する第2の絶縁体ピラー22と、第1及び第2の絶縁体ピラー21,22の上面を覆う絶縁膜31と、第1のゲート電極16と電気的に接続し、かつ少なくとも側面21s,22sを覆う第2のゲート電極23と、底面に絶縁膜31及び第2のゲート電極23が露出したコンタクトホールの内部に設けられ、かつ第2のゲート電極23の上面と電気的に接続するゲートコンタクトプラグ42とを備え、側面21s,22s間の距離は、ゲートコンタクトプラグ42のx方向の長さより短く、ゲートコンタクトプラグ42は側面21s,22s間の領域で第2のゲート電極23と電気的に接続する。

(もっと読む)

半導体装置及びその製造方法

【課題】ダイシング等で半導体装置を個片化する際に加工のダメージ又は膜の残留応力などに起因して発生する、基板上の膜の剥離を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置101,102の周辺すなわち個片化のための加工ラインの近傍の基板1上に溝6を形成する。その溝の内部では基板上に成膜される薄膜が少なくとも1部で不連続となることにより、万一、半導体装置の端部から膜剥がれが発生したとしても、この溝部でその進行を阻止する。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】CMOS回路を構成するnチャネルMISFETとpチャネルMISFETの両者において、キャリア移動度を高めて高い性能を実現する半導体装置を提供する。

【解決手段】半導体基板の第1領域及び第2領域において第1ゲート絶縁膜及び第1ゲート電極(16,17)を形成し、第1ゲート電極の両側部における半導体基板中にソースドレイン領域を形成し、ソースドレイン領域の導電性不純物を活性化し、第1ゲート電極を被覆して全面に半導体基板に応力を印加するストレスライナー膜(27,28)を形成し、少なくとも第1領域に形成された部分のストレスライナー膜は残しながら第2領域における第1ゲート電極の上部部分のストレスライナー膜を除去し、第2領域における第1ゲート電極の上部を露出させて第1ゲート電極を全て除去して第2ゲート電極形成用溝Tを形成し、第2ゲート電極形成用溝内に第2ゲート電極(31,32)を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】下層の金属配線のダメージがなく上層の金属配線が形成され、かつ、配線間の寄生容量が低減された半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板上に設けられた第1の金属配線層と、

前記第1の金属配線層上に設けられ、該第1の金属配線層の金属の拡散を防止する拡散防止膜と、前記拡散防止膜上に設けられた第1の絶縁膜と、前記第1の絶縁膜上に設けられた、前記拡散防止膜と同じ材料からなる第2の絶縁膜と、前記第2の絶縁膜上に設けられた第3の絶縁膜と、前記拡散防止膜、前記第1の絶縁膜、前記第2の絶縁膜及び前記第3の絶縁膜に形成された接続孔に充填され、前記第1の金属配線層に電気的に接続された第2の金属配線層と、を備えたことを特徴とする。

(もっと読む)

絶縁パターン形成方法及びダマシンプロセス用絶縁パターン形成材料

【課題】 煩雑なエッチング工程等を施すことなく、簡便に多層構造が形成できる、絶縁パターン形成方法及び樹脂組成物を提供すること。

【解決手段】 〔I〕基板上に有機パターンを形成する工程と、

〔II〕前記有機パターンのパターン間に絶縁材料を埋め込む工程と、

〔III〕前記有機パターンを除去し、前記絶縁材料からなる反転パターンを得る工程と、

〔IV〕得られた反転パターンを硬化させる工程と、

を有することを特徴とする、絶縁パターン形成方法と、ダマシンプロセス用絶縁パターン形成材料を提供する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明ではフォトリソグラフィー技術解像限界付近のパターン形成を安定して形成すると共に、コンタクトプラグなどの構造物における目合わせずれや接触面積の縮小による接触電気抵抗の増大や接続不良を解決する。

【解決手段】半導体基板上に形成された絶縁材料層100に、第1の方向に延在し、底部の幅W1より上部の幅W2が広い第1の溝101を形成する工程と、第1の溝101内に、溝の上端より低い位置まで埋め込み層102を形成する工程と、埋め込み層102上に露出している第1の溝101の側壁を覆うサイドウォール103を形成する工程と、サイドウォール103をマスクとして埋め込み層102をエッチングして第1の方向に分離する工程と、

を含むことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタの特性を劣化させることなくポリシリコン抵抗素子を製造できる半導体装置の製造方法を提供する。

【解決手段】半導体基板30の抵抗素子形成領域に抵抗素子となるポリシリコン膜35aを形成するとともに、トランジスタ形成領域にポリシリコンゲート35b及び高濃度不純物領域40を形成する。その後、全面に絶縁膜41を形成した後、トランジスタ形成領域をフォトレジスト膜42で覆い、ポリシリコン膜35aに導電性不純物をイオン注入する。次いで、フォトレジスト膜42をアッシングにより除去する。このとき、トランジスタは絶縁膜41に覆われているため、アッシングによるダメージが回避される。また、抵抗素子領域に導入された導電性不純物が大気中のO及びHと反応して酸が発生しても、ポリシリコンゲート及び高濃度不純物領域40が酸により溶解することが回避される。

(もっと読む)

半導体装置の製造方法

【課題】ビット線材料埋設体の形状のばらつきに起因するビット線の配線抵抗値のばらつきを防ぐ半導体装置の製造方法を提供する。

【解決手段】製造方法は、第一溝4内に第一のビット線材料埋設体6および第二のビット線材料埋設体10からなるビット線11を形成する第一工程と、ビット線11に含まれる不純物を拡散させて第一不純物拡散領域13を形成する第二工程と、ピラー部1bを形成する第三工程と、ピラー部1bに対向する配線17を第二溝15内に形成する第四工程と、ピラー部1bの先端部に、第二不純物拡散領域19を形成する第五工程と、を具備し、第一工程が、第一溝4を完全に埋め込むように第一ビット線材料を形成した後に第一ビット線材料表面を平坦化し、第一溝4底部に残るように第一ビット線材料をエッチバックする工程を具備する。

(もっと読む)

半導体装置の製造方法

【課題】安定した形状の信頼性の高いエアギャップを効率良く形成する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、半導体基板上に、ビアホール及びエアギャップ用トレンチを含む複数のホールを有する層間絶縁膜を形成する。次に、エアギャップ用トレンチ内に有機材料を埋め込んだ後、硬化させる。また、ビアホール内にビアプラグを形成する。この後、エアギャップ用トレンチ内に埋め込まれた有機材料を除去することにより、エアギャップを形成する。

(もっと読む)

埋め込みビットラインを備えた半導体装置およびその製造方法

【課題】埋め込みビットラインと接合を安定的にコンタクトさせることができ、埋め込みビットラインとコンタクトされる接合の深さを均一に形成できる半導体装置およびその製造方法を提供する。

【解決手段】本発明の半導体装置製造方法は、基板をエッチングして何れか1つの側壁がステアを有するトレンチを形成するステップと、前記ステアの表面下部に接合部を形成するステップと、前記接合部とコンタクトされる埋め込みビットラインを形成するステップと、を含むことを特徴とする。本発明は、垂直セル構造の埋め込みビットライン製造時に使用されるマスクの個数を顕著に減少させることができ、工程ステップを減少させ、行うことができるため工程の単純化および工程難易度、原価節減の側面で非常に有利である。

(もっと読む)

半導体装置およびその製造方法

【課題】SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を向上させる。また、半導体装置の製造工程を簡略化する。

【解決手段】SOI基板SB上に形成された複数のnチャネル型MOSFETQnを有する半導体装置において、BOX膜の下部の支持基板の上面に拡散層であるn+型半導体領域を形成し、n+型半導体領域と電気的に接続され、素子分離領域1を貫くコンタクトプラグCT2を形成することで、支持基板の電位を制御する。SOI基板SBの平面において、各nチャネル型MOSFETQnは第1方向に延在しており、第1方向に複数形成されて隣り合うコンタクトプラグCT2同士の間に配置された構造とする。

(もっと読む)

固体撮像装置およびその製造方法

【課題】高速動作に有利な固体撮像装置およびその製造方法を提供する。

【解決手段】固体撮像装置は、多層配線層73と、前記多層配線層上に設けられ、貫通トレンチを有する半導体層64と、前記貫通トレンチ内部に埋め込まれた第1導電層69と、前記第1導電層の周囲に形成された第1絶縁膜32と、前記第1絶縁膜の周囲に形成された第1導電型の第1不純物拡散層36とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】どのようなレイアウトの配線に対しても、個々の配線ごとにエアギャップ部を設ける。エアギャップ部によって、配線の寄生容量を低減する。

【解決手段】半導体装置は、層間絶縁膜と、層間絶縁膜内に埋め込まれた配線と、配線の側面と層間絶縁膜との間に設けられたエアギャップ部と、を有する。半導体装置の製造方法は、配線の側面上に第2のサイドウォール膜を形成した後、第2のサイドウォール膜の一部が露出するように第1の絶縁膜を形成する。次に、第2のサイドウォール膜を除去することによりサイドスペースを形成した後、サイドスペースが埋め込まれないように第2の絶縁膜を形成することによりサイドスペースから構成されるエアギャップ部を形成する。

(もっと読む)

141 - 160 / 992

[ Back to top ]