Fターム[5F033QQ31]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチバック (992)

Fターム[5F033QQ31]に分類される特許

161 - 180 / 992

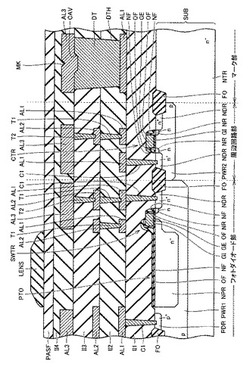

半導体装置およびその製造方法

【課題】層間絶縁膜などの積層構造を低背化しつつ、アライメント用のマークが容易に形成された半導体装置、およびその製造方法を提供する。

【解決手段】半導体基板SUBに形成された光電変換素子PTOと、マーク部のストッパ膜AL1と、ストッパ膜AL1上および光電変換素子PTO上に形成された第1の層間絶縁膜II2と、第1の金属配線AL2と、第2の層間絶縁膜II3とを備える。層間絶縁膜II2、II3を貫通してストッパ膜AL1に達するスルーホールDTHが形成され、スルーホールDTH内の導電層DTの上面に第1の凹部CAVが形成される。第1の凹部CAVの上面の第2の金属配線AL3に、アライメントマークとなる第2の凹部MKを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】どのようなレイアウトの配線に対しても、個々の配線ごとにエアギャップ部を設ける。エアギャップ部によって、配線の寄生容量を低減する。

【解決手段】半導体装置は、層間絶縁膜と、層間絶縁膜内に埋め込まれた配線と、配線の側面と層間絶縁膜との間に設けられたエアギャップ部と、を有する。半導体装置の製造方法は、配線の側面上に第2のサイドウォール膜を形成した後、第2のサイドウォール膜の一部が露出するように第1の絶縁膜を形成する。次に、第2のサイドウォール膜を除去することによりサイドスペースを形成した後、サイドスペースが埋め込まれないように第2の絶縁膜を形成することによりサイドスペースから構成されるエアギャップ部を形成する。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の向上に寄与し得る半導体装置の製造方法を提供する。

【解決手段】半導体基板10にトランジスタ36を形成する工程と、半導体基板上に、トランジスタを覆う第1のシリコン窒化膜38を形成する工程と、第1のシリコン窒化膜にNH4Fラジカルを供給する工程と、NH4Fラジカルを供給する工程の後、第1のシリコン窒化膜に対して熱処理を行う工程と、熱処理を行う工程の後、第1のシリコン窒化膜上に第2のシリコン窒化膜を形成する工程とを有している。

(もっと読む)

空隙組込みの構造体及び方法

【課題】 空隙を組み込んだ構造体及びその形成方法を提供する。

【解決手段】 VLSI及びULSI用の空隙含有金属・絶縁体相互接続構造体を、光パターン化可能低k材料を用いて作成する方法、及び形成した空隙含有金属・絶縁体相互接続構造体を開示する。より具体的には、本明細書で説明する方法は、内部に種々異なる深さの空隙がフォトリソグラフィにより画定された光パターン化可能低k材料の内部に構築される相互接続構造体を提供する。本発明の方法においては、空隙を形成するのにエッチ・ステップは必要としない。光パターン化可能低k材料内部の空隙を形成するのに、エッチ・ステップを必要としないで、本発明において開示する方法は、高信頼性の相互接続構造体を提供する。

(もっと読む)

半導体装置の製造方法

【課題】サイドウォールスペーサを利用してリソグラフィー解像限界未満のパターンと任意の寸法のパターンとが混在するパターンを形成する。

【解決手段】アモルファスカーボン膜3及びシリコン酸窒化膜4からなる被エッチング部材上に塗布膜5をスピン塗布法により成膜し、塗布膜5をパターニングすることによってサイドウォールコアを形成し、サイドウォールコアの少なくとも側面を覆うシリコン酸化膜7を成膜し、シリコン酸化膜7上に有機反射防止膜8をスピン塗布法により成膜する。次いで、有機反射防止膜8をエッチングすることによって、シリコン酸化膜7の凹部7aを覆う埋込マスクを形成し、シリコン酸化膜7をエッチングすることにより、サイドウォールコアまたは埋込マスクと重ならない被エッチング部材を露出させ、被エッチング部材をエッチングすることでフォトリソグラフィー解像限界未満のパターンを得る。

(もっと読む)

他の素子の処理の間のメモリセルの活性層の保護

【課題】メモリ構造に対して損傷を与えることを防止しながら選択された導電体から表面酸化物を適切に除去する。

【解決手段】導電層(102)を設け、その導電層(102)を覆うように誘電体(100)を設け、その誘電体(100)を貫通する第1および第2の開口(104,106)を設け、第1および第2の開口(104,106)内にそれぞれ第1および第2の導電体(108,110)を設けかつ第1および第2の導電体(108,110)を導電層(102)に接触させ、その第1の導電体(108)を覆うようにメモリ構造(126)を設け、そのメモリ構造(126)を覆うように保護要素(134)を設け、その第2の導電体(110)上に処理を施すことによる電子構造の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】吸湿性の高い絶縁膜を使用してもコンタクト又は配線の劣化を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板10上に第1の絶縁膜15を形成する工程(a)と、第1の絶縁膜15にホール24を形成する工程(b)と、ホール24の側壁上に、第1の絶縁膜15よりも水分を通しにくい第2の絶縁膜17を形成する工程(c)と、工程(c)の後、ホール24に導電体30を埋め込むことにより、プラグ19を形成する工程(d)とを備えている。

(もっと読む)

半導体装置の製造方法

【課題】キャパシタの誘電体膜を構成する強誘電体又は高誘電体の結晶性が良好であり、キャパシタのスイッチング電荷量が高く、低電圧動作が可能で信頼性が高い半導体装置及びその製造方法を提供すること。

【解決手段】半導体基板110にトランジスタT1、T2を形成した後、ストッパ層120及び層間絶縁膜121を形成する。そして、層間絶縁膜121にコンタクトホールを形成し、層間絶縁膜121上に銅膜を形成してコンタクトホール内に銅を埋め込む。その後、低圧CMP研磨又はECMP研磨により層間絶縁膜121上の銅膜を除去して表面を平坦化し、プラグ124a,124bを形成する。次いで、バリアメタル125、下部電極126a、強誘電体膜127及び上部電極128aを形成する。このようにして、強誘電体キャパシタ130を有する半導体装置(FeRAM)が形成される。

(もっと読む)

半導体装置

【課題】半導体装置の性能を向上させる。また、半導体装置の信頼性を確保する。また、半導体装置のチップサイズの縮小を図る。特に、SOI基板上に形成されたMOSFETを有する半導体装置の信頼性を損なわずにゲート電極の下部のウエルの電位を制御し、寄生容量の発生を防ぐ。また、MOSFETにおける欠陥の発生を防ぐ。

【解決手段】ゲート電極配線3に形成された孔部27内を通るウエルコンタクトプラグ8により、ゲート電極2の下部のウエルの電位を制御することで寄生容量の発生を防ぐ。また、ゲート電極2に沿って素子分離領域4を延在させることで、ゲッタリング効果によりゲート絶縁膜における欠陥の発生を防ぐ。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】電極パッドのプローブ領域とボンディング領域とを、光学顕微鏡による拡大観察で明確に識別することができる半導体装置を提供する。

【解決手段】半導体基板に形成された回路と接続される下層メタル配線20と、下層メタル配線20の上に形成され、複数のビアホール35、36を有する層間絶縁膜30と、複数のビアホール35、36を埋める複数の配線部40と、層間絶縁膜30及び複数の配線部40の上に形成され、複数の配線部40を介して下層メタル配線20と電気的に接続する上層メタル配線50とを具備する。層間絶縁膜30は、複数の第1ビアホール35を有する第1絶縁部31と、複数の第2ビアホール36を有する第2絶縁部32と、第1絶縁部31と第2絶縁部32との間に位置し、上面が平らな第3絶縁部33とを備える。

(もっと読む)

半導体装置の製造方法

【課題】複数の顧客による各々異なるLSIが共同で作製された基板を、守秘性が得られた状態で各々の顧客に提供できるようにする。

【解決手段】特定の顧客への提供対象とするLSIチップ領域331以外の領域が開放した開口部307aを備えるマスクパターン307を形成する。次に、マスクパターン307をマスクとし、開口部307に露出しているLSIチップ領域332をエッチング除去し、ブラインド領域301aを形成する。ブラインド領域301aの形成では、第1配線層302,第2配線層303,および第3配線層304を除去し、これらの下層の一部までを除去する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線の信頼性の高い半導体装置を提供する。

【解決手段】半導体基板42上に台形状の凸部領域と台形状の凹部領域を設け、凹部領域のシリコン表面にはゲート酸化膜45が設けられ、ゲート酸化膜上にはゲート電極46が形成されている。凹部領域に設けられたゲート電極46の両側の凸部領域にはソース・ドレイン高濃度領域48が位置し、ソース・ドレイン高濃度領域48とゲート電極46の間にはソース・ドレイン低濃度領域47が形成されている。ソース・ドレイン高濃度領域48の上表面には第1層目の金属配線49と第2層目の金属配線50と第3層目の金属配線52が積層され、ソース・ドレイン高濃度領域48から第3金属配線までの接続にコンタクトホールやビアホールなどを利用していない。このように本発明の半導体装置は、コンタクトホールやビアホールなどの接続孔を形成しないで素子と配線との接続や配線間接続を行なうことができる。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、簡素な製造工程でありながら、ボイドを発生させずにトランジスタセルの高密度化を実現する半導体装置の製造方法を提供することを目的とする。

【解決手段】半導体層60にトレンチ型のゲート90が形成され、該ゲート90の両側に拡散層50が形成されたトランジスタセルを複数含むセル部61と、該セル部61を囲むガードリング部62とを有する半導体装置の製造方法であって、

前記ゲート90及び前記拡散層50が形成された前記半導体層60の表面に、層間絶縁膜120を形成する工程と、

前記セル部61に形成された前記層間絶縁膜120を、エッチバックにより薄膜化する工程と、

前記層間絶縁膜120の前記拡散層50上の位置に、孔状又は溝状のコンタクト部130を形成する工程と、

前記層間絶縁膜120上に、金属膜140を形成する工程と、を含むことを特徴とする。

(もっと読む)

半導体装置、半導体装置の製造方法、半導体装置の設計方法、及び電子機器

【課題】積層される半導体ウェハのそれぞれの性能を十分に発揮して高性能化を図り、且つ量産性、コスト低減を図った、固体撮像装置等の半導体装置とその製造方法を提供する。また、固体撮像装置を備えたカメラ等の電子機器を提供する。

【解決手段】第1の半導体ウェハ31と、第2の半導体ウェハ45とを、基板間配線68で接続する構成とする。基板間配線は、第1の半導体ウェハ31表面の第1の多層配線層に形成される接続孔66と、第2の半導体ウェハ45表面の第2の多層配線層に形成された貫通接続孔65とに、導電材料が埋め込まれて形成されている。そして、貫通接続孔65は接続孔66の直径よりも大きく形成されている。これにより、貫通接続孔65の構内に導電材料を埋め込む際のボイドの発生を防ぐ。

(もっと読む)

光電変換装置及びその製造方法

【課題】 層間絶縁膜の厚膜化を抑制しつつ、周辺回路領域の配線層数を増加させることのできる光電変換装置を提供する。

【解決手段】 画素領域と、画素領域よりも多くの配線層を有する周辺回路領域とが配された半導体基板と、半導体基板の上部に配された配線部とを有する光電変換装置において、配線部は、第1の配線層と接続する第1の層間絶縁膜に配されたプラグを周辺回路領域に有し、第1の配線層よりも上部に配された第2の配線層と接続する第1の層間絶縁膜に配されたプラグと第2の層間絶縁膜に配されたプラグとを画素領域に有し、

半導体基板に最も近接して配された配線層は、周辺回路領域において第1の配線層であり、画素領域において第2の配線層である。

(もっと読む)

半導体装置及びその製造方法

【課題】深さの異なるコンタクトホールを同時に形成することを可能とした半導体装置を提供する。

【解決手段】第1の溝部7内に形成された第1の埋め込み配線11と、第2の溝部12内に形成された第2の埋め込み配線14と、第1の埋め込み配線11上に第1のコンタクトプラグ24が形成される第1のコンタクト形成領域23と、第2の埋め込み配線14上に第2のコンタクトプラグ26が形成される第2のコンタクト形成領域25とを備え、第1のコンタクト形成領域23の上面23aが第1の埋め込み配線11の上面11aよりも高い位置にあり、第2のコンタクト形成領域25の上面25aが第2の埋め込み配線14の上面14aと同じかそれよりも高い位置にあり、第1のコンタクト形成領域23の上面23aが第2のコンタクト形成領域25の上面25aと同じかそれよりも高い位置にある。

(もっと読む)

半導体装置及びその製造方法

【課題】N型トランジスタ及びP型トランジスタの双方で可及的に製造工程を共通にして、工程数の可及的な削減を図るも、N型トランジスタ及びP型トランジスタの夫々に適合した応力を適宜印加し、トランジスタ性能の大幅な向上を実現する。

【解決手段】N型トランジスタでは、ゲート電極14a及びサイドウォール絶縁膜17を覆うようにN型領域10aの全面に引張応力膜22を形成し、P型トランジスタでは、サイドウォール17絶縁膜上のみに引張応力膜22を形成し、更にゲート電極14b及び引張応力膜22を覆うようにP型領域10bの全面に圧縮応力膜24を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】GaN系HEMT及びMIMキャパシタを同一基板上に設ける場合でも小型化することができる半導体装置及びその製造方法を提供する。

【解決手段】基板1の表面上に下部電極11を形成し、下部電極11上に誘電体膜12を形成し、誘電体膜12上に基板1の表面に接する上部電極14aを形成する。また、基板1の裏面から基板1をエッチングすることにより、上部電極14aの基板1の表面に接する部分に達するビアホール1aを基板1に形成し、基板1の裏面上にビアホール1aを介して上部電極14aに接するビア配線36を形成する。

(もっと読む)

半導体装置

【課題】小型化が可能な半導体装置を提供する。

【解決手段】半導体装置において、第1の導電性材料からなる第1のコンタクトと、第2の導電性材料からなり、下端部が第1のコンタクトの上端部に接続された第2のコンタクトと、第3の導電性材料からなり、下面が第1のコンタクトの下面よりも上方に位置し、上面が第2のコンタクトの上面よりも下方に位置し、第1及び第2のコンタクトから離隔した中間配線と、を設ける。そして、第2の導電性材料に対する第1の導電性材料の拡散係数は、第2の導電性材料に対する第3の導電性材料の拡散係数よりも小さい。

(もっと読む)

半導体装置の製造方法

【課題】配線とコンタクトプラグの短絡を効果的に防止する。

【解決手段】半導体装置の製造方法は、隣り合う配線の間に位置する層間絶縁膜内に、配線が露出した第1のコンタクトホールを含む複数のコンタクトホールを形成する。次に、(i)配線の露出した側面が、第1のコンタクトホールの第1の絶縁膜から構成される内壁側面と実質的に同一面となるか、又は(ii)第1のコンタクトホールの内壁側面において配線の露出した側面が窪んだ凹形状が形成されるように、露出した前記配線の一部を除去する。この後、コンタクトホールの内壁側面上にサイドウォール膜を形成後、コンタクトホール内に導電材料を充填することによりコンタクトプラグを形成する。

(もっと読む)

161 - 180 / 992

[ Back to top ]