Fターム[5F033QQ31]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチバック (992)

Fターム[5F033QQ31]に分類される特許

41 - 60 / 992

半導体装置及びその製造方法

【課題】高品質な配線を有する半導体装置を提供する。

【解決手段】第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域に設けられた第1の絶縁層上に形成された第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層上に形成され、第2の絶縁層と略同一の高さを有する第3の絶縁層11cと、第1の領域に設けられた第1の絶縁層上及び第2の絶縁層の両方の側壁に形成された第1の配線層13aと、第2の領域に設けられた第1の絶縁層上、及び第3の絶縁層の上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層、第2の絶縁層、第1の配線層、及び第2の配線層を覆う第4の絶縁層15と、第1の領域に設けられた第4の絶縁層内に形成され、第1の配線層に接続された第1のコンタクトプラグ17aと、第2の領域に設けられた第4の絶縁層内に形成され、第2の配線層に接続された第2のコンタクトプラグ17bと、を備える。

(もっと読む)

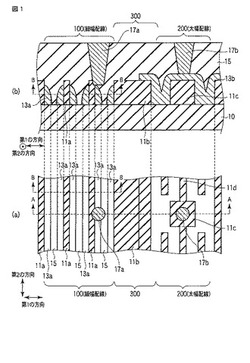

半導体装置およびその製造方法

【課題】トランジスタ間接続配線が吊りワード線と短絡してしまうのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置するピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央の位置で、第1の方向(X)へ延在して配置された吊りワード線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつ吊りワード線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板における抵抗やコンタクト抵抗を低減させた半導体装置及びその製造方法を提供すること。

【解決手段】半導体装置は、シリコン層と、シリコン層に形成され、第1不純物を含有する金属シリサイド層と、を備える。シリコン層は、金属シリサイド層が形成されていない領域において、第1不純物に起因するエンド・オブ・レンジ欠陥を有していない。

(もっと読む)

半導体装置の製造方法

【課題】本願発明者らが、プラズマ処理等による半導体ウエハのチャージアップの影響を検討したところによると、半導体ウエハ等にドライエッチング等を施すと、通常、その結果として、半導体ウエハは、主に電気的に正側に偏った不均一な帯電状態となることが明らかとなった。これは、ドライエッチング等によって、正の可動イオン等がウエハの表面やその近傍に残存し、不均一に分布していることを示すものであり、個々の半導体チップとされた後も残存して、動作に悪影響を及ぼす恐れがある。

【解決手段】本願発明は、通常、ポリマー除去液等を使用する必要のないメタル膜加工工程に於いて、加工用レジスト膜の除去後、ポリマー除去液類似の導電性処理液との摩擦により、ウエハ全体を負に帯電させるものである。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、コンタクトプラグが形成されるセル部と、前記コンタクトプラグが形成されない周辺回路部とを平坦化できる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に最上部が第1の絶縁膜からなる配線層を形成する工程と、

前記半導体基板と前記配線層とを被う第2の絶縁膜を形成する工程と、前記第2の絶縁膜の所定の領域をエッチングし、前記配線層と前記半導体基板とを露出させる開口部を形成する工程と、前記開口部内と前記第2の絶縁膜上とに導電膜を形成する工程と、前記第1の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有し、前記第2の絶縁膜の研磨速度が前記導電膜に対する研磨速度よりも大きい選択比を有する条件で、前記第2の絶縁膜と前記導電膜とを前記第1の絶縁膜が露出するようCMP法で除去し、コンタクトプラグを形成する工程を有する半導体装置の製造方法。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1のnMIS形成領域1Aにnチャネル型MISFETQnを、半導体基板1のpMIS形成領域1Bにpチャネル型MISFETQpを、それぞれ形成してから、nチャネル型MISFETQnおよびpチャネル型MISFETQpを覆うように引張応力の窒化シリコン膜5を形成し、nMIS形成領域1AおよびpMIS形成領域1Bの窒化シリコン膜5に紫外線照射処理を施す。その後、nMIS形成領域1Aの窒化シリコン膜5を覆いかつpMIS形成領域1Bの窒化シリコン膜5を露出するマスク層6aを形成してから、pMIS形成領域1Bの窒化シリコン膜5をプラズマ処理することで、pMIS形成領域1Bの窒化シリコン膜5の引張応力を緩和させる。

(もっと読む)

薄膜トランジスタ表示板及びその製造方法

【課題】酸化物半導体を使用する薄膜トランジスタの特性を向上させることができる薄膜トランジスタ表示板及びその製造方法を提供する。

【解決手段】薄膜トランジスタ表示板を提供する。本発明の一実施形態に係る薄膜トランジスタ表示板は、基板の上に配置するゲート配線層、前記ゲート配線層の上に配置する酸化物半導体層、及び前記酸化物半導体層の上に配置して、前記ゲート配線層と交差するデータ配線層を含み、前記データ配線層は銅を含む主配線層、及び前記主配線層の上に配置して、銅合金を含むキャッピング層を含む。

(もっと読む)

半導体装置の製造方法

【課題】埋込ワード線の高さにばらつきのない半導体装置の製造方法を提供する。

【解決手段】本発明の半導体装置の製造方法は、複数の素子分離領域を形成すると共に、素子分離領域間に素子形成領域を形成する工程と、素子形成領域に交差する第1の方向に延在するゲート電極溝を形成する工程と、ゲート電極溝の内壁にゲート絶縁膜を形成する工程と、ゲート電極溝の内壁にゲート絶縁膜を介して第1導電膜を形成する工程と、ゲート電極溝内を埋め込むように第2導電膜を形成する工程と、第2導電膜上に平坦化膜を形成する工程と、第2導電膜が露出するように平坦化膜をエッチングして除去する第1のエッチング工程と、第2導電膜がゲート電極溝の下部に残留するように第2導電膜をエッチングする第2のエッチング工程と、第1導電膜が前記ゲート電極溝の下部に残留するように第1導電膜をエッチングする第3のエッチング工程と、を有することを特徴とする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】大電流を流す第1ビアおよび第1配線を有し、且つ、当該第1ビアおよび第1配線が形成された第1面が平坦な半導体装置を提供する。

【解決手段】第1基板100と、第1基板100の第1面側から、当該第1基板100を貫通する第1ビア420と、第1基板100の第1面に埋設され、少なくとも一つ以上の第1ビア420の一端と接続する第1配線440と、を備えている。また、第1ビア420は、当該第1ビア420の側面と当該第1ビア420の底面とのなす角θ1が、第1配線440の側面と第1配線440の底面とのなす角θ2より大きい傾斜部を有している。

(もっと読む)

半導体装置

【課題】浮遊状態の配線と洗浄水との間において高い密度で電荷が移動することに起因する配線の高抵抗化を防ぐ。

【解決手段】半導体製造装置の製造工程中において、半導体基板1Sなどと絶縁された浮遊状態となる銅配線である第1層配線L1の上面に、電気的に機能する接続ビアPL2と電気的に機能しないダミービアDP2とを接続させて形成する。これにより、第1層配線L1の上面に接続ビアPL2を形成するためのビアホールを形成した後の洗浄工程中に、第1層配線L1に溜まった電荷が洗浄水中に移動する際、前記電荷をダミービアDP2形成用のビアホールにも分散させることで、接続ビアPL2形成用のビアホールの底部のみに前記電荷が集中することを防ぐ。

(もっと読む)

半導体装置

【課題】チャネル形成領域に対しトランジスタの電流駆動能力を向上させる方向に応力をかけ、さらに電流駆動能力が向上し、性能が向上された半導体装置を提供する。

【解決手段】半導体基板1aの活性領域1cが素子分離絶縁膜2で区画され、チャネル形成領域、ゲート絶縁膜、ゲート電極8a、ソース・ドレイン領域及び被覆応力膜を有するNTrを有し、ソース・ドレイン領域の両側部に位置する素子分離絶縁膜2aの表面は、ソース・ドレイン領域の表面より低い位置に形成されており、ゲート電極8a、活性領域1c、及び表面がソース・ドレイン領域の表面より低い位置に形成された素子分離絶縁膜2aを被覆して、チャネル形成領域に対し引張応力を印加する被覆応力膜が形成されている構成とする。

(もっと読む)

半導体装置およびその製造方法

【課題】活性領域における上記プラグと、活性領域の外部における上記プラグとの双方を有する、微細化された半導体装置において、枠付け絶縁膜を確実に形成し、かつ導電性などの機能を最適化することが可能な半導体装置を提供する。

【解決手段】主表面を有する半導体基板SUBと、半導体基板SUBの主表面上に形成される活性領域と、平面視における活性領域の周辺に形成されるゲート接続領域と、活性領域上に形成される複数の第1のトランジスタTGに挟まれる領域に形成される、第1のトランジスタTGと第1のトランジスタTGよりも上側の層とを電気的に接続するための第1の接続層CTと、ゲート接続領域上に形成される第2のトランジスタTGと、第2のトランジスタTGよりも上側の層とを電気的に接続するための第2の接続層とを備えている。上記第1の接続層CTには第1の導電部PP1aと第2の導電部PP2aとを含み、第2の接続層SNCには第3の導電部PP2bを含む。

(もっと読む)

抵抗変化メモリ及びその製造方法

【課題】抵抗変化メモリの製造プロセスにおけるPEP数を削減する。

【解決手段】実施形態に係わる抵抗変化メモリは、第1の方向及びこれに直交する第2の方向にそれぞれ交互に配置される複数の抵抗変化素子MTJ及び複数のビアV0と、複数の抵抗変化素子MTJの側壁上に配置される複数の側壁絶縁層PLとを備える。複数の抵抗変化素子MTJは、一定ピッチで格子状に配置され、複数の側壁絶縁層PLの側壁に垂直な方向の厚さは、複数の側壁絶縁層PLが互いに部分的に接触し、複数の側壁絶縁層PL間に複数のホールが形成される値に設定される。複数のビアV0は、これら複数のホール内に配置される。

(もっと読む)

半導体装置、半導体装置の製造方法、及び電子装置

【課題】縦型トランジスタのTDDB耐性を向上させ、かつ、閾値電圧がばらつくことも抑制する。

【解決手段】ゲート電極120の上端は、半導体基板100の表面よりも下に位置している。絶縁層340は、ゲート電極120上及びその周囲に位置する半導体基板100上に形成されている。絶縁層340は、第1絶縁膜342及び低酸素透過性絶縁膜344を有している。第1絶縁膜342は、例えばNSG膜であり、低酸素透過性絶縁膜344は、例えばSiN膜である。さらに、低酸素透過性絶縁膜344上には、第2絶縁膜346が形成されている。第2絶縁膜346は、例えばBPSG膜である。絶縁層340を形成した後、酸化雰囲気で処理することにより、縦型MOSトランジスタ20のTDDB耐性が向上する。また、絶縁層340が低酸素透過性絶縁膜344を有することにより、縦型MOSトランジスタ20の閾値電圧がばらつくことを抑制できる。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】携帯電話などに使用されるハイパワーアンプの出力段は、多数のLDMOSFETセルを集積し、通常、複数のLDMOSFETを構成するLDMOSFET部を有する。このLDMOSFETセルにおいては、裏面のソース電極と表面のソース領域との間の抵抗を低減するために、半導体基板に高濃度にボロンドープされたポリシリコンプラグが埋め込まれている。本願発明者らが、このポリシリコンプラグについて、検討したところによって、熱処理に起因してポリシリコンプラグの固相エピタキシャル成長により、ポリシリコンプラグが収縮し、それによってシリコン基板に歪が発生し、リーク不良等の原因となることが明らかとなった。

【解決手段】本願発明は、LDMOSFETを有する半導体集積回路装置において、半導体基板に埋め込まれたシリコン系導電プラグのボロン濃度が、固溶限界内に於いて、8.1x1020atom/cm3以上である。

(もっと読む)

金属エッチング用組成物、および金属エッチング用組成物を用いた半導体装置の製造方法

【課題】基板に含まれる珪素系材料に対してダメージを与えることなく、常温で高速に長時間安定してタングステン系金属を除去することができるエッチング用組成物を提供する。

【解決手段】本発明の金属エッチング用組成物は、過硫酸塩の添加量が8〜30質量%、塩基性化合物の添加量が1〜15質量%、となるように配合された、フッ素含有化合物を含まない25℃でのpHが8以上の水溶液であることを特徴とする。過酸化水素をさらに添加することによりタングステン系金属とチタン系金属の積層膜あるいは合金膜の除去に適用することができる。他方、過酸化水素を無添加とすることにより、チタン系金属に優先してタングステン系金属を選択的に除去することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】縦型トランジスタの特性にばらつきが生じることを抑制する。

【解決手段】半導体基板100には縦型MOSトランジスタ20が形成されている。半導体基板100の表面上には、第1層間絶縁膜300及び第1ソース配線312が形成されている。第1ソース配線312は、第1層間絶縁膜300上に形成されており、平面視で縦型MOSトランジスタ20と重なっている。第1層間絶縁膜300にはコンタクト302が埋め込まれている。コンタクト302は、縦型MOSトランジスタ20のn型ソース層140と第1ソース配線312とを接続している。そして第1ソース配線312には、複数の開口316が形成されている。

(もっと読む)

電気光学装置の製造方法

【課題】層間絶縁膜のコンタクトホールの内部にコンタクト用導電膜および埋め込み膜を設けた場合でも、コンタクトホールの外部で画素電極とコンタクト用導電膜とを確実に導通させることができる電気光学装置の製造方法を提供すること。

【解決手段】電気光学装置100を製造するにあたって、層間絶縁膜45上にコンタクトホール45aの底部45eおよび内壁45fに重なるコンタクト用導電膜90をITO膜により形成した後、コンタクトホール45aの内部を埋める埋め込み膜48をシリコン酸化膜により形成し、その後、埋め込み膜48に対して反応性イオンエッチングを行い、コンタクト用導電膜90を露出させる。また、コンタクトホール45aの内部には埋め込み膜48を残す。その際、埋め込み膜48とコンタクト用導電膜90とのエッチング選択比を利用して埋め込み膜48を選択的に除去してコンタクト用導電膜90を露出させる。

(もっと読む)

半導体装置及びその製造方法

【課題】基板貫通電極の周囲に形成される絶縁分離部において、埋め込まれる絶縁膜が接合面を有していると、基板裏面の研削後の絶縁分離部は、接合面が基板主面から基板裏面に達することで、機械的強度が低下しやすく、貫通電極に応力を印加した場合に絶縁分離部の内側領域が孤立しやすい。

【解決手段】絶縁分離部5に埋め込まれる絶縁膜を第1の絶縁膜3と第2の絶縁膜4の少なくとも2段の積層構造とすることで、第1の絶縁膜3の接合面3Sと第2の絶縁膜4の接合面4Sとが第2の絶縁膜4の底面の接合面のない領域で分断され、機械的強度が増加し、絶縁分離部の内側領域の孤立を阻止することができる。

(もっと読む)

半導体装置の製造方法

【課題】 シリコン基板を貫通するビアホールの形成時におけるノッチの発生を抑制することができ、製造歩留まり及び信頼性の向上をはかる。

【解決手段】 シリコン基板貫通電極を有する半導体装置の製造方法であって、表面側に機能素子と配線層15が形成され、且つ配線層15の下層にエッチング停止層12を有するシリコン基板10の表面側に支持基板30を取着した後、基板10の裏面側を研削して厚みを減少させる。次いで、基板10の裏面側に、ビアホール用開口及び該開口よりも小径のダミーホール用開口を有するマスクを形成した後、基板10の裏面側からエッチングすることにより、配線層15の一部に達するビアホール42を形成すると共に、基板10の途中までダミーホール43を形成する。次いで、ビアホール42の側面に絶縁膜44を形成した後、ビアホール42内に配線材料を形成する。

(もっと読む)

41 - 60 / 992

[ Back to top ]