Fターム[5F033QQ31]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エッチバック (992)

Fターム[5F033QQ31]に分類される特許

21 - 40 / 992

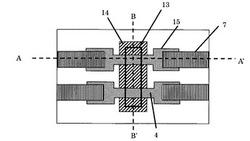

半導体装置

【課題】ヒューズ開口部からの水分侵入による電特異常及び配線腐食を防止する半導体装置を提供する。

【解決手段】ヒューズ配線4の下方には凸領域となるTEOS膜14の下敷きがあり、ヒューズ配線4はTEOS膜14を跨ぐように設けられ、ヒューズ配線4の上方にはTEOS膜14よりも小さい領域のヒューズ開口部13が設けられる。さらに、TEOS膜14の無い領域にてヒューズ配線14の両端に設けられたヒューズ端子15には第1金属配線7が電気的に接続されている。

(もっと読む)

半導体装置及びその製造方法

【課題】柱状半導体層の幅を広く維持することができる半導体装置を提供すること。

【解決手段】半導体装置は、一つの直線上に順に形成された、第1、第2及び第3の柱状半導体層と、第2及び第3の柱状半導体層の間の空間であって第2及び第3の柱状半導体層の側面に夫々設けられた第1及び第2のゲート電極と、第1及び第2の柱状半導体層の間の空間及び第2及び第3の柱状半導体層の空間に埋め込まれた層間絶縁膜とを有する。層間絶縁膜は、第1及び第2の柱状半導体層の間の空間内であってゲート電極を介することなく第1及び第2の柱状半導体層の側面に形成され、第2及び第3の柱状半導体層の間の空間内であって第1及び第2のゲート電極を介して第2及び第3の柱状半導体層の側面に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】貫通電極を効率良く形成する。

【解決手段】シリコン基板1にビアホール25を形成し、絶縁膜22を形成した後、ビアホール25に低誘電率膜31を埋め込む。ビアホール25内の低誘電率膜31の膜厚を異方性ドライエッチングによって所望の値に減少させる。この異方性ドライエッチングによって、絶縁膜22上の低誘電率膜31が除去される。続いて、ビアホール25内に導電材を埋め込み、トランジスタT1,T2上に多層配線を形成する。この後、シリコン基板1の裏面側を研磨して導電材を露出させると、貫通電極が形成される。

(もっと読む)

半導体チップ、これを含む半導体パッケージ、及びその製造方法

【課題】信頼性を向上させることができる高集積化された半導体チップ及びこれを含む半導体パッケージが提供される。

【解決手段】本発明にしたがう半導体チップは、基板と、前記基板を貫通している貫通ビアと、前記貫通ビアと前記基板との間に介在されたウェッティング膜と、前記ウェッティング膜と前記貫通ビアとの間に介在されたシード膜と、を含む。本発明の実施形態による半導体チップは突出された貫通ビアをウェッティング膜が覆っているので、導電パッドを追加に形成する必要がない。したがって、半導体チップの厚さを減らすことができ、構造が単純化されて半導体装置の高集積化により有利である。また、工程を単純化することができるので、生産収率を増大させ得る。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置において、隣接するメモリセル積層構造間、及び、メモリセル積層構造−選択ゲート積層構造間のショートを防ぐことができる不揮発性半導体記憶装置およびその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、シリコン基板上にゲート絶縁膜、浮遊ゲート電極、電極間絶縁膜および制御ゲート電極が順に積層されたメモリセル積層構造が複数隣接して配置され、隣接する前記メモリセル積層構造間に空隙を有する不揮発性半導体記憶装置であって、前記メモリセル積層構造間のシリコン基板上に、前記メモリセル積層構造の側壁に形成されたシリコン酸化膜より厚いシリコン酸化膜が形成されている。

(もっと読む)

半導体装置の製造方法

【課題】実施形態によれば、工程数削減によるコスト低減を図れる半導体装置の製造方法を提供する。

【解決手段】実施形態によれば、半導体装置の製造方法は、第2の被加工膜の上に第2の方向に延びる複数の第2の芯材膜であって、第1のスペースを隔てて第1の方向に並んだ第1の配列部と、第1のスペースよりも大きな第2のスペースを第1の方向に隔てて配置された第2の配列部とを有し、第2のスペースがループ部の上に位置する第2の芯材膜を形成する工程と、第2の芯材膜を除去し第2の被加工膜上に第2のスペーサー膜を残す工程と、第2のスペーサー膜をマスクにしたエッチングにより、第1の配列部の下の第2の被加工膜を、第2の方向に延びる第2のラインパターンを含む第2のラインアンドスペースパターンに加工するとともに、第2のスペースの下の第2の被加工膜と、第1の被加工膜のループ部とを除去する工程とを備える。

(もっと読む)

半導体記憶装置及びその製造方法

【課題】メモリセル部及び周辺回路部を微細化する。

【解決手段】半導体基板20に設けられたメモリセル部11及び周辺回路部12を有する半導体記憶装置の製造方法であって、メモリセル部11及び周辺回路部12にそれぞれ層間絶縁層37及び47を形成する工程と、層間絶縁層37及び47上にそれぞれ、心材50を形成する工程と、心材50をスリミングする工程と、メモリセル部11及び周辺回路部12の心材50の側面にそれぞれ、側壁38及び48を形成する工程と、側壁38及び48をマスクとして、層間絶縁層37及び47を加工する工程と、加工された層間絶縁層37及び47内にそれぞれビット線BL及び配線層44を形成する工程とを含む。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】低抵抗の微細配線構造を有する半導体装置を提供する。

【解決手段】第1配線420は、半導体基板100上に設けられている。第1ビア440は、第1配線420上に設けられている。また、第1ビア440の底面は、第1配線420に接している。第1絶縁層330は、半導体基板100上に設けられ、少なくとも第1配線420の上面および第1ビア440の側面と接している。第1配線420および第1ビア440のうち各々の側面の少なくとも一部は、各々の金属の結晶粒を分断している。

(もっと読む)

不揮発性記憶素子及び不揮発性記憶装置並びにそれらの製造方法

【課題】良好な電気的特性が得られる不揮発性記憶素子及びその製造方法を提供する。

【解決手段】第1の配線103と、第1の配線103上に形成され、第1の配線103に接続される第1のプラグ107及び第2のプラグ108と、第1電極109、第2電極113、及び抵抗変化層112を有し、第1のプラグ107上に形成され、第1電極109が第1のプラグ107と電気的に接続されている抵抗変化素子114と、抵抗変化素子114上に形成され、第2電極113と電気的に接続されている第2の配線119と、第2のプラグ108上に形成され、第2のプラグ108と電気的に接続されている第3の配線121とを備え、第1のプラグ107の上面と第2のプラグ108の上面とが略同一平面内に形成され、かつ第2の配線119の上面と第3の配線121の上面とが略同一平面内に形成されている。

(もっと読む)

半導体記憶装置およびその製造方法

【課題】メモリセルアレイと周辺回路との間のアレイ端パターンにおける耐圧を向上させる。

【解決手段】浮遊ゲートは半導体基板上の第1の絶縁膜上に設けられる。ゲート間絶縁膜は浮遊ゲート上に、制御ゲートはゲート間絶縁膜上に設けられる。メモリセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含む。周辺回路はメモリセルアレイの周辺に設けられる。第1のダミーセルは、第1の絶縁膜、浮遊ゲート、ゲート間絶縁膜および制御ゲートを含み、メモリセルアレイの端に設けられる。第2のダミーセルは、第1の絶縁膜よりも厚い第2の絶縁膜を含み、第1のダミーセルと周辺回路との間に設けられる。第1のダミーセルにおいて、ゲート間絶縁膜および制御ゲートは浮遊ゲートの上面および2つの側面に設けられる。

(もっと読む)

半導体装置の製造方法

【課題】局所配線を有する半導体装置に関し、位置ずれに起因する電気特性や歩留まりの低下を抑制しうる半導体装置の製造方法を提供する。

【解決手段】半導体基板上に、隣接して配された第1の配線及び第2の配線を形成し、第1の配線の側壁に第1の側壁絶縁膜を、第2の配線の側壁に第2の側壁絶縁膜を形成し、第1及び第2の配線、第1及び第2の側壁絶縁膜が形成された半導体基板上に導電膜を形成し、第1及び第2の配線上の導電膜を選択的に除去し、第1の配線と第2の配線との間の領域に、導電膜により形成され、第1及び第2の側壁絶縁膜によって第1及び第2の配線から隔てられた第3の配線を形成する。

(もっと読む)

半導体装置の製造方法

【課題】基板を貫通する電極の形成に適用できる新規な半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体基板上に半導体素子を形成する工程と、半導体基板に孔を形成する工程と、半導体素子の上方と孔の内壁および底を覆うように絶縁膜を形成する工程と、異方性エッチングにより、半導体素子の上方と孔の底の絶縁膜を除去する工程と、孔の底に金属拡散防止膜を形成する工程と、孔に導電膜を埋める工程とを有する。

(もっと読む)

半導体装置、及びその製造方法

【課題】絶縁破壊が発生しにくい半導体装置及びその製造方法を提供する。

【解決手段】集積回路13と電気的に接続する電極14が位置する半導体基板10を用意する。半導体基板の前記第1の面11とは反対側の第2の面12において等方性エッチングを行い、第1内壁面を有する第1凹部を形成する。第1凹部内から前記半導体基板を貫通して電極に至り、第2内壁面22aを有する第2凹部を形成する。第2の面と第1内壁面によって形成された第1の角部、及び第1内壁面と第2内壁面によって形成された第2の角部を除去するエッチバック処理を行い、第2の面と第2内壁面とを連続する第1内壁面を形成する。角部を除去した後、少なくとも第1内壁面、及び第2内壁面を覆うように、電極とオーバーラップする位置に開口部65を有する絶縁層30を形成する。絶縁層を介して第2凹部内に充填され、電極と接続し、かつ第2の面から突出する導電部40を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】配線コーナーでの電子散乱を減らし、配線の抵抗率の増大を抑制する。

【解決手段】実施形態によれば、半導体装置は、半導体基板と、前記半導体基板上に形成され、配線溝を有する層間絶縁膜とを備える。さらに、前記装置は、前記配線溝内に形成された配線を備える。さらに、前記配線溝の底面と側面との間の角部の曲率半径は、前記配線の配線幅の1/10以上である。

(もっと読む)

半導体装置及びその製造方法

【課題】通電領域表面の周辺の強電界の影響がナノワイヤに及び難くして、ホットキャリアの生成やオフリーク電流を低減する。半導体装置を高性能化する。

【解決手段】基板の表面よりも深い位置に配置され互いに対向する2つの側壁を有する導電膜と、導電膜の2つの側壁の側方に形成され互いに同じ導電型の半導体領域である第1及び第2の通電領域と、導電膜を貫通して2つの半導体領域どうしを接続し第1及び第2の通電領域の導電型とは逆導電型の半導体領域であるナノワイヤと、導電膜と前記ナノワイヤとの境界部に形成された絶縁膜と、を有することを特徴とする半導体装置。

(もっと読む)

半導体ウェハ及びその製造方法

【課題】スクライブ線領域におけるダミーパターンが影響して配線形成の際に露光時のアライメント波形検出精度を低下させるおそれがあった。

【解決手段】複数の素子形成領域と、素子形成領域を相互に区画するスクライブ線領域と、素子形成領域において半導体基板上に配置された複数のパターンと、スクライブ線領域において半導体基板上に配置されるとともに、パターンと同様な構成の複数のダミーパターンと、パターン及びダミーパターンを含む半導体基板上に形成されるとともに、上面が平坦化された層間絶縁膜と、スクライブ線領域における層間絶縁膜に形成されるとともに、ダミーパターンと重ならない領域にて半導体基板に通じないように形成された穴状のアクセサリパターンと、を備える。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

不揮発性半導体記憶装置の製造方法および不揮発性半導体記憶装置

【課題】メモリセルトランジスタのゲート電極間の空隙の形状を最適化し、高性能、高信頼性を実現する不揮発性半導体記憶装置の製造方法。

【解決手段】実施の形態の不揮発性半導体記憶装置の製造方法は、半導体基板上に、第1のゲート絶縁膜、第1のフローティングゲート電極、第1のゲート間絶縁膜、第1のコントロールゲート電極、第1のゲートマスク絶縁膜の積層構造を有する複数のメモリセルゲート電極を形成する。メモリセルゲート電極の側壁部に保護膜を形成し、その一部を第1のコントロールゲート電極の側壁部の一部が露出するよう除去する。金属膜を形成し、熱処理により、金属膜と第1のコントロールゲート電極を反応させ第1の金属半導体化合物層を形成する。メモリセルゲート電極間を埋め込み、内部に空隙を有する層間絶縁膜であって、第1のコントロールゲート電極の上面よりも半導体基板から離れた位置に空隙の上端が位置する層間絶縁膜を形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を製造することはできないから、高抵抗の拡散抵抗は実現できなかった。

【解決手段】一組の薄膜構造体の対向する間隔に、サイドウォール形成用の絶縁膜を形成する際に生じる空隙を利用して露光光源として真空紫外光を用いるホトリソ技術のパターン解像限界より微細な拡散抵抗を形成する。薄膜構造体を配線抵抗として利用すれば、これらを接続して設けることにより温度特性に優れる抵抗素子を構成することもできる。

(もっと読む)

半導体装置及びその製造方法

【課題】高品質な配線を有する半導体装置を提供する。

【解決手段】第1の領域100及び第2の領域200に設けられた第1の絶縁層10と、第1の領域に設けられた第1の絶縁層上に形成された第2の絶縁層11aと、第2の領域200に設けられた第1の絶縁層上に形成され、第2の絶縁層と略同一の高さを有する第3の絶縁層11cと、第1の領域に設けられた第1の絶縁層上及び第2の絶縁層の両方の側壁に形成された第1の配線層13aと、第2の領域に設けられた第1の絶縁層上、及び第3の絶縁層の上面及び側壁上に形成された第2の配線層13bと、第1の絶縁層、第2の絶縁層、第1の配線層、及び第2の配線層を覆う第4の絶縁層15と、第1の領域に設けられた第4の絶縁層内に形成され、第1の配線層に接続された第1のコンタクトプラグ17aと、第2の領域に設けられた第4の絶縁層内に形成され、第2の配線層に接続された第2のコンタクトプラグ17bと、を備える。

(もっと読む)

21 - 40 / 992

[ Back to top ]