Fターム[5F033QQ35]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | エッチング (29,543) | エツチングの速度差の利用 (676)

Fターム[5F033QQ35]に分類される特許

661 - 676 / 676

層構造の製造方法

本発明は、層構造の製造方法に関するものである。導電層および犠牲層をパターニングし、形成する。これらの層の上に、電気絶縁層を形成し、犠牲層の表面領域が露出するようにパターニングする。該露出した領域を除去し、そうすることによって露出したパターン形成された導電層の表面領域を、導電性材料からなる構造によって覆う。  (もっと読む)

(もっと読む)

改善された二重ダマシン集積構造およびその製造方法

ガスクラスターイオンビーム処理を用いた多孔質超低k値(ULK)絶縁体材料内に二重ダマシン構造を形成する方法に関して開示する。これらの方法においては二重ダマシンULK処理中におけるハードマスク層を最小にし、最終的なULK二重ダマシン構造内には、ハードマスク層が存在しない。ガスクラスターイオンビームのエッチング処理、緻密化処理、孔のシーリング処理、アッシング処理の各方法が記載されており、該方法は、材料の除去と同時にULKインターフェースの緻密化を進行させる。緻密なインターフェースとハードマスクがない新規なULK二重ダマシン構造が含まれている。 (もっと読む)

相異なるチャネル領域に相異なるよう調整された内在応力を有するエッチストップ層を形成することによって、相異なる機械的応力を生成するための技術

コンタクトエッチストップ層(116)を設けることによって、異なるトランジスタ型(100N),(100P)のチャネル領域内の応力を効果的に制御することができる。その際、コンタクトエッチストップ層(116)の引張応力部分と圧縮応力部分は、ウェット化学エッチング、プラズマエッチング、イオン注入、プラズマ処理などの十分に確立されたプロセスによって得ることができる。このため、プロセスを著しく複雑にすることなく、トランジスタ(100N),(100P)の性能を大きく改善することができる。  (もっと読む)

(もっと読む)

空隙を有する半導体デバイスの形成方法および該方法によって形成された構造

【課題】半導体デバイスの形成方法および該方法によって形成されたデバイスを提供すること。

【解決手段】第1の誘電材料(12a〜f)と第2の誘電材料(14a〜f)の互層を付着させる。ここで、第1の誘電材料と第2の誘電材料は異なる速度で選択的にエッチング可能である。誘電材料の互層内に第1のフィーチャ(22、24)を形成する。誘電材料の互層を選択的にエッチングして、第1の誘電材料を有するそれぞれの層内の第1の誘電材料の少なくとも一部分(26)を除去し、第2の誘電材料は本質的にエッチングされていないままにしておく。

(もっと読む)

半導体構成のための電気的接続を形成する方法

本発明は、半導体構成に関連して電気的接続を形成する方法を含む。その上に導電線路を有し、導電線路に隣接して少なくとも2つの拡散領域を有する半導体基板が設けられる。パターン化されるエッチ・ストップが拡散領域の上に形成される。パターン化されるエッチ・ストップは、開口を貫通して延びる1対の開口を有し、開口は導電線路の軸に実質的に平行に一列に並んでいる。絶縁材料がエッチ・ストップ上に形成される。絶縁材料は、絶縁材料内にトレンチを形成し且つ開口をエッチ・ストップから拡散領域まで延ばすために、エッチングに対して露出される。トレンチの少なくとも一部分は開口の直上にあり、線路の軸に沿って延びる。導電材料が開口内とトレンチ内に形成される。  (もっと読む)

(もっと読む)

サイドウォールスペーサの形成方法

本発明により、基板(201)上のフィーチャ(206)に隣接するサイドウォールスペーサ(217、218)を形成することができる。フィーチャ(206)は1つ以上の保護層(220、207)に覆われる。スペーサ材料層(211)はフィーチャ(206)上に蒸着され、異方性エッチングされる。異方性エッチングに使用されるエッチング液はスペーサ材料を選択的に除去することに適しており、一方で1つ以上の保護層(220、207)はこのエッチング液による影響を実質的に受けない。その結果、1つ以上の層(220、207)はフィーチャがエッチング液にさらされるのを保護する。  (もっと読む)

(もっと読む)

プラズマ加工システムによる基板エッチング法

プラズマ加工システムで基板をエッチングする方法を提供する。基板は、半導体層、その半導体層上方に提供された第1バリアー層、その第1バリアー層上方に提供された低k層、その低k層上方に提供された第3ハードマスク層、その第3ハードマスク層上方に提供された第2ハードマスク層、及びその第2ハードマスク層上方に提供された第1ハードマスク層を有する。方法には、第1ハードマスク層の第1ハードマスク材料、第3ハードマスク層の第3ハードマスク材料、及び第1バリアー層の第1バリアー層材料に対して低選択度を有するが、第2ハードマスク層の第2ハードマスク材料に対しては高選択度を有する第1エチャントと、第1ハードマスク層の第1ハードマスク材料、第3ハードマスク層の第3ハードマスク材料、及び第1バリアー層の第1バリアー層材料に対しては高選択度を有する第2エチャントとで基板を交互にエッチングするステップが含まれ、第1エチャントは第2ハードマスク層の第2ハードマスク材料に対して低選択度を有する。  (もっと読む)

(もっと読む)

炭素含有アンチヒューズ材料を使用した再プログラム可能な金属−金属間のアンチヒューズ

金属−金属間のアンチヒューズが集積回路内の2つの金属相互接続層の間に配置される。下側のバリア層はTiから形成される。下側の付着力促進層は下側のTiバリア層の上に配置される。アモルファス炭素、および、水素およびフッ素の少なくとも1つによりドープされたアモルファス炭素のうち少なくとも1つを有するグループから選択されたアンチヒューズ材料層が、下側の付着力促進層上に配置される。上側の付着力促進層がアンチヒューズ材料層の上に配置される。上側のTiバリア層が上側の付着力促進層の上に配置される。  (もっと読む)

(もっと読む)

成膜方法、SiO2膜、電子部品および電子機器

【課題】所定パターンのSiO2膜を容易かつ安価に形成し得る成膜方法、かかる成膜方法により形成されたSiO2膜、このSiO2膜を備える電子部品および電子機器を提供すること。

【解決手段】本発明の成膜方法は、所定パターンの第2の層間絶縁層(SiO2膜)5を形成する方法であり、主としてポリオルガノシロキサンで構成されるポリオルガノシロキサン膜を形成する第1の工程と、ポリオルガノシロキサン膜の前記所定パターンに対応する領域に、第1のSiO2化処理を施して、前記領域に存在するポリオルガノシロキサンをSiO2に変化させる第2の工程と、SiO2に変化した前記領域をアルカリ溶液により除去する第3の工程と、第3の工程において残存するポリオルガノシロキサン膜に、第2のSiO2化処理を施して、ポリオルガノシロキサンをSiO2に変化させることにより、第2の層間絶縁層5を得る第4の工程とを有する。

(もっと読む)

多孔質絶縁膜及びその製造方法並びに多孔質絶縁膜を用いた半導体装置

半導体装置を構成する絶縁膜として有効な多孔質絶縁膜の作製方法、該絶縁膜の上下界面に接する半導体材料と高い密着性を有する多孔質絶縁膜の作製方法を提供。

少なくとも一つ以上の、分子中に環状シリカ骨格を有し且つ該環状シリカ骨格に少なくとも一つ以上の不飽和炭化水素基が結合されている有機シリカ化合物の分子蒸気、を含む気体をプラズマ中に導入し、半導体基板上に多孔質絶縁膜の成長を行う。

(もっと読む)

トレンチエッチングのためのラインエッジ粗さ低減

【課題】基板上の誘電体レイヤにおいてトレンチ深さまでトレンチをエッチングする方法を提供する。

【解決手段】ARCが前記誘電体レイヤ上に設けられる。厚さを有するフォトレジストマスクが前記ARC上に形成される。前記ARCがエッチングされる。1:1および2:1の間であるフォトレジストに対する誘電体のエッチング選択性で、トレンチが前記誘電体レイヤ中へエッチングされる。

(もっと読む)

薄膜トランジスタ表示板、これを含む平板ディスプレイ表示装置及びその製造方法

本発明は、薄膜トランジスタ表示板とこれを含む液晶表示装置及びその製造方法に関し、薄膜トランジスタ表示板は液晶表示装置や有機EL(electro luminescence)表示装置などで、各画素を独立的に駆動するための回路基板において、画素電極またはゲート線及びデータ線の拡張部を外部回路と接続させるコンタクト補助部材を、IZO及びITOの2重層で形成することに対する発明であって、IZOで形成された下部層とITOで形成された上部層を有するように形成する。前記のように画素電極またはコンタクト補助部材を二重層で形成することによって、エッチング過程で下部配線が損傷されることを防止し、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を良好に確保することができる。また、コンタクト補助部材のみをIZOとITO二重層で形成することによって、グロステストの際に探針とコンタクト補助部材とのコンタクト抵抗の均一性を確保することができ、ITOの使用を減らすことによって製造単価を下げることができる。  (もっと読む)

(もっと読む)

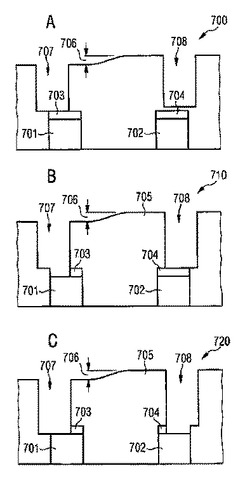

溝配線を有する半導体装置および半導体装置の製造方法

【課題】 多層配線において、ショートやビア抵抗増加のような目合わせずれによる問題を回避し、信頼性の高い多層配線を得る。

【解決手段】 半導体装置は、第1配線層(201)と、層間絶縁層(202〜208)とを具備する。第1配線層(201)は、基板の上面側に設けられ、第1配線を含む。層間絶縁層(202〜208)は、前記第1配線層(201)上に設けられ、一方の端を前記第1配線に接続されたビアと、前記ビアの他方の端に接続された第2配線とを含む。前記層間絶縁層(202〜208)はシリコン酸化膜より低い比誘電率を有する。前記層間絶縁層(202〜208)の上部は、下側から順に、シリコン酸化膜(206)、シリコン窒化膜(207)、シリコン酸化膜(208)を備える。

(もっと読む)

デュアルダマシンによる半導体装置の製造方法

【課題】 放熱性が良好で、製造コストが低く、微細加工に好適なデュアルダマシンによる半導体装置の製造方法を提供する。

【解決手段】 基板1上に無機層間膜5、有機層間膜6、シリコン酸化膜からなる下部マスク7、シリコン窒化膜からなる上部マスク8を形成し、上部マスク8上にシリコン酸化窒化膜からなり膜厚が20乃至100nmであるカバーマスク10を形成する。そして、反射防止膜11及びレジスト膜12を形成する。次に、レジスト膜12をマスクとして、反射防止膜11、カバーマスク10、下部マスク7をエッチングする。そして、カバーマスク10をマスクとして、有機層間膜6及び無機層間膜5をエッチングしてビアホールを形成する。次に、上部マスク8をマスクとして有機層間膜6をエッチングして配線溝を形成する。

(もっと読む)

半導体チップ、配線基板およびそれらの製造方法ならびに半導体装置

【課題】複数の半導体チップを配線基板に積層しても、半導体チップを積層した半導体装置の厚みおよび基板面積の増大および半導体チップ間の配線長の増加を招かない半導体チップ、その製造方法および半導体装置等を提供する。

【解決手段】半導体基板13と、半導体基板13の第1の面14に形成された第1の外部電極21と、半導体基板13の第2の面17に形成された第2の外部電極22と、半導体基板13に形成された貫通孔16とを有し、貫通孔16は第2の面17となす内角が鈍角をなして形成された斜面15に設けられ、第1の外部電極21と第2の外部電極22とは、貫通孔16の内壁および斜面15を経由して形成された導電パターン19により電気的に接続されている。

(もっと読む)

多層スピンオン多孔性誘電体からなるlow−k配線構造

【課題】その中にマイクロトレンチを含まない低誘電体層間絶縁膜金属導体配線構造およびそのような構造の形成方法を提供する。

【解決手段】導体抵抗に対する制御は、第1の原子組成を有する多孔性の低誘電体層間絶縁膜の線とバイア誘電体層との間に位置する第2の原子組成を有する埋込みエッチング停止層により行われる。本発明の配線構造は、また、二重波形模様タイプの配線構造を形成する際に助けになるハードマスクを含む。第1および第2の組成は、エッチング選択性が少なくとも10:1またはそれ以上になるように選択され、特定の原子組成および他の発見できる量を有する多孔性の低誘電体層間絶縁膜有機材料または無機材料の特定のグルーブから選択される。

(もっと読む)

661 - 676 / 676

[ Back to top ]