Fターム[5F033QQ58]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入の対象 (894) | 基板 (558)

Fターム[5F033QQ58]に分類される特許

541 - 558 / 558

半導体記憶装置及びその製造方法

【課題】一列配置されるビット線コンタクトCBの形成予定領域におけるボイドの発生を回避する。

【解決手段】半導体チップ100上に搭載され、ビット線BLと、ビット線に直交するソース線SL及びワード線WLを備える半導体記憶装置において、ビット線方向に配列されたワード線の両端部に隣接して、ワード線に平行に配列されるビット線側選択ゲート線SGD及びソース線側選択ゲート線SGSと、ビット線とワード線の交差部に配置されるメモリセルトランジスタMT及びビット線と選択ゲート線の交差部に配置される選択ゲートトランジスタSTと、ビット線側選択ゲート線間においてワード線方向に配置されるビット線コンタクトCBと、ソース線側選択ゲート線間においてワード線方向に配置されるソース線コンタクトCSとを備え、ビット線側選択ゲート線間の間隔L1が、ソース線側選択ゲート線間の間隔L2よりも大きい半導体記憶装置。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】 ドライエッチングにより半導体基板やポリシリコン層に生じるダメージ層を効果的に除去して、寄生抵抗や接合リークが低減された半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、半導体基板上に絶縁膜を形成する工程と、前記絶縁膜を、ドライ工程によりエッチングする工程と、前記エッチングにより前記半導体基板上に生じたダメージ層を、熱分解した原子状の水素により、所定の温度下で除去する工程とを含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】接続孔の直径を小さくしても、接続孔に埋め込まれたプラグと、プラグ上の配線との接触抵抗を低くする。

【解決手段】第1の導電層4上に、絶縁膜8を形成し、絶縁膜8に、第1の導電層4上に位置する接続孔8cを形成する。接続孔8cの中及び絶縁膜上に導電膜を形成し、さらに、絶縁膜8a上に位置する導電膜をCMP法で除去することにより、接続孔8cに導電体9を埋め込む。接続孔8cに埋め込まれた導電体9の表層を、不活性イオンを用いたスパッタエッチングにより除去し、その後、絶縁膜8上に、導電体9に接続する第2の導電層10aを形成する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】絶縁膜の平坦性を向上させるとともに、生産性を向上させ、製造コストを抑えることが可能な半導体装置の製造方法および半導体装置を提供する。

【解決手段】基板11上に設けられたサイドウォール15を備えたゲート電極12による段差を有する基板11上に下地絶縁膜18を形成する第1工程と、段差下部よりも段差上部を覆う下地絶縁膜18上に成膜される膜の成長が抑制されるように、段差上部を覆う下地絶縁膜18に選択的に表面処理を行う第2工程と、表面処理が施された下地絶縁膜18上に、絶縁膜19を形成する第3工程とを有することを特徴とする半導体装置の製造方法およびこれによって得られる半導体装置である。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト間のショートが効果的に防止され、微細化に対応可能な半導体装置およびその製造方法を得る。

【解決手段】半導体基板上に絶縁膜を介して複数の積層ゲート電極を形成するゲート電極形成工程と、前記積層ゲート電極の伸長方向の側面にサイドウォールを形成するサイドウォール形成工程と、前記半導体基板上に前記積層ゲート電極およびサイドウォールを覆う絶縁層を形成する絶縁層形成工程と、前記複数の積層ゲート電極間の前記絶縁層を選択的にエッチング除去してライン状のコンタクト用溝を形成するコンタクト用溝形成工程と、 前記コンタクト用溝に導電性材料を埋め込むことによりライン状のコンタクトプラグを形成するコンタクトプラグ形成工程と、前記コンタクトプラグをその長手方向で分断して、互いに電気的に分離されたコンタクトを形成するコンタクト形成工程と、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 微細化された半導体装置において、半導体素子相互間及び配線相互間に層間絶縁膜が十分に埋め込む。

【解決手段】半導体基板1に形成された半導体素子と、半導体素子上及び半導体基板1上に位置し、下地膜としての第1の絶縁膜9aと、第1の絶縁膜9a上に位置し、O3とTEOSを反応させるCVD法により形成された第2の絶縁膜9bと、第2の絶縁膜9b上に位置し、プラズマCVD法により形成され、表面がCMP法により平坦化された第3の絶縁膜9cと、第1乃至第3の絶縁膜に形成され、半導体素子上に位置する接続孔10a,10bと、接続孔10a,10bに埋め込まれた導電体11a,11bと、第3の絶縁膜9c上に形成され、導電体11a,11bを介して半導体素子に接続する配線12a,12bとを具備する。

(もっと読む)

半導体素子のストレージノードコンタクトの形成方法

【課題】ランディングプラグコンタクトとストレージノードコンタクトとの間の不整合を防止し、接触抵抗を改善することができる半導体素子のストレージノードコンタクトの形成方法を提供すること。

【解決手段】複数のゲート23とソース/ドレーン領域25が形成された半導体基板21のゲート間に酸化膜26とランディングプラグコンタクトを形成するステップと、ランディングプラグコンタクト及びゲートを含んだ半導体基板の全面上に層間絶縁膜29を形成するステップと、層間絶縁膜をエッチングしてランディングプラグコンタクトを露出させる第1ストレージノードコンタクトホールを形成するステップと、露出されたランディングプラグコンタクトと酸化膜を除去し、第2ストレージノードコンタクトホールを形成するステップと、第2ストレージノードコンタクトホール内にポリシリコンを埋め込んでストレージノードコンタクト30を形成するステップとを含む。

(もっと読む)

パターン形成方法を含む半導体装置の製造方法

【課題】 本発明は半導体装置の製造工程において、レジストなどのマスクパターンを用いる際に発生する反応生成物等のレジスト等への不均一な付着によるパターン形状等の不良を生じさせず、また、寸法精度が良好な微細パターンの形成方法を提供することを目的とする。

【解決手段】 パターン形成方法を含む半導体装置の製造方法として、第1の薄膜の側壁に第2の薄膜を形成し、その側壁に形成された第2の薄膜の先端部が不均一にならないように、平坦化法により、精度良くエッチバックして揃える。

(もっと読む)

半導体装置及びその製造方法

【課題】 高抵抗素子を、半導体基板内の不純物拡散層を用いて形成することにより、サリサイドプロセスにおいても、構造的に、高抵抗素子部におけるシリサイド膜の形成を防止し、工程数を増大させることなく、高抵抗素子の形成を可能とする。

【解決手段】 シリコン基板11aの上の素子領域にゲート絶縁膜12aを介してポリシリコン配線12層を形成し、このポリシリコン配線12層の上から、不純物を拡散してポリシリコン配線12層の抵抗値を調整すると共に、このポリシリコン配線12層をマスクとしてシリコン基板11a上の素子領域内において、ポリシリコン配線12層に隣接する領域に不純物を拡散させN型不純物層11cを形成してこれを高抵抗素子とし、この高抵抗素子つまりN型不純物層11cの上にSiN膜14からなる絶縁膜を配置して、この上から、サリサイドを施して、ポリシリコン配線12の上にシリサイド膜17を形成することにより得られる。

(もっと読む)

半導体装置

【課題】

酸化シリコン層、窒化シリコン層の積層ライナを備えたSTIを有し、帯電を低減できる半導体装置およびその製造方法を提供する。

【解決手段】

半導体装置は、シリコン基板と、前記シリコン基板の表面から下方に向かって形成され、前記シリコン基板の表面に活性領域を画定するトレンチと、前記トレンチの内壁を覆う酸化シリコン層の第1ライナ層と、前記第1ライナ層の上に形成された窒化シリコン層の第2ライナ層と、前記第2ライナ層の上に形成され、前記トレンチを埋める絶縁物の素子分離領域と、前記活性領域に形成されたpチャネルMOSトランジスタと、前記pチャネルMOSトランジスタを覆って,前記シリコン基板上方に形成され,紫外光遮蔽能を有さない窒化シリコン層のコンタクトエッチストッパ層と、前記コンタクトエッチストッパ層の上方に形成され、紫外光遮蔽能を有する窒化シリコン層の遮光膜と、を有する。

(もっと読む)

半導体装置におけるセルフアラインドコンタクトを形成する製造方法

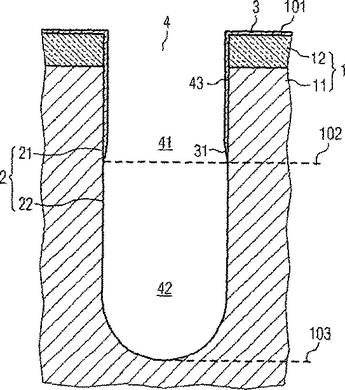

【課題】半導体装置におけるセルフアラインドコンタクトを形成する製造方法であって、基板のコアエリアとターミネーションエリアの一部分まで拡張してトレンチをエッチングで形成する方法を提供する。

【解決手段】第一の酸化物はトレンチの壁部に隣接した前記基板上に生成される。ポリシリコン層は前記コアエリアと前記ターミネーションエリアに蒸着される。このポリシリコン層は、前記コアエリアの前記トレンチの一部分にゲート領域を形成するように選択的にエッチングされる。このポリシリコン層のエッチングは、また、前記ゲートインターコネクト領域の第一部分を前記ターミネーションエリアの前記トレンチ部分に形成し、ゲートインターコネクト領域の第二部分を前記ターミネーションエリアにおける前記トレンチの外側に形成する。

(もっと読む)

貫通電極の形成方法、貫通電極および半導体装置

【課題】 工数や手間の増大を招くことなく、半導体基板の汚染を防止できる貫通電極の形成方法を提供すること。

【解決手段】 シリコン基板1に非貫通孔を形成し、この非貫通孔の底面からシリコン基板1に不純物を添加して、不純物添加部2を形成する。非貫通孔の側面および底面に表面側絶縁膜3を形成し、表面側絶縁膜3の内側に埋め込み電極4を形成する。シリコン基板1の裏面部分を除去して、不純物添加部2を裏面に露出させる。シリコンに対してエッチングレートが高いエッチングによって、不純物添加部2を、埋め込み電極4に対してセルフアライメントした状態で除去できる。

(もっと読む)

半導体素子の製造方法

【課題】 シリコンを含むN型の導電領域と直接接続される導電パターンの形成時に、N型の導電領域と接続される部分のコンタクト抵抗の増大を防止し、バリア膜の厚さ増大に伴う導電パターンの寄生容量の増大を防止できる半導体素子の製造方法を提供すること。

【解決手段】 シリコンを含むN型の導電領域(207)にN型の不純物をドープして、N型の高濃度不純物拡散領域(212)を形成する工程と、CVD法を用いて高濃度不純物拡散領域(212)上にバリア用第1金属膜を蒸着し、高濃度不純物拡散領域(212)のシリコンと前記第1金属膜の金属とを反応させて、高濃度不純物拡散領域(212)と前記第1金属膜との間の界面に金属シリサイドを形成する工程、前記第1金属膜上に導電膜を形成する工程、及び、前記導電膜と前記第1金属膜とを選択的にエッチングして、導電パターンを形成する工程を含む。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】 誘電体膜の段差被覆性がよく、かつ誘電体物質の廃棄量を少なくする。

【解決手段】 下地膜8上に、パターニングされた下部電極11を形成する工程と、インクジェット方式の塗布機構を用いて、下部電極11上に誘電体物質を塗布する工程と、塗布された誘電体物質を加熱することにより、下部電極11上に誘電体膜12を形成する工程と、誘電体膜12上に上部電極を形成する工程とを具備する。上部電極を形成する工程は、下地膜8上及び誘電体膜12上に層間絶縁膜を形成する工程と、層間絶縁膜に、誘電体膜上に位置する開口部を形成する工程と、開口部の中及び層間絶縁膜上に導電体を堆積する工程と、層間絶縁膜上から導電体を除去することにより上部電極を形成する工程とを具備する。

(もっと読む)

基板への相互接続を有する集積回路およびその製造方法

ソース/ドレイン(20)とゲート(26)との間の接点(32)が、ゲート誘電体(46)の選択部分(35)へ埋設物を注入することによりゲート誘電体(46)の選択部分(35)を導電性にすることで行われる。ゲート材料は集積回路全体(10)の上の層に位置する。ゲート(26)がソース/ドレイン(20)に接続する領域(32)が識別され、この識別位置(35)においてゲート誘電体(46)が導電性となるよう埋設物が注入される。ソース/ドレイン(20)が導電性ゲート誘電体(35)のそのような導電性領域の下を延び、該位置で埋設物が注入されたゲート誘電体(35)がゲート(26)をソース/ドレイン(20)に短絡するように、ソース/ドレイン(20)は形成される。これによって集積回路(10)上のスペースが節約され、相互接続層の必要性が低減され、露出したシリコン基板上にポリシリコンを堆積およびエッチングさせることに付随する問題を回避することができる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 セルトランジスタの拡散層に接続された多結晶シリコン電極と、周辺回路トランジスタの拡散層に接続された金属電極とを備え、多結晶シリコン電極が形成された拡散層の接合リーク電流が抑制され、これによって、良好な情報保持特性を有する半導体装置の製造方法を提供する。

【解決手段】 半導体装置の製造方法は、多結晶シリコン電極に接続された拡散層を有するトランジスタを形成する工程と、980〜1020℃の基板温度で熱処理する第1の高温熱処理工程(工程A2)と、700〜850℃の基板温度で熱処理する第1の低温熱処理工程(工程A3)とをこの順に有する。

(もっと読む)

インコンフォーマルな堆積を用いて半導体プロセス技術において基板を垂直にパターニングする方法

典型的には半導体ウェーハである基板(1)の、レリーフ状にパターニングされた基板表面(101)上に、堆積方法(ADL;atomic layer deposition:原子層堆積)を用いて、基板表面(101)に対して傾斜し、および/または垂直である処理表面(2)に、被覆層(3)が提供される。被覆層(3)は、前駆材料の少なくとも1つの処理量の制限によって、および/または堆積方法の時間的制限によって、簡易な方法において、基板表面(101)に対して垂直な方向にパターニングされ、後続のプロセス工程のための機能層あるいはマスクとして形成される。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】 微細トランジスタと高耐圧トランジスタの線幅バラツキを低減する。

【解決手段】 P型の半導体基板1上の段差部を境にしてP型ウエル2及びN型ウエル3が形成されたものにおいて、段差低部に形成される前記P型ウエル2上に第1線幅を有する第1のトランジスタ(微細トランジスタ)が形成され、段差高部に形成される前記N型ウエル3上に第1のトランジスタよりも線幅の太い第2線幅を有する第2のトランジスタ(高耐圧トランジスタ)が形成されていることを特徴とする。

(もっと読む)

541 - 558 / 558

[ Back to top ]