Fターム[5F033QQ59]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入の対象 (894) | 導電膜 (246)

Fターム[5F033QQ59]に分類される特許

241 - 246 / 246

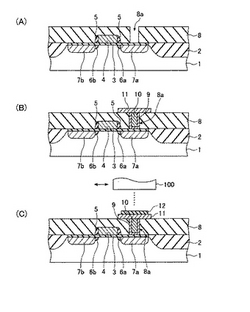

半導体装置の製造方法及び半導体装置

【課題】 誘電体膜の段差被覆性がよく、かつ誘電体物質の廃棄量を少なくする。

【解決手段】 下地膜8上に、パターニングされた下部電極11を形成する工程と、インクジェット方式の塗布機構を用いて、下部電極11上に誘電体物質を塗布する工程と、塗布された誘電体物質を加熱することにより、下部電極11上に誘電体膜12を形成する工程と、誘電体膜12上に上部電極を形成する工程とを具備する。上部電極を形成する工程は、下地膜8上及び誘電体膜12上に層間絶縁膜を形成する工程と、層間絶縁膜に、誘電体膜上に位置する開口部を形成する工程と、開口部の中及び層間絶縁膜上に導電体を堆積する工程と、層間絶縁膜上から導電体を除去することにより上部電極を形成する工程とを具備する。

(もっと読む)

半導体装置におけるセルフアラインドコンタクトを形成する製造方法

【課題】半導体装置におけるセルフアラインドコンタクトを形成する製造方法であって、基板のコアエリアとターミネーションエリアの一部分まで拡張してトレンチをエッチングで形成する方法を提供する。

【解決手段】第一の酸化物はトレンチの壁部に隣接した前記基板上に生成される。ポリシリコン層は前記コアエリアと前記ターミネーションエリアに蒸着される。このポリシリコン層は、前記コアエリアの前記トレンチの一部分にゲート領域を形成するように選択的にエッチングされる。このポリシリコン層のエッチングは、また、前記ゲートインターコネクト領域の第一部分を前記ターミネーションエリアの前記トレンチ部分に形成し、ゲートインターコネクト領域の第二部分を前記ターミネーションエリアにおける前記トレンチの外側に形成する。

(もっと読む)

基板への相互接続を有する集積回路およびその製造方法

ソース/ドレイン(20)とゲート(26)との間の接点(32)が、ゲート誘電体(46)の選択部分(35)へ埋設物を注入することによりゲート誘電体(46)の選択部分(35)を導電性にすることで行われる。ゲート材料は集積回路全体(10)の上の層に位置する。ゲート(26)がソース/ドレイン(20)に接続する領域(32)が識別され、この識別位置(35)においてゲート誘電体(46)が導電性となるよう埋設物が注入される。ソース/ドレイン(20)が導電性ゲート誘電体(35)のそのような導電性領域の下を延び、該位置で埋設物が注入されたゲート誘電体(35)がゲート(26)をソース/ドレイン(20)に短絡するように、ソース/ドレイン(20)は形成される。これによって集積回路(10)上のスペースが節約され、相互接続層の必要性が低減され、露出したシリコン基板上にポリシリコンを堆積およびエッチングさせることに付随する問題を回避することができる。  (もっと読む)

(もっと読む)

金属の化学的機械的研磨用の新規なスラリー

一般に集積回路の製造に有用な、金属を取り除くための、及び、特に貴金属の化学的機械的研磨用の、スラリーは、過ヨウ素酸、研磨剤、及び緩衝系を組み合わせることによって、形成されてもよく、ここでそのスラリーのpHは、約(4)と約(8)との間にある。

(もっと読む)

(もっと読む)

精密ポリシリコン・レジスタ・プロセス

【課題】 製造されるポリシリコン・レジスタのシート抵抗の許容誤差をより正確に制御する精密ポリシリコン・レジスタを製造するためのプロセスを提供する。

【解決手段】 プロセスは、一般に、部分的に形成されたポリシリコン・レジスタを有するウェハに対して、エミッタ/FET活性化高速熱アニール(RTA)を行うステップと、それに続いて、保護誘電体層をポリシリコン上に堆積させるステップと、ドーパントを該保護誘電体層を通して該ポリシリコンに注入して、ポリシリコン・レジスタの抵抗を定めるステップと、シリサイドを形成するステップとを含む。

(もっと読む)

銅配線構造およびその製造方法

【課題】銅配線の寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させる。

【解決手段】Cu16とバリアメタル12、あるいはCu16とキャップ層19との界面近傍に、不純物15を固溶させる、不純物15を析出させる、非晶質Cu14を存在させるまたはCuとの化合物を形成することにより、界面近傍の空孔を減らし、Cuのエレクトロマイグレーション(EM)に対する界面拡散の寄与を減少させ、寿命を増大させ、同時に、密着性を高め、ストレスマイグレーション耐性を向上させた。

(もっと読む)

241 - 246 / 246

[ Back to top ]