Fターム[5F033QQ59]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入の対象 (894) | 導電膜 (246)

Fターム[5F033QQ59]に分類される特許

81 - 100 / 246

半導体装置及びその製造方法

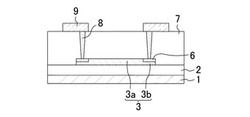

【課題】アナログ回路を構成する抵抗体において、抵抗体の抵抗長が縮小化されることがあっても、アナログ回路を構成する各抵抗体の抵抗値間にバラツキが生じることを抑制する。

【解決手段】アナログ回路を構成する抵抗体3を有する半導体装置であって、半導体基板1上に形成され、長手方向に延びるボディ部3aと該ボディ部3aの端部に連接するヘッド部3bとを有し、且つシリコンからなる抵抗体3と、抵抗体3のヘッド部3bの上部に形成された金属シリサイド膜6と、抵抗体3を覆う層間絶縁膜7中に形成され、金属シリサイド膜6を介して、抵抗体3と電気的に接続するコンタクトプラグ8とを備え、ボディ部3aとヘッド部3bとの境界長は、抵抗体3の抵抗幅よりも大きい。

(もっと読む)

カーボンナノチューブを利用した半導体素子の配線形成方法およびその方法により製造された半導体素子

【課題】高い電流密度を持つカーボンナノチューブを利用した半導体素子の配線形成方法、およびその方法により製造される超高集積度の半導体素子を提供する。

【解決手段】半導体素子の電極120表面を前処理して活性化させる段階と、電極の活性化した表面122上に絶縁層130を形成した後、電極の活性化した表面の一部を露出させるために絶縁層を貫通するコンタクトホール132を形成する段階と、コンタクトホールを通じて電極の活性化した表面に炭素が含まれているガスを供給して前記電極の活性化した表面からカーボンナノチューブ140を成長させて配線を形成する段階と、を具備する半導体素子の配線形成方法およびその方法により製造された半導体素子。

(もっと読む)

半導体装置の製造方法

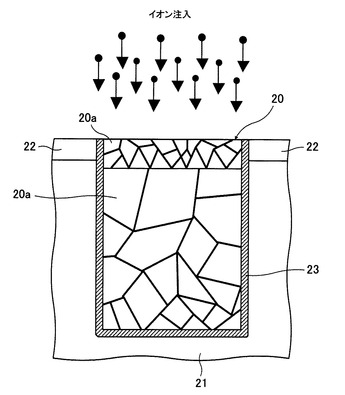

【課題】配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】めっき法を用いてCu配線20を形成する際、まず第1の電流密度の条件で第1の平均粒径を有する第1の金属膜を形成し、次いで、第1の電流密度よりも高い第2の電流密度の条件で第1の平均粒径よりも大きい第2の平均粒径を有する第2の金属膜を形成する。その後、第1,第2の金属膜の上部に所定元素を導入し、導入後、第1,第2の金属膜上にキャップ膜を形成する。

【選択図】図5  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート電極間にエアギャップを制御良く形成する。

【解決手段】本発明の半導体装置の製造方法では、半導体基板2上のゲート絶縁膜3上に浮遊ゲート電極用の多結晶シリコン層4を形成するときに、多結晶シリコン層4の上下方向の中間部のドーパント濃度を、その上下部のドーパント濃度よりも高くするように形成し、この多結晶シリコン層4上に形成したゲート間絶縁膜5上に制御ゲート電極用の多結晶シリコン層9を形成するときに、多結晶シリコン層9の上下方向の中間部のドーパント濃度を、その上下部のドーパント濃度よりも高くするように形成し、複数のゲート電極の側面が露出した状態で熱酸化処理を行なった後、エッチングすることにより、多結晶シリコン層4、9の各側面に凹部11、12を形成し、複数のゲート電極間に絶縁膜7を埋め込み、埋め込まれた絶縁膜7の中にエアギャップ8を形成する。

(もっと読む)

半導体装置の製造方法

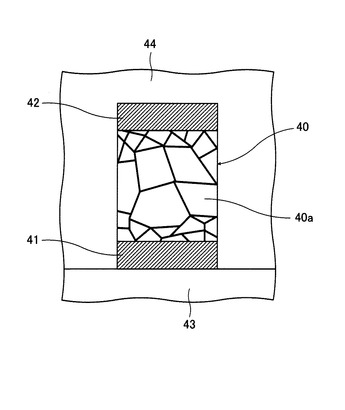

【課題】配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】Al配線40を形成する際、バリアメタル41上に、Al粒子40aが第1の平均粒径となるように第1の条件で第1のAl膜を形成し、次いで、第1の平均粒径より小さい第2の平均粒径となるように第2の条件で第2のAl膜を形成する。その後、第2のAl膜上にバリアメタル42を形成し、形成後、バリアメタル41,42および第1,第2のAl膜を配線パターンに加工する。

【選択図】図9  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】Cu配線上に形成されるCuとSiとを含有する化合物膜の余剰SiがCu配線中へと拡散することを防止した半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、SiとOとが他より多く含まれる領域を有するCu配線となるCu膜260,262と、Cu膜260,262上に選択的に形成された、CuとSiとを含有する選択キャップ膜280と、Cu膜260,262の側面側に形成された層間絶縁膜220と、を備えたことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】 厚いCESL膜を用いてもCESL膜やその上の層間絶縁膜に生じるボイドを回避し、高い駆動電流と高い信頼性を実現する。

【解決手段】 半導体基板10上にゲート絶縁膜12を介してゲート電極13を形成し、ゲート電極13を挟んで基板の表面部にソース/ドレイン領域18を形成してなるMOSFETを有する半導体装置であって、ゲート部のゲート長方向の側部に形成された側壁絶縁膜17と、ソース/ドレイン領域18上に形成された合金層19と、側壁絶縁膜17の側部に設けられ、ゲート長方向の断面で見た基板表面と成すテーパ角度が側壁絶縁膜17よりも小さいテーパ調整用絶縁膜21と、ゲート部、側壁絶縁膜17及びテーパ調整用絶縁膜21を覆うように形成された、チャネルに歪みを与えるための応力付与用絶縁膜22と、応力付与用絶縁膜22上に形成された層間絶縁膜25とを備えた。

(もっと読む)

半導体装置の製造方法

【課題】MISトランジスタを備える半導体装置の性能を向上させる。

【解決手段】シリコン基板1の主面s1上のうち、nMIS領域RnにnMIS用ゲート電極GEnを形成し、pMIS領域RpにpMIS用ゲート電極GEpを形成し、それらの側方下部に、それぞれ、n型ソース・ドレイン領域sdnおよびp型ソース・ドレイン領域sdpを形成する。続いて、シリコン基板1の主面s1と両ゲート電極GEn,GEpとを覆うようにして、引張応力を持つ第1応力膜N1aを形成する。その後、pMIS領域Rpの第1応力膜N1aにイオン注入300を施すことで応力を緩和させる。その後、熱処理を施すことで両ゲート電極GEn,GEpを結晶化してから、第1応力膜N1aを除去する。両ゲート電極GEn,GEpを結晶化する工程では、第1応力膜N1aの引張応力をnMIS用ゲート電極GEnに記憶させる。

(もっと読む)

半導体装置及びその製造方法

【課題】Cuを含む配線について、配線抵抗を低く維持しつつ、しかも、ストレスマイグレーション耐性の劣化を伴うことなく、エレクトロマイグレーション耐性を向上し得る半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10の上方に形成された層間絶縁膜36と、層間絶縁膜36内に形成されたCuより成る配線50と、層間絶縁膜36と配線50の間に形成され、Ti膜42とTa膜44との積層膜より成るバリアメタル膜46とを有し、配線50表面に、TiとSiとを含む界面層54が形成されている。

(もっと読む)

半導体装置、およびその製造方法

【課題】配線間をCuプラグによって電気的に接続する構成において、Cuプラグとの電気的接続の信頼性が高く、リーク電流が少ない半導体装置、およびその製造方法を提供することを目的とする。

【解決手段】本発明における半導体装置100は、拡散層43およびゲート電極42を形成した半導体基板1と、半導体基板1上に形成された層間絶縁膜5と、層間絶縁膜5を貫通し、拡散層43およびゲート電極42上に形成されたコンタクトホール61と、コンタクトホール61の内面に形成されたTiバリアメタル層62と、バリアメタル層62上に形成されたW、Co、Ru、Ptのいずれかを含むシード層63と、シード層63上であってコンタクトホール61を充填するように形成されたCuプラグ64と、Cuプラグ64上に形成された配線層7と、を備える。

(もっと読む)

半導体装置

【課題】電荷を蓄積させる量を容易に調整可能であり、信号遅延回路において信号遅延量を所望に調整可能にする。

【解決手段】セレクタ回路300が、第1半導体部100の電位および第2半導体部200の電位を調整し、第1半導体部100と信号配線10との間と、第2半導体部200と信号配線10との間との少なくとも一方において電位差を生じさせる。これにより、第1半導体部100と信号配線10との間と、第2半導体部200と信号配線10との間との少なくとも一方を、静電容量素子として機能させる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】接触抵抗の増加が抑制されたピラー形状の縦型MOSトランジスタを用いた半導体装置を提供する

【解決手段】基部1aと複数のピラー部1Aとを有するシリコン基板1と、基部1aに設けられた一方のソースドレイン領域6と、ピラー部1Aの側面1bを覆うゲート絶縁膜4と、ゲート絶縁膜4を介してピラー部1Aの側面1bを覆うゲート電極5と、ピラー部1Aの上部に設けられた他方のソースドレイン領域12と、他方のソースドレイン領域12と接続されるコンタクトプラグ9とを備え、ピラー部1Aの上面1cの全面にコンタクトプラグ9が接続されていることを特徴とする半導体装置10。

(もっと読む)

半導体デバイス内でのビアパターニングにおける金属キャップ層の侵食を低減する方法

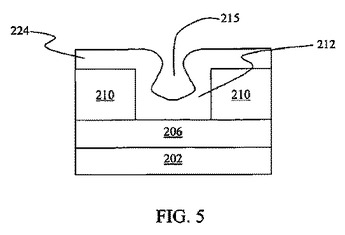

【解決手段】

半導体デバイスの高性能な金属化システムにおいてビア開口をパターニングする間、開口(221A)が導電性キャップ層(213)を通って延び、適切なイオン衝撃が確立されて下層の金属領域(212)の材質が導電性キャップ層(213)の露出した側壁部分へ再分配され、それにより保護材質(212P)が確立される。その結果、後続のウエット化学的エッチング処理(215)において、導電性キャップ層(213)の過度な材質除去の可能性を大幅に低減することができる。

(もっと読む)

薄膜半導体装置およびその製造方法

【課題】 微細化に伴うコンタクト抵抗の増加を防止した、信頼性の高い素子特性を有する薄膜半導体装置を提供すること。

【解決手段】 透明絶縁性基板上に形成され、所定の間隔を隔てて第1導電型の不純物を含むソース領域及び第1導電型の不純物を含むドレイン領域を有する島状半導体層、前記ソース領域及びドレイン領域の間の島状半導体層上に形成されたゲート絶縁膜、前記ゲート絶縁膜上に形成されたゲート電極、前記島状半導体層及びゲート電極を覆う層間絶縁膜、及び前記ソース領域及びドレイン領域にそれぞれ接続する、前記層間絶縁膜に形成された第1及び第2のコンタクト孔内にそれぞれ埋め込まれた第1導電型の不純物を含む凸型ソース多結晶半導体層並びに第1導電型の不純物を含む凸型ドレイン多結晶半導体層を具備することを特徴とする。

(もっと読む)

相変化メモリデバイスに電極を形成する気相法

サブリソグラフィック寸法又は高アスペクト比を含む小寸法を有する開口内に均一で均質に電極材料を形成する方法を提供する。この方法は、内側に形成された開口を有する絶縁層を提供し、開口上及び開口内に均質な導電又は準抵抗材料を形成するステップを含んでいる。この方法は、金属窒化物、金属アルミニウム窒化物及び金属ケイ素窒化物電極組成を形成するCLD又はALDプロセスである。この方法は、アルキル、アリル、アルケン、アルキン、アシル、アミド、アミン、イミン、イミド、アジド、ヒドラジン、シリル、アルキルシリル、シリルアミン、キレーティング、ヒドリド、サイクリック、カルボサイクリック、シクロペンタジエニル、ホスフィン、カルボニル又はハライドから選択された1以上のリガンドを含む金属前駆体を利用する。公的な前駆体は、一般式MRnを有し、Mは金属、Rは上述のリガンド、nは主要な金属原子に結合したリガンドの数に対応している。Mは、Ti、Ta、W、Nb、Mo、Pr、Cr、Co、Ni又は他の遷移金属である。  (もっと読む)

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】バックゲート電極を有するMOSトランジスタのS/D層について、その抵抗を小さくすることができ、且つ、その寄生容量を低減できるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】Si基板1上に形成されたSi層68と、Si層68上に絶縁膜2を介して形成されたSi層3と、Si層3を平面視で囲むようにSi基板1上に形成された絶縁膜4とを有し、絶縁膜4が絶縁膜2よりも厚く形成されたSOI基板10に、MOSトランジスタ50を形成する方法であって、Si層3上にゲート絶縁膜5を介してゲート電極6を形成する工程と、ゲート電極6の両側にS/D層20を形成する工程と、を含み、S/D層20を形成する工程は、ゲート電極6が形成される領域の両側に位置する端部領域のSi層3に不純物層7を形成する工程と、不純物層7と接触する導電膜8を、不純物層7上から絶縁膜4上にかけて形成する工程と、を有する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】記憶情報を高速に読み出す半導体集積回路装置の製造方法を提供する。

【解決手段】本発明の半導体集積回路装置の製造方法は、半導体基板上に第1ゲート電極を形成する工程、この工程の後に第1ゲート電極を覆うように半導体基板上に導電性膜を形成する工程、この工程の後に導電性膜の一部を覆うように半導体基板上にマスクパターンを形成する工程、この工程の後にドライエッチングを行いマスクパターンで覆われていない導電性膜をサイドスペーサ状の第2ゲート電極に加工する工程で、且つマスクパターンで覆われた導電性膜を第2ゲート電極のコンタクト領域としてパターニングする工程、この工程の後にマスクパターンを除去する工程、この工程の後に不揮発性メモリセルを覆うように半導体基板上に層間絶縁膜を形成する工程、この工程の後に層間絶縁膜中に第2ゲート電極のコンタクト領域に接続するプラグを形成する工程、を有する。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、広範囲な材料組成のメタル層をエッチングして配線層等を形成する際の、エッチング時間の短縮化を図り、それによって加工精度の向上及びダメージの抑制を図ることが可能な新規な技術を提供する。

【解決方法】半導体装置の製造方法であって、半導体基材上に絶縁層を形成し、前記絶縁層上にメタル層を形成し、前記メタル層のエッチング除去すべき領域に対してイオン注入を施して少なくとも一部にイオン注入領域を形成した後、前記メタル層の、前記エッチング除去すべき領域に対してエッチング処理を施して除去する。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】安定した動作の積層型不揮発性半導体記憶装置、及びその製造方法を提供する。

【解決手段】電気的に書き換え可能なメモリセルが複数形成されるメモリセル領域と、メモリセルを制御する周辺回路を構成するトランジスタが形成される周辺回路領域とを備え、メモリセル領域には、半導体基板11上に対し垂直方向に、ソース側選択トランジスタ層20、メモリトランジスタ層30、及びドレイン側選択トランジスタ層40が積層されて形成される。メモリホール34内には、ブロック絶縁層(第1絶縁層)35、電荷蓄積層(特性変化層)36、トンネル絶縁層37、及びメモリ柱状半導体層38が形成される。周辺回路領域には、p−型領域101Aにプレーナ型トランジスタのソース/ドレイン領域101Bが形成され、メモリセル領域の複数の導電層の各々と同一平面上に形成され、且つ導電層と電気的に分断される複数のダミー配線層100が形成される。

(もっと読む)

半導体装置とその製造方法

【課題】半導体装置とその製造方法において、製造コストの上昇を抑えつつ、歩留まりを向上させること。

【解決手段】シリコン(半導体)基板1と、シリコン基板1に形成される素子分離絶縁膜6と、シリコン基板1の上、及び素子分離絶縁膜6の上に形成され、素子分離絶縁膜6の上に側面13eを有する導電パターン13aと、素子分離絶縁膜6の上、導電パターン13aの上、及び導電パターン13aの側面13eに形成される絶縁膜16とを有し、導電パターン13aの側面13eにノッチ13wが形成された半導体装置による。

(もっと読む)

81 - 100 / 246

[ Back to top ]