Fターム[5F033QQ59]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入の対象 (894) | 導電膜 (246)

Fターム[5F033QQ59]に分類される特許

101 - 120 / 246

半導体装置および半導体装置の製造方法

【課題】WPP技術における再配線を有する半導体装置の信頼性を向上させる。

【解決手段】再配線が半導体基板1Sの面内において互いに電気的に分離された本体パターン2およびダミーパターン3を有している。多層配線と電気的に接続された本体パターン2と、フローティングされたダミーパターン3とが、半導体基板1Sの面内で混在して設けられている。半導体基板1Sの面内における本体パターン2およびダミーパターン3を合わせた占有率、すなわち再配線の占有率が35%以上60%以下である。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体素子とコンタクトプラグとが高精度で位置合わせされた半導体装置の製造方法を提供する。

【解決手段】半導体基板のエッチング速度が絶縁層2のエッチング速度よりも速くなるように、裏面側から、半導体基板内の突起状領域に対応する位置の異方性エッチングを行い、第1構造体が露出するまで開口2を設ける。

(もっと読む)

半導体装置の製造方法

【課題】Viaホールと下層配線間の抵抗を下げるため、パンチスルー技術にてViaホール底のバリアメタル膜の除去時に、上層配線底のバリアメタル膜も同時に除去されて絶縁膜が深く掘り下げられることを防ぐ。

【解決手段】低誘電率絶縁膜203の表面を水素(H2)と水蒸気(H2O)の混合ガスにてプラズマ処理して、ヤング率を4.5GPaから70GPa程度の改質膜207を形成することにより、その後、上層に形成されたバリアメタル膜208をパンチスルー技術によって除去する際に、下層の低誘電率絶縁膜203へのダメージを低減する。

(もっと読む)

半導体装置およびその製造方法

【課題】複数の導電層を電気的に接続するコンタクト部の近傍におけるリーク電流を効果的に抑制可能な半導体装置を提供する。

【解決手段】半導体基板1の主表面に形成され、低濃度不純物領域5bと高濃度不純物領域5aとを有する不純物領域と、低濃度不純物領域5bと隣り合う位置の上記主表面上に形成されたゲート電極4と、ゲート電極4の一方の側壁上に形成されたサイドウォール絶縁膜12a,12bと、低濃度不純物領域5b上からゲート電極4の他方の側壁上に延在し高さの低いサイドウォール絶縁膜12a,12bと、この高さの低いサイドウォール絶縁膜12a,12bと低濃度不純物領域5bとを覆いゲート電極4の他方の側壁に達するシリコン窒化膜9aと、シリコン窒化膜9aを覆うように形成され上記不純物領域とゲート電極4との双方と電気的に接続されたプラグ11とを備える。

(もっと読む)

配線構造および半導体装置

【課題】電気を流すことができる。

【解決手段】基板11と、基板11上に形成された、開口孔を有する絶縁膜12と、開口孔の底部に形成された、内部にアルカリ金属原子(またはハロゲン原子)16aを有する筒状炭素構造体14と、を有する配線構造10により、基板11と、基板11上に形成された、開口孔を有する絶縁膜12と、開口孔の底部に形成された、内部にアルカリ金属原子(またはハロゲン原子)16aを有する筒状炭素構造体14とにより、筒状炭素構造体14が金属性を示す。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】電極の接触抵抗の低減によって高性能化した半導体装置の製造方法および半導体装置を提供する。

【解決手段】半導体基板上にゲート絶縁膜を形成する工程と、ゲート絶縁膜上にゲート電極を形成する工程と、半導体基板上に第1の金属を堆積する工程と、第1の熱処理により第1の金属と半導体基板を反応させて、前記ゲート電極両側の前記半導体基板表面に金属半導体化合物層を形成する工程と、金属半導体化合物層中に、Siの原子量以上の質量を有するイオンをイオン注入する工程と、金属半導体化合物層上に第2の金属を堆積する工程と、第2の熱処理により、第2の金属を金属半導体化合物層中に拡散させることで、金属半導体化合物層と半導体基板の界面に、第2の金属を偏析させて界面層を形成する工程を有することを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置

【課題】層間絶縁膜を厚くしなくてもソース配線の外にドレイン配線を引き出せ、かつ、LOCOS酸化膜や層間絶縁膜などの絶縁膜の絶縁破壊を防止できるようにする。

【解決手段】素子部8から配線引出し部9に延設されるようにn-型ドリフト層4の裏面に裏面電極19を備え、この裏面電極19とソース配線18との間に電流が流れるような構造、つまりn-型ドリフト層4の表裏を貫通して縦方向に電流を流す構造にする。そして、裏面電極19を配線引出し部9まで延設し、n+型コンタクト領域21、配線引出し部9のn-型ドリフト層4、nウェル領域20およびn+型コンタクト領域21を通じてドレイン配線23と接続する。すなわち、裏面電極19を通じて電流が流れるようにすることにより、ドレイン配線23を素子部8の外に引き出した構造とする。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法に関し、光吸収膜を利用して実行する新たな製造方法を提供する。

【解決手段】基板上に光吸収膜を堆積し、前記光吸収膜を加工して、第1の膜厚の前記光吸収膜で覆われた第1領域と、前記第1の膜厚よりも薄い第2の膜厚の前記光吸収膜で覆われた第2領域と、前記第2の膜厚よりも薄い第3の膜厚の前記光吸収膜で覆われた第3領域とを形成し、前記基板に光を照射することにより、前記基板をアニールすることを特徴とする半導体装置の製造方法。

(もっと読む)

半導体装置の製造方法

【課題】歪み技術を利用した性能のよい半導体装置を低コストで製造する。

【解決手段】シリコン基板10上のnMOS形成領域12a及びpMOS形成領域12bにそれぞれゲート電極15a,15bを形成し、pMOS形成領域12bを覆い、フォトレジストマスク18を形成して、イオン注入によりnMOSのソース/ドレイン領域17aを形成するとともに、ゲート電極15aをアモルファス化し、フォトレジストマスク18を除去した後に、シリコン基板10上に、ゲート電極15a,15bを覆うように、引っ張り歪みを有するキャップ膜19を形成し、nMOS形成領域12aを覆うようにフォトレジストマスク20を形成し、pMOS形成領域12bのキャップ膜19に不純物をイオン注入し、フォトレジストマスク20を除去した後に、アニール処理を行い、nMOSのゲート電極15a下のチャネルに対し、チャネル深さ方向の圧縮歪みを加える。

(もっと読む)

半導体装置及びその製造方法

【課題】Wを材料とする接続部の下地膜の形成工程として、形成容易なプロセスを選択することができ、下層のCu配線である第1の配線のCuの浸食を抑制することにより、第1の配線と接続部との間における接触抵抗を低く抑えるとともにその均一性を高め、信頼性の高い半導体装置を実現する。

【解決手段】熱CVD法によりWF6、H2及びB2H6を含有し、シラン系ガスを含有しない第1の供給ガスを用いてW膜18aを形成した後、WF6及びH2を含有する第2の供給ガスを用いてW膜18bを形成し、CMPを経て、ビア孔16をW膜18で充填するWプラグ19を形成する。

(もっと読む)

アンチヒューズ素子、およびアンチヒューズ素子の設定方法

【課題】2値よりも多い情報を記録可能にしたアンチヒューズ素子を提供する。

【解決手段】複数のMOSトランジスタと、複数のMOSトランジスタのソース電極が共通に接続された第1の電極と、複数のMOSトランジスタのゲート電極が共通に接続された第2の電極と、複数のMOSトランジスタのドレイン電極の少なくとも1つと接続される第3の電極と、ドレイン電極および第3の電極の間に設けられた絶縁膜と、を有する。そして、上記絶縁膜においてドレイン電極に対応して少なくとも1箇所が絶縁破壊されることで、絶縁破壊された部位に対応するドレイン電極と第3の電極とが導通する構成である。

(もっと読む)

導電性クラッディング部を有する、ドープされた半導体ラインを含む集積回路

【課題】メモリセルアレイのメモリセルを選択する配線の抵抗率を低減することにより、配線中の電圧降下を低減し、消費電力を低減する半導体ラインの構造を提供する。

【解決手段】集積回路は、各メモリセルのアレイと半導体基板内に形成されたドープされた各半導体ライン202とを含む。上記ドープされた各半導体ライン202は、各メモリセルのロウに結合されている。上記集積回路は、上記ドープされた各半導体ライン202に接触している導電性クラッディング部203を含む。

(もっと読む)

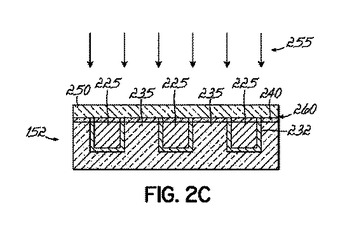

半導体デバイスにおいてゲート電極高を調整するための方法

高エネルギー注入プロセス(203)中に、高度な半導体デバイス(200)のゲート電極構造(252)上に注入ブロック材料(258)を設けることによって、トランジスタ(250A,250B)のチャネル領域(255)に対する必要な遮蔽効果を得ることができる。後の製造段階において、層間絶縁材料(210)の堆積時のプロセス条件を向上させるために、注入ブロック部分(258)が除去されてゲート電極高さ(253H)が所望の高さに低減され、これにより、高密度のデバイス領域であっても、層間絶縁材料(210)内にボイドなどの不規則性が形成されるリスクを大幅に低減することができる。  (もっと読む)

(もっと読む)

埋め込み配線の形成方法

【課題】配線抵抗が低く、EM耐性及び信頼性に優れた埋め込み配線の形成方法を提供することにある。

【解決手段】半導体基板10上に形成された絶縁層11内に溝12を形成した後、溝12の側面及び底面を覆うように、絶縁層11上にALD法でバリアメタル層13を形成し、その表面に、イオン注入法またはALD法により不純物層14、17を形成する。その後、バリアメタル層13と不純物層14、17とを合金化した後、溝12内にCuシード層15及びCuメッキ層16からなる埋め込み配線層を形成し、然る後、合金化されたバリアメタル層13内の不純物元素を埋め込み配線層内に熱拡散させる。

(もっと読む)

半導体装置及びその製造方法

【課題】同一配線層の配線間における実効誘電率の増大及び配線幅のばらつきの増加を解消しつつ、ナノホールパターンの形成時における反射率差に起因する課題と、エッチングによる配線信頼性低下の課題とを同時に解決できるようにする。

【解決手段】半導体装置は、半導体基板の主面に垂直な方向に筒状に延びる複数の空間部である第1のナノコラム型ホール11bを有する第1の層間絶縁膜11と、該第1の層間絶縁膜11に選択的に形成された下層配線12とを有している。下層配線12の上部には、金属又は金属を含む材料からなるキャップ膜12cが形成されている。

(もっと読む)

半導体装置の製造方法

【課題】ドライエッチングによるアルミニウム配線形成後、反応生成物を除去することにより、エレクトロマイグレーション、ストレスマイグレーションの少ない、信頼性の高い半導体装置の製造方法を提供する。

【解決手段】基板11上に、絶縁膜12を介してアルミニウム膜17を形成する。アルミニウム膜をマスク材18を用いてドライエッチングし、アルミニウム配線15を形成する。マスク材を除去した後、アルミニウム配線の少なくとも側壁に形成された反応生成物19にArをイオン注入し、反応生成物に欠陥を発生させる。ウェットエッチングによりアルミニウム配線の表層をエッチングし、反応生成物を浮き上がらせて剥離する。

(もっと読む)

半導体装置及びその製造方法

【課題】FEOLレベルから正負とも低電圧の範囲で拡散工程中のチャージアップから被保護素子を保護し、且つ、拡散工程完了後は被保護素子の駆動に必要な正負両極性の高電圧を被保護素子に印加することが可能な半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11に形成され、被保護素子電極22を有する被保護素子21と、半導体基板11と電気的に接続された基板接続電極42を有する基板接続部41と、被保護素子電極22と基板接続電極42との間に形成されたヒューズ素子電極32を有するヒューズ素子部31とを備えている。ヒューズ素子電極32は、所定の電流を流すことにより切断可能に形成され、ヒューズ素子電極32が切断されていない状態において、被保護素子電極22、基板接続電極42及びヒューズ素子電極32は、一体に形成された導電膜15からなる。

(もっと読む)

半導体デバイスにおける電気漏れ特性の改善及びエレクトロマイグレーションの抑制を行う方法

本明細書には概して半導体デバイスにおける電気漏れ特性の改善及びエレクトロマイグレーションの抑制を行う方法が記載されている。  (もっと読む)

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】抵抗体の高抵抗化を妨げることなくレイアウト面積を小さくできるようにした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】シリコン基板1にSTI層3を形成する工程と、STI層3を介してシリコン基板1上に第1ポリシリコン膜を形成する工程と、第1ポリシリコン膜を所定形状にパターニングして抵抗体11を形成する工程と、抵抗体11を覆うようにシリコン基板1上にシリコン酸化膜13を形成する工程と、シリコン酸化膜13を覆うようにシリコン基板1上に第2ポリシリコン膜を形成する工程と、第2ポリシリコン膜にドライエッチングを施して、抵抗体11の側面に沿ってバイアス用電極15を形成する工程と、を含む。

(もっと読む)

半導体装置およびその製造方法

【課題】 抵抗体を備えた半導体装置の小型化、集積化を図ること。

【解決手段】 半導体基板の表面に、半導体基板とは逆の導電型であるエピタキシャル層を形成し、抵抗となる部分以外にトレンチを形成し、前記トレンチに絶縁膜を埋め込むことで互いに分離された抵抗体を3次元的に形成する。

(もっと読む)

101 - 120 / 246

[ Back to top ]