Fターム[5F033QQ59]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入の対象 (894) | 導電膜 (246)

Fターム[5F033QQ59]に分類される特許

21 - 40 / 246

半導体装置の製造方法

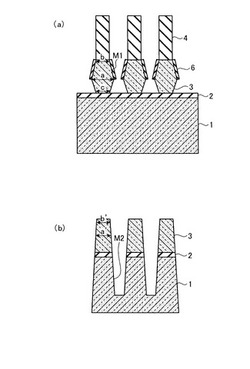

【課題】シリコン膜のエッチング時に膜厚方向中央部での括れの発生を防止する。

【解決手段】多結晶シリコン膜3の上部と下部はノンドープ層3a、3cにてそれぞれ構成され、多結晶シリコン膜3の中央部は不純物ドープ層3bにて構成され、多結晶シリコン膜3に凹部M1を形成した後、多結晶シリコン膜3の酸化処理にて凹部M1の表面にシリコン酸化膜6を形成し、凹部M1下の多結晶シリコン膜3を除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】多結晶シリコンプラグと上層の導体プラグとの界面に十分な膜厚の金属シリサイド層を形成してコンタクト抵抗の低減を図る。

【解決手段】多結晶シリコンプラグを形成した後、多結晶シリコンプラグの表面からゲルマニウムイオン注入を実施してゲルマニウム含有多結晶シリコン16Gとし、その後、シリサイド化可能な金属膜を成膜して金属シリサイド層19を形成し、金属シリサイド19上に導体膜(バリア膜20、W膜21)を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】パッドと当該パッドの下地との密着性の向上および信頼性の向上を図ることが可能な半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板1の一表面側に熱酸化膜1bとシリコン窒化膜32と層間絶縁膜50とパッシベーション膜60との積層構造を有する半導体装置であって、熱酸化膜1b上にパッド80を形成してある。半導体装置の製造方法では、半導体基板1の上記一表面側に熱酸化膜1bと熱酸化膜1bの表面の一部を覆うシリコン窒化膜32とを有する基本構造を形成してから、半導体基板1の上記一表面側に層間絶縁膜50を形成する。基本構造の形成にあたっては、シリコン窒化膜32のうち熱酸化膜1bにおけるパッド80の形成予定領域に形成した部分を除去する。層間絶縁膜の形成後であってパッド80の形成前に層間絶縁膜50のうち熱酸化膜1bにおけるパッド80の形成予定領域上に形成されている部分を除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】工程数を削減して生産性を向上できる構造の半導体装置およびその製造方法を提供する。

【解決手段】半導体装置の製造方法は、半導体層1にトレンチ20を形成する工程と、トレンチ2の内壁およびトレンチ2外の表面を覆うように半導体層1上に絶縁膜3を形成する工程と、トレンチ2を埋め尽くし、トレンチ2外の絶縁膜3上に堆積されるように導電性のポリシリコン膜4を形成する工程と、トレンチ2内、およびトレンチ2外の絶縁膜3上の所定領域にポリシリコン膜4が残るように、当該ポリシリコン膜4を選択的に除去するポリシリコンエッチング工程とを含む。

(もっと読む)

パターン化金属膜及びその形成方法

【課題】ドライエッチングが困難な遷移金属の膜を、サイドエッチングが極力生じないようにパターニングする。

【解決手段】絶縁膜の上にバリア層・密着層を形成し(S1)、その上に遷移金属からなるシード層を形成する(S2)。シード層の上にSiO2膜及びフォトレジスト膜を順次形成し(S3、S4)、フォトレジスト膜、SiO2膜をパターニングして開口を形成し(S5,S6)、開口内にCu膜及びマスクAl膜を積層する(S7、S8)。次に、SiO2膜をエッチング(S9)、露出したシード層をその膜厚方向に異方的に改質し(S10)、改質されたシード層、露出したバリア・密着層、及びマスクAl膜を順次エッチングにより除去することにより(S10〜S13)、パターン化金属膜を得る。

(もっと読む)

埋没ジャンクションを有する垂直型トランジスタ及びその形成方法

【課題】ドーパントの濃度をより高く確保しつつも、ドーパントが拡散されるジャンクション深さを制御することができ、改善された接触抵抗を実現し、チャネル領域との離隔間隔を減らしてチャネルのしきい電圧(Vt)を改善できる埋没ジャンクションを有する垂直型トランジスタ及びその形成方法を提供すること。

【解決手段】半導体基板に第1の側面に反対される第2の側面を有して突出した壁体)を形成し、壁体の第1の側面の一部を選択的に開口する開口部を有する片側コンタクトマスクを形成した後、開口部に露出した第1の側面部分に互いに拡散度が異なる不純物を拡散させて第1の不純物層及び該第1の不純物層を覆う第2の不純物層を形成することを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】縦型トランジスタの特性を悪化させることなく縦型トランジスタの設置面積を削減できる高集積化に適した半導体装置およびその製造方法を提供する。

【解決手段】一定の間隔を空けて配置された複数のピラー30が備えられ、複数のピラー30が、縦型トランジスタTのチャネルとして機能する半導体層からなるチャネルピラー1と、不純物拡散層からなり、前記チャネルピラー1の下部に接続されて縦型トランジスタTの一方のソースドレインとして機能する下部拡散層4に電気的に接続された引き上げコンタクトプラグ2とを含む半導体装置とする。

(もっと読む)

半導体装置の製造方法

【課題】より視認が容易なアライメントマークを簡素な工程で形成することが可能な、半導体装置の製造方法を提供する。

【解決手段】半導体基板SUBの主表面上に、主表面に対して段差を有するパターンMKが形成される工程と、パターンMK上に、半導体材料を含む第1の半導体層PS1が形成される工程と、第1の半導体層PS1上に、半導体材料を含む第2の半導体層PS2が形成される工程と、第2の半導体層PS2上にレジストパターンRSが形成される工程とを備えている。レジストパターンRSが形成される工程において、パターンMKが位置合わせマークとして用いられる。

(もっと読む)

薄膜トランジスタ基板の製造方法

【課題】透明導電膜にピンホール等の欠陥が生じたとしても金属導電膜の腐食を抑制し、透明導電膜と金属導電膜との間の導通を確実にとることが可能な薄膜トランジスタ基板の製造方法を提供すること。

【解決手段】金属導電膜としてのゲート端子121、ドレイン端子122上にOC−SiN膜109を形成し、ゲート端子121及びドレイン端子122が露出するようにコンタクトホールを形成し、コンタクトホールを介してゲート端子121及びドレイン端子122に接触するようにITO膜を成膜してパターニングし、ITO膜に対して酸化膜形成処理を行う。これにより、ITO膜にピンホール等の欠陥が発生していた場合には、欠陥を介してITO膜下のゲート端子121ドレイン端子122の一部が酸化されて酸化膜が形成される。

(もっと読む)

半導体装置の製造方法

【課題】容量コンタクトパッドと容量コンタクトプラグが一体となった構造を形成する。これにより、従来は2回、必要だったフォトリソグラフィ工程を1回に削減して、製造コストを低減する。

【解決手段】半導体装置の製造方法では、層間絶縁膜上に、開口を有するマスクパターンを形成する。このマスクパターンを用いて、層間絶縁膜をエッチングすることにより、開口の下の層間絶縁膜内に容量コンタクトホールを形成する。湿式エッチングにより、マスクパターン内の開口を大きくした後、開口内に導電材料を埋め込むことにより、それぞれ容量コンタクトプラグ及び容量コンタクトパッドを形成する。この後、容量コンタクトパッド上にキャパシタを形成する。

(もっと読む)

半導体装置の製造方法

【課題】隣接する活性領域の間で横方向に成長するシリコン膜が連結されることを防ぎつつ、活性領域上に十分な厚みのシリコン膜を形成可能とした半導体装置の製造方法を提供する。

【解決手段】ゲート電極6aを挟んだ両側の活性領域5上に第1のシリコン膜12aを選択的にエピタキシャル成長させる工程と、複数のワード配線層WLの各間に第1のシリコン膜12aを覆うのに十分な厚みでマスク絶縁膜を埋め込んだ後、このマスク絶縁膜を第1のシリコン膜12aの表面が露出するまでエッチングにより除去する工程と、第1のシリコン膜12a上に第2のシリコン膜12bを選択的にエピタキシャル成長させる工程とを含む。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト抵抗を低減する半導体装置およびその製造方法を提供する。

【解決手段】実施の形態の半導体装置は、シリコンを含む半導体基板10上の層間絶縁膜11に形成されたコンタクトホール12の底部14に形成され、コンタクトホール12に形成されるコンタクトプラグ21と電気的に接続するニッケルシリサイド膜18を有する。このニッケルシリサイド膜18は、ニッケルシリサイド膜18とコンタクトプラグ21の界面18aが半導体基板10と層間絶縁膜11の界面10aより高い。

(もっと読む)

エッチング方法及びエッチング装置

【課題】銅を、異方的にエッチングすることが可能なエッチング方法を提供すること。

【解決手段】表面にマスク材102が形成された銅膜101の周囲を、有機化合物ガス22雰囲気とする工程と、有機化合物ガス22雰囲気中で、銅膜101に、マスク材102をマスクに用いて酸素イオン6を照射し、銅膜101を異方性エッチングする工程と、を具備する。

(もっと読む)

エッチング方法及びエッチングシステム

【課題】スループット良く、銅を、異方的にエッチングすることが可能なエッチング方法を提供すること。

【解決手段】 表面にマスク材102が形成された銅膜101に、マスク材102をマスクに用いて酸素イオン6を照射し、銅膜101内に、銅膜101の厚さ方向の全てに対して異方的に酸化された酸化銅103を形成する工程と、異方的に酸化された酸化銅103をエッチングする工程と、を具備する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】メモリセル間の短絡を防止した上で、活性領域上にシリコン膜が十分に形成された半導体装置を提供する。

【解決手段】半導体基板2の表層に埋め込み形成された素子分離膜8によって、活性領域7が区画された半導体装置1であって、前記活性領域7の側面17が露出するように、前記素子分離膜8の上面の一部が除去されて設けられた凹部と、前記凹部を埋め込みつつ、前記活性領域7の上面7d及び前記側面17と接するように設けられたシリコン膜10と、を有することを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】高さのばらつきが低減された埋め込みビット線を有する半導体装置を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、半導体基板内にビット線とワード線を有する半導体装置の製造方法において、半導体基板をエッチングして第1の方向に延在する第1の溝を形成することによって、複数の第1の半導体ピラーを形成する工程と、第1の半導体ピラーの側面の一部に拡散層を形成する工程と、隣接する前記第1の半導体ピラー間の前記第1の溝に、拡散層に接続するビット線を形成する工程と、第1の半導体ピラーと前記ビット線を覆う第1の絶縁膜を形成する工程と、第1の半導体ピラーの少なくとも一部が露出するように前記第1の絶縁膜に、第1の方向に直交する第2の方向に延在する第2の溝を形成する工程と、露出した第1の半導体ピラー上にエピタキシャル層を成長させて第2の半導体ピラーを形成する工程と、を有することを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】サリサイド構造を有するMIS型電界効果トランジスタにおいて、ゲート電極とソース・ドレインコンタクトとの間の短絡を防止する。

【解決手段】ゲート電極175上にはシリサイド層230が形成されている。シリサイド層230の上面は、シリサイド層230の中央から両端に向けて低くなっており、当該両端におけるシリサイド層230の上面の高さは、オフセットスペーサ180の高さ以下である。

(もっと読む)

半導体装置

【課題】導電膜を有する半導体装置は、導電膜の内部応力の影響を受ける。内部応力について検討する。

【解決手段】単結晶シリコン基板に形成されたnチャネル型MOSFETを有する半導体装置において、チャネル形成領域が引っ張り応力を受けるように、導電膜には不純物が導入され、単結晶シリコン基板に形成されたpチャネル型MOSFETを有する半導体装置において、チャネル形成領域が圧縮応力を受けるように、導電膜には不純物が導入されている。

(もっと読む)

半導体装置及びその製造方法

【課題】第1のコンタクトプラグのゲート電極への短絡を防止する。第1の不純物拡散層と第1のコンタクトプラグの接続抵抗、及び第1と第2のコンタクトプラグの接続抵抗を低減することにより、縦型MOSトランジスタのオン電流を増加させる。

【解決手段】シリコンピラー上部に、非晶質シリコン層及び単結晶シリコン層を形成する。次に、2度の選択エピタキシャル成長法により、シリコンピラー上に順に非晶質シリコン層、及び非晶質シリコンゲルマニウム層を形成する。この後、熱処理により、シリコンピラー上部に単結晶シリコン層を有する第1の不純物拡散層を形成すると同時に、シリコンピラー上に単結晶シリコン層及び多結晶シリコンゲルマニウム層を有する第1のコンタクトプラグを形成する。次に、第1のコンタクトプラグに接続されるように、金属から構成される第2のコンタクトプラグを形成する。

(もっと読む)

半導体装置

【課題】SRAM回路の動作速度を向上させる。

【解決手段】駆動MISFETと転送MISFETとそれらの上部に形成された縦型MISFETとでメモリセルを構成したSRAMにおいて、周辺回路を構成するMISFET間の電気的接続を、メモリセルの縦型MISFET(SV1、SV2)よりも下部に形成されるプラグ28および中間導電層46、47で行うとともに、縦型MISFET(SV1、SV2)よりも上部に形成されるプラグ、第1および第2金属配線層を用いて行うことにより、配線の自由度を向上でき、高集積化できる。また、MISFET間の接続抵抗を低減でき、回路の動作スピードを向上できる。

(もっと読む)

21 - 40 / 246

[ Back to top ]