Fターム[5F033QQ59]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入の対象 (894) | 導電膜 (246)

Fターム[5F033QQ59]に分類される特許

161 - 180 / 246

実質的に均一なパターン密度で形成された回路を有する半導体デバイス

半導体デバイスは、導電層から形成された少なくとも3つの導電配線(202、204、206)に結合された少なくとも1つのトランジスタ(T1)を有する第1の回路部分(200A)を含む。3つの導電配線のうちの1つ(204)は前記少なくとも1つのトランジスタの制御端子を形成する。また、第2の回路部分(200B)は、少なくとも2つのトランジスタ(T3−T6)を含む。該少なくとも2つのトランジスタの各々は、同一の導電層から形成された導電配線(234、236、238、240)によって形成された制御端子を有する。第1の回路部分の前記3つの導電配線は、第2の回路部分の導電配線群と同一のピッチパターンを有する。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】本発明はトランジスタのソース・ドレイン拡散層と配線を多結晶シリコンによって接続したコンタクトプラグを有する半導体装置に関し、特に拡散層中に残留する欠陥を低減して接合リーク電流を減少できる半導体装置を提供する。

【解決手段】本発明の半導体装置は、トランジスタのソース拡散層及び又はドレイン拡散層へのコンタクトが多結晶シリコンのコンタクトプラグである半導体装置において、前記ソース拡散層及び又はドレイン拡散層と多結晶シリコンのコンタクトプラグの間に格子間シリコンまたは空孔の拡散を防止する拡散防止膜を形成した。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体基板上に形成された配線層間を通してスルーホールを形成する際に、アライメントズレによって発生する配線層とスルーホールとの接触に起因する電気的なショートに対するマージンを拡大する。

【解決手段】半導体基板100上に絶縁膜101を堆積する工程と、絶縁膜上に導電膜102を堆積する工程と、導電膜にドライエッチング処理を実施して配線パターン105を形成する工程と、配線パターンを覆うように保護絶縁膜110を堆積する工程と、保護絶縁膜中に配線パターンの間を通すようにスルーホール111を形成する工程と、スルーホール内にプラグ112を形成する工程とを含み、配線パターンの上部の寸法を配線パターンの下部の寸法に比べて小さくすることで、配線パターンの上部間のスペース幅が配線パターンの下部間スペース幅より大きくする。

(もっと読む)

電気光学装置、電気光学装置の製造方法、及び電子機器

【課題】製造工程が増加せず製品コストの高騰を抑制すると共に、製造工程中に蓄積された電荷による静電気破壊から配線膜を保護する。

【解決手段】TFT基板10上の画素領域の周辺に設けられている周辺領域に、信号線膜200と、この信号線膜200の上層であって信号線膜200に対して交差する方向に配設されている配線膜201と、この信号線膜200と配線膜201との間に絶縁膜41',42'を介して介装されると共に平面視において少なくとも信号線膜200と配線膜201との交差する領域に配設されているシールド膜203とを備え、このシールド膜203が、画素領域において形成される蓄積容量70の下部電極71と同一の層であって、この下部電極71をパターンニングする際に同時に形成される。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を短縮することにより、歩留りを向上し、装置の信頼性を高める。

【解決手段】シリコン基板100上の第1主面101上に酸化膜102を形成し、この酸化膜102上に第1ポリシリコン層104a、及びその上層にキャップ絶縁膜106aを具えた島状積層体108を形成する。次に、第1主面101の島状積層体108を含む上側全面に第2ポリシリコン層110を形成して、島状積層体108の側壁で第1ポリシリコン層104aと第2ポリシリコン層110とを接合させる。その後、一回の拡散処理によって、第2ポリシリコン層110の表面から第2ポリシリコン層110内部に不純物を拡散させるとともに、第2ポリシリコン層110に拡散された不純物をさらに第1ポリシリコン層104aの側壁から第1ポリシリコン層104aの内部に向かって、拡散させる。

(もっと読む)

半導体集積回路装置

【課題】複数層の埋め込み配線を有する半導体集積回路装置において、埋め込み配線と底部にて接続するプラグとその埋め込み配線との界面でのストレスマイグレーションによる導通不良を防ぐ。

【解決手段】たとえば、Cu配線33Wの幅が約0.9μm以上かつ約1.44μm未満であり、Cu配線43の幅およびプラグ43Pの径が約0.18μmである場合において、Cu配線33W上にてCu配線33WとCu配線43とを電気的に接続するプラグ43Pを2個以上配置する。

(もっと読む)

不揮発性半導体記憶装置およびその製造方法

【課題】コンタクトホールをワード線上に精度良く開口できない場合でも、周辺回路からの電気信号がワード線を介して確実に制御ゲートに伝達される構造の不揮発性半導体記憶装置およびその製造方法を提供すること。

【解決手段】半導体基板上に複数本のワード線(10_1,…)と複数本のビット線(20_1,…)とが配置され、ワード線とビット線との交差部にメモリセルを有している。ワード線と上層の金属配線とのコンタクト部においては、ワード線(たとえば10_2)を形成するポリシリコンの下部に、コンタクト部(たとえば12_2)を包含するポリシリコン領域100_2が、コンタクトを形成する際のエッチングストップ層として形成される。

(もっと読む)

半導体装置の製造方法

【課題】 フォトレジストパターンをマスクとして下地膜をエッチングする際に、適正なパターンを形成することが可能な半導体装置の製造方法を提供する。

【解決手段】 第1の膜16上にフォトレジストパターン18を形成する工程と、フォトレジストパターンをマスクとして用いて、第1の膜に第1の膜のエッチングレートを高める所定の注入物を注入し、第1の膜に注入層16aを形成する工程と、フォトレジストパターンをマスクとして用いて、注入層の少なくとも一部である第1の膜の第1の部分をエッチングする工程とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】コーナーラウンディング現象に起因するゲート電極寸法の変化及びトランジスタ特性の劣化を防止することができるゲート電極を備えた半導体装置及びその製造方法を提供する。

【解決手段】半導体装置は、素子分離領域102と、素子分離領域102に囲まれた活性領域103と、素子分離領域102及び活性領域103上に形成されたゲート電極105とを備える。素子分離領域102上のゲート電極105における上面のゲート長方向の線幅LbTは、活性領域103上のゲート電極105における上面のゲート長方向の線幅LaTとほぼ等しく、素子分離領域102上のゲート電極105における下面のゲート長方向の線幅LbBは、活性領域103上のゲート電極105における下面のゲート長方向の線幅LaBよりも長い。

(もっと読む)

半導体装置およびその製造方法

【課題】分離絶縁膜上の配線と、この配線の側面上に形成されたサイドウォールと、配線と活性領域上の不純物拡散とを接続するシェアードコンタクトを備えた半導体装置であっても、シェアードコンタクから半導体基板へのリーク電流の発生を抑制することができる半導体装置およびその製造方法を提供する。

【解決手段】本発明に係る半導体装置は、半導体基板100の主表面上に選択的に形成された分離絶縁膜と、半導体基板100の主表面上において、分離絶縁膜20Aにより規定される活性領域2cと、分離絶縁膜上にて、活性領域3bに達する凹部50と、凹部50を覆うように形成された第1絶縁膜10Aと、第1絶縁膜10A上に形成され、凹部50を充填し、第1絶縁膜10Aと材質の異なる第2絶縁膜10Bと、凹部50と隣り合う位置の活性領域2cの主表面上に形成された不純物拡散層2c1と、不純物拡散層2c1上に形成された導電膜とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】リソグラフィの解像限界以下の配線パターンと、それ以外の任意の寸法の配線パターン等を簡易に形成することが可能な半導体装置の製造方法を提供する。

【解決手段】被エッチング部材であるポリシリコン膜25上に第1ハードマスク30が形成され、更にこの上にアモルファスシリコンからなる第2ハードマスク40が形成される。第2ハードマスク40の所望の一部にボロン等のイオン注入を行った後、第2ハードマスク40をマスクとして第1ハードマスク30をエッチングする。ウエットエッチングにより第2ハードマスク40のイオン注入されていない部分をエッチング除去する。第1ハードマスク30の側壁に側壁膜70を形成した後、第2ハードマスク40に覆われず上部が露出している第1ハードマスク30を選択的にエッチング除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】PN接合の太陽電池効果による配線の腐食及び再堆積を抑制する。

【解決手段】半導体装置は、Pウェル103上に形成されたN型不純物拡散層106とNウェル104上に形成されたP型不純物拡散層108とを電気的に接続するシェアードコンタクト111を備えている。

(もっと読む)

半導体装置及びその製造方法

【課題】 簡易な製法によって製造が可能で、エレクトロマイグレーション耐性に優れ、簡易な製法によって製造が可能な配線層を備える半導体装置、及びその製造方法を提供する。

【解決手段】 下地絶縁膜2上にAl合金を堆積して初期配線層3を形成した後、初期配線層3の表層部分にAlイオンを注入する。このとき、ウェハを回転させることで初期配線層3の表面外周部分にAlイオンを注入し、これによって当該部分をアモルファス化する。その後、熱処理工程を行い、アモルファス層を再結晶化して結晶粒径の小さい第2配線層7を外周部分に形成すると共に、初期配線層3を構成する結晶粒4の結晶成長を誘発して結晶粒径の大きい第1配線層8を内層部分に形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】接触抵抗の低減されたポリシリコンプラグを有する半導体装置及びその製造方法を提供する。

【解決手段】半導体基板上の絶縁層に形成されたホール中に、ポリシリコンプラグが埋めこまれた構造を有する半導体装置の製造方法において、半導体基板上の絶縁層にホールを形成する工程と、前記ホールを埋めるようにポリシリコンを形成させるポリシリコン形成工程と、前記ポリシリコンを、水素雰囲気下で加熱する水素ベーク工程と、を具備する。

(もっと読む)

シリサイド・コンタクトとその上のメタライゼーションとの間の接触抵抗を低減する方法及び構造体

【課題】シリサイド・コンタクトとその上のメタライゼーションとの間の接触抵抗を低減する方法及び構造体を提供する。

【解決手段】上に配置される少なくとも1つの電界効果トランジスタを含み、前記少なくとも1つの電界効果トランジスタに隣接して配置されるシリサイド・コンタクト領域16A,16B,16Cを含む、半導体基板12と、前記半導体基板上に配置され、前記少なくとも1つの電界効果トランジスタの上に延び、前記シリサイド・コンタクト領域を露出させるコンタクト開口部20を有する絶縁中間層18と、前記コンタクト開口部内の金属ゲルマニウム化物含有コンタクト材料24とを備える。

(もっと読む)

改善されたコンタクトヒューズを備えた半導体デバイス

本発明の1つの態様は、集積回路(IC)(400b)を提供する。ICは、トランジスタ(410b)及びコンタクトヒューズ(422b)を含む。コンタクトヒューズは各々導電層(424b)を含み、錐体形コンタクト(426b)は、導電層に接触する狭い端部と、導電層上に配置される第1の金属層(427b)とを有する。錐体形コンタクトの広い端部は第1の金属層に接触する。錐体形コンタクトは、約1.2以上である、狭い端部に対する広い端部の開口の比を有する。コンタクトヒューズは各々、第1の金属層上に配置されて接触するヒートシンク(432b)を更に含む。 (もっと読む)

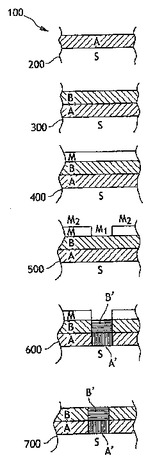

特性が制御された多層構造物の製造方法

本発明はn層の所定材料の元素状活性層(nは2以上の整数)を含む多層構造物を支持体上に製造する方法(100)に関する。この方法は、第1の元素状材料活性層の成膜工程(200)と、n番目の元素状材料活性層の成膜工程(300)とを含む方法であって、特性が制御された多層構造物を得るために、成膜されたn層の材料元素状活性層上に、n層の元素状活性層のそれぞれの個々の特性を変性させるのに適したイオン種をレジストを介して注入する単一の工程(600)を含むことを特徴とする。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタ等のデバイスを構成する各層の結晶配向に優れた半導体装置を提供する。

【解決手段】本発明の半導体装置は、基板10上の層間絶縁膜26に形成された貫通孔24内に設けられてなるプラグ20を介した導電接続構造を具備した半導体装置であり、前記プラグ20が前記貫通孔24内に第1導電膜を埋め込んでなるプラグ導電層22を有しており、少なくとも前記プラグ導電層22上には、シリコンからなる第2導電膜21と、自己配向性を有する導電材料からなる窒化チタン層12とが積層されている。

(もっと読む)

半導体装置およびその製造方法

【課題】配線のマイグレーション耐性を向上させるとともに、シリコンの配線内部への拡散を抑制する。

【解決手段】半導体装置100は、シリコン基板101、シリコン基板101上に設けられ、SiCN膜103、SiOC膜105およびSiO2膜107からなる第一絶縁膜、当該第一絶縁膜中に設けられ、主として銅含有金属からなる第一銅配線111、を含む。第一銅配線111の内部の表面近傍に、シリコンが導入されたSi−O偏在層115を有し、導入されたシリコンの少なくとも一部が、Si−O結合を形成している。

(もっと読む)

半導体装置

【課題】Cu配線などの金属配線について、金属配線と金属拡散防止膜との密着性が向上し、金属配線のエレクトロマイグレーション耐性向上により金属配線寿命の長い半導体装置を提供する。

【解決手段】半導体基板上に形成された第1の絶縁膜中の溝部内に設けられ、銅および銅の合金のうち少なくとも1つを含有する第1の金属配線と、第1の金属配線および第1の絶縁膜の露出面を覆う第1の金属拡散防止膜を有する半導体装置において、第1の金属配線は金属シリサイド層を含有しないシリコン含有金属配線であり、第1の金属配線全体にシリコンを含む構成である。

(もっと読む)

161 - 180 / 246

[ Back to top ]