Fターム[5F033QQ59]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入の対象 (894) | 導電膜 (246)

Fターム[5F033QQ59]に分類される特許

41 - 60 / 246

半導体装置およびその製造方法

【課題】第1の領域中の層間絶縁膜を湿式エッチングにより除去する際に、使用する薬液が第2の領域に浸透することを防止する。これにより、第2の領域の特性の劣化がない、高性能の半導体装置を提供する。

【解決手段】第1の領域と、第1の領域を囲むように設けられたガードリングと、ガードリングの外側に設けられた第2の領域と、を有する半導体装置。第1の領域は、導電性を有する第1の膜によって構成された第1の電極を有する。第1の領域中の第1の電極の表面は、第2の膜で覆われていない。ガードリングは、凹状の溝の内壁を覆う第1の膜と、凹状の溝の内部において少なくとも第1の膜の表面の一部を覆う絶縁性の第2の膜を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明はビット配線と半導体基板上の不純物拡散層とのコンタクト抵抗を低減した構造の提供を目的とする。

【解決手段】本発明は、半導体基板の一面に形成されたトレンチ溝内に、ゲート絶縁膜を介しゲート電極を含む埋込ワード線とその上に位置する埋込絶縁膜とが埋め込まれ、前記トレンチ溝に隣接する半導体基板一面の表面領域に不純物拡散層が形成され、前記不純物拡散層が形成された領域上にビット配線が形成されるとともに、前記不純物拡散層に接続されたビット配線の少なくとも底部側が、不純物をドープした不純物ドープ型のポリシリコンに更に不純物イオンを打ち込みしてなる注入ポリシリコン膜からなることを特徴とする。

(もっと読む)

配線構造の製造方法及び配線構造

【課題】本発明は、簡素な工程で配線構造を形成することができ、簡素な構成で自由度の高い配線の取り出しが可能な配線構造の製造方法及び配線構造を提供することを目的とする。

【解決手段】接合界面に電荷蓄積が発生する異種材料を積層して積層体を形成し、該積層体の接合界面に2次元電子ガス層を形成する2次元電子ガス層形成工程と、

該2次元電子ガス層を選択的に加熱して該2次元電子ガス層に非導電性領域を選択的に形成し、非加熱の導電性領域とで所定の配線構造を形成する選択的加熱工程と、を含むことを特徴とする。

(もっと読む)

半導体装置

【課題】SRAMのメモリセルの面積を減少させる。

【解決手段】半導体装置は、基板上のメモリセル領域内に設けられた第1活性領域と、第1活性領域と素子分離により分離され、第1活性領域内よりもメモリセル領域の中心に近い位置に設けられた第2活性領域と、第1活性領域を横断する第1ゲート電極と、第1ゲート電極と離間し、第1活性領域および第2活性領域を横断する第2ゲート電極と、第1活性領域で、第1ゲート電極と第2ゲート電極との間の第1ドレイン部と、第2活性領域で、第2ゲート電極の第1ドレイン部側の第2ドレイン部と、第1ドレイン部と第2ドレイン部とを接続する第1配線と、第1ゲート電極および第2ゲート電極と離間し、端部が第1ゲート電極の第2活性領域側の端部と対向する第3ゲート電極と、第2ドレイン部と第3ゲート電極とを接続する第2配線とを備え、第3ゲート電極の上面と第2配線の上面はほぼ同じ高さに形成されている。

(もっと読む)

半導体装置の製造方法

【課題】信頼性の高い半導体装置を高い製造歩留まりで提供し得る半導体装置の製造方法を提供することにある。

【解決手段】側壁にサイドウォール絶縁膜が形成されたゲート配線20を形成する工程と、第1の応力膜38を形成する工程と、第1の応力膜上にエッチングストッパ膜40を形成する工程と、エッチングストッパ膜をエッチングし、第1の応力膜のうちのサイドウォール絶縁膜を覆う部分上にエッチングストッパ膜を選択的に残存させる工程と、第2の領域4を露出する第1のマスクを用いて第2の領域内の第1の応力膜をエッチングする工程と、第2の応力膜42を形成する工程と、第1の領域2を露出する第2のマスクを用いて第1の領域内の第2の応力膜をエッチングする工程と、第1の領域と第2の領域との境界部におけるゲート配線に達するコンタクトホール46aを形成する工程とを有している。

(もっと読む)

カーボンナノチューブ配線及びその製造方法

【課題】カーボンナノチューブを有するプラグ配線において良好な電気的接続を得ることができるカーボンナノチューブ配線及びその製造方法を提供する。

【解決手段】第1配線層12上に層間絶縁膜13が形成され、層間絶縁膜13上に第2配線層14が形成されている。第1配線層12と第2配線層14との間の層間絶縁膜13内にはコンタクト孔15が形成される。コンタクト孔15内には、一端が第1配線層12に接続され、他端が第2配線層14に接続された複数のカーボンナノチューブ16が形成されている。さらに、層間絶縁膜13と第2配線層14との間にはストッパ膜17が形成され、ストッパ膜17の一部は複数のカーボンナノチューブ16の前記他端間に充填されている。

(もっと読む)

電子デバイス

【課題】製造工程数や面積の増大を招くことなく、金属薄膜抵抗の抵抗率を異ならせる素子構造を提案する。

【解決手段】基板に形成された積層構造における絶縁層間の導電膜配置階層の1つに、抵抗素子の抵抗値を規定する抵抗膜5が配置されている。また、抵抗膜5の厚さ方向の少なくとも一方の他の導電膜配置階層に、水素吸蔵金属3が、抵抗膜5と絶縁された状態で、かつ金属抵抗膜の少なくともコンタクトエッジ間の領域の全域と平面視で重なる位置と大きさで配置されている。

(もっと読む)

半導体装置の製造方法

【課題】

微細化したMOSトランジスタを含む半導体装置において、リーク/ショートの可能性を抑制する。

【解決手段】

半導体装置の製造方法は、活性領域上に、ゲート絶縁膜とシリコン膜とを形成し、シリコン膜上方にゲート電極用レジストパターンを形成し、レジストパターンをマスクとして、シリコン膜を厚さの途中までエッチングしてレジストパターン下方に凸部を残し、レジストパターンを除去した後シリコン膜を覆うダミー膜を形成し、ダミー膜を異方性エッチングして、凸部の側壁にダミー膜を残存させつつ、平坦面上のダミー膜を除去し、ダミー膜をマスクとして、シリコン膜の残りの厚さをエッチングしてゲート電極を形成し、ゲート電極両側の半導体基板に、ソース/ドレイン領域を形成し、シリコン領域にシリサイドを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】実用上十分なエレクトロマイグレーション耐性及び動作速度を有する半導体装置を得られるようにする。

【解決手段】半導体基板1の上に第1の絶縁膜2を形成し、第1の絶縁膜2に配線溝3を形成し、配線溝3の内部に金属膜5を埋め込んで第1の配線6を形成し、第1の絶縁膜2及び第1の配線6の上に保護膜7を形成し、第1の配線6と保護膜7との界面に反応層8を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】キャパシタの下部電極のダメージを抑制することができる半導体装置およびその製造方法を提供するものである。

【解決手段】本発明の半導体装置は、立設する複数の電極と、前記電極の立設を保持する第1の絶縁膜と、前記電極が貫通するように前記第1の絶縁膜に形成され、各々の前記電極の外周側面の少なくとも一部に接触する複数の孔部と、前記第1の絶縁膜に形成され、前記複数の孔部のうちその一部の孔部に連結する第1の開口と、前記第1の絶縁膜に形成され、前記複数の孔部のいずれの孔部に対してよりも前記溝部に近接する位置に配置すると共に前記複数の孔部のいずれにも連結しない第2の開口とを、備えたことを特徴とすることを特徴とする。

(もっと読む)

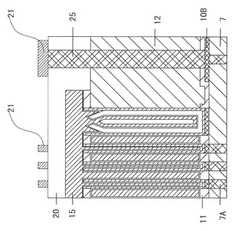

半導体装置及びその製造方法

【課題】高温環境下での絶縁膜の腐食を抑制して、絶縁不良を回避した半導体装置及びその製造方法を提供することことを課題とする。

【解決手段】半導体基板11上にエピタキシャル成長により第1絶縁膜12が積層形成され、この第1絶縁膜12上には、耐熱性の電極13が選択的に形成され、この電極13の上部には、シリカガラスを主成分とする層間絶縁膜14が形成され、この層間絶縁膜14の表面には絶縁バリア膜15が形成され、この絶縁バリア膜15の上には、Alの配線16が形成され、絶縁バリア膜15は、絶縁性の窒化物、炭化物、窒化炭化物の単層膜、多層膜、または混合膜で構成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】絶縁破壊に至らない微量の電荷の蓄積を抑制した半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板11の上に形成された半導体素子1及び保護ダイオード2を備えている。半導体基板11の上には、半導体素子1及び保護ダイオード2を覆うように第1の層間絶縁膜22が形成されている。第1の層間絶縁膜22には、半導体素子1と電気的に接続された第1のプラグ25と、保護ダイオード2と電気的に接続された第2のプラグ23、24とが形成されている。第2のプラグ23、24の上面の面積は、第1のプラグ25の上面の面積よりも大きい。

(もっと読む)

半導体装置及び配線

【課題】低抵抗の電極や配線を有する半導体装置を実現する。

【解決手段】本実施形態による配線は、p型不純物が導入されたp型不純物層部分と、n型不純物が導入されたn型不純物層部分と、p型及びn型不純物が導入された(p+n)型不純物層部分と、を含む半導体層と、少なくとも(p+n)型不純物層部分上に形成されたシリサイド層と、を備え、(p+n)型不純物層部分に含まれるp型不純物とn型不純物の総濃度は、5E20cm−3未満である。

(もっと読む)

半導体装置の製造方法

【課題】 極短時間アニール処理を行う際に、基板自体の損傷を抑制する半導体装置の製造方法を提供する。

【解決手段】 半導体基板上にゲート電極を形成する工程と、前記半導体基板に導電性の不純物を導入する工程と、前記半導体基板及び前記ゲート電極上に保護膜を形成する工程と、前記保護膜を形成後に前記半導体基板の裏面全面を研磨する工程と、前記半導体基板の裏面全面を研磨した後に前記半導体基板の表面が1000℃以上での保持時間が0.1秒以下となるような加熱処理により前記不純物を活性化する工程とを備えることを特徴とする半導体装置の製造方法。

(もっと読む)

信頼性向上のためのケイ化銅パッシベーション

【課題】その表面をケイ化銅に転化することにより、銅相互接続構造の露出銅表面を直接不動態化するための方法を提供すること。

【解決手段】その後の誘電体フィルムの形成とともに原位置に実行されるシラン・パッシベーション・プロセスは、Cu相互接続構造の露出したCu表面をケイ化銅に転化する。ケイ化銅は、Cu拡散およびエレクトロマイグレーションを抑制し、後続導体材料との接触が行われる領域内でバリア材として機能する。銅相互接続構造の銅表面全体をケイ化する場合もあれば、銅表面の一部分を露出するように上に重なる誘電体に開口部を形成した後で表面の局部部分をケイ化する場合もある。

(もっと読む)

薄膜トランジスタの製造方法

【課題】低抵抗なAl配線材料を用いて、生産コストの低下および生産性の向上を図ることができる薄膜トランジスタの製造方法を提供する。

【解決手段】本発明の薄膜トランジスタの製造方法は、Arガスを用いたスパッタリングによって純AlまたはAl合金を第1層として成膜する工程と、前記第1層の上層に、Ar+N2混合ガスまたはAr+NH3混合ガスを用いたスパッタリングによって、前記第1層の材料に加えて窒化アルミニウムも部分的に含む第2層を成膜する工程と、別途形成するコンタクトホールを介して透明膜電極と第1電極の前記第2層とを電気的に接続する工程を含むものである。

(もっと読む)

電界効果トランジスタ

【課題】従来の光学素子に電界効果トランジスタを適用するとき、PN接合部の光リークを抑えるために、トランジスタの周囲に遮光領域を設定する必要が有り、回路面積が大きくなるという課題があった。また、反射光に対して遮光性が十分でないという問題があった。

【解決手段】本発明の電界効果トランジスタは、ゲート電極上に、PN接合部に平面的に重なるように遮光部材を有する。この遮光部材により、PN接合部を遮光することができる。また、電界効果トランジスタ面積が増大しないため、回路の面積を小さく設定できる。

(もっと読む)

半導体装置及びその製造方法

【課題】シェアードコンタクト形成時に、ゲート電極が溶解されて形状異常となるのを防止する。

【解決手段】半導体装置は、基板1上にゲート絶縁膜2を介して形成されたゲート電極31と、基板1のゲート電極31の両側方に形成された不純物領域32及び33とを有するトランジスタと、トランジスタ上を覆うように基板1上に形成された層間絶縁膜11及び12と、不純物領域32及び33及びゲート電極31に電気的に接続するシェアードコンタクト14とを備える。ゲート電極31の側面下部を覆うように第1のサイドウォール5、第1のサイドウォール5におけるゲート電極31とは反対側に第2のサイドウォール6、第1のサイドウォール5上に、ゲート電極31の側面上部と第2のサイドウォール6とに挟まれるように第3のサイドウォール9bが形成されている。第2及び第3のサイドウォール6及び9bは、第1のサイドウォール5とは異なる材料からなる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の性能を向上させる。

【解決手段】半導体基板1に形成したnチャネル型MISFETQnのソース・ドレイン用のn+型半導体領域7bおよびゲート電極GE1上と、pチャネル型MISFETQpのソース・ドレイン用のp+型半導体領域8bおよびゲート電極GE2上とに、ニッケル白金シリサイドからなる金属シリサイド層13bをサリサイドプロセスで形成する。その後、半導体基板1全面上に引張応力膜TSL1を形成してから、pチャネル型MISFETQp上の引張応力膜TSL1をドライエッチングで除去し、半導体基板1全面上に圧縮応力膜CSL1を形成してからnチャネル型MISFETQn上の圧縮応力膜CSL1をドライエッチングで除去する。金属シリサイド層13bにおけるPt濃度は、表面が最も高く、表面から深い位置になるほど低くなっている。

(もっと読む)

金属相互接続線を形成するための方法

【課題】金属相互接続線の形成方法を提供する。

【解決手段】基板にトレンチを画定するエッチング・ステップと、金属の電着によって前記トレンチを充填するステップとを含み、金属の結晶粒で充填された前記トレンチの上に金属侵入層を形成するステップを含み、さらに、トレンチに沿った結晶粒方位の第1の方向と、トレンチに垂直な方向での結晶粒方位の第2の方向とを決定するステップと、前記金属の結晶格子内でのイオン・チャネリングの第3の方向を決定するステップと、前記金属侵入層内でのイオン注入ビームの向きDi1の少なくとも1つの方向を決定するステップと、イオン注入ビームの向きDi1の1つに応じて、侵入層にイオン・ビームによってイオン注入するステップと、を含む。

(もっと読む)

41 - 60 / 246

[ Back to top ]