Fターム[5F033QQ63]の内容

半導体集積回路装置の内部配線 (234,551) | パターン形成方法,基板,導電膜,絶縁膜の処理方法 (47,095) | 不純物導入、イオン注入 (1,611) | 導入、注入するもの (714) | 酸素系 (57)

Fターム[5F033QQ63]に分類される特許

21 - 40 / 57

半導体装置の製造方法

【課題】新規な半導体装置の製造方法を提供する。

【解決手段】SiN層にPおよびOを注入する工程と、前記SiN層に注入されたPおよびOをH2Oと反応させ、前記SiN層をエッチングする工程とを有する方法により、半導体装置を製造する。特に、半導体装置を形成するにあたり、狭スペースで高アスペクト比の溝サイドウォールを形成する工程や、埋め込み型ビット線を形成する工程に、上記のようにSiN層をエッチングすることができる。

(もっと読む)

半導体装置及びその作製方法

【課題】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とソース電極層又はドレイン電極層との間のコンタクト抵抗を低減し、電気特性を安定させた薄膜トランジスタを提供する。また、該薄膜トランジスタの作製方法を提供する。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層より導電率の高いバッファ層を形成し、酸化物半導体層とソース電極層又はドレイン電極層とがバッファ層を介して電気的に接続されるように薄膜トランジスタを形成する。また、バッファ層に逆スパッタ処理及び窒素雰囲気下での熱処理を行うことにより、酸化物半導体層より導電率の高いバッファ層を形成する。

(もっと読む)

配線構造、薄膜トランジスタ基板およびその製造方法、並びに表示装置

【課題】純CuまたはCu合金のCu系合金配線と半導体層との間のバリアメタル層を省略することが可能なダイレクトコンタクト技術であって、幅広いプロセスマージンの範囲においてCu系合金配線を半導体層に直接かつ確実に接続することができる技術を提供する。

【解決手段】本発明の配線構造は、基板の上に、基板側から順に、半導体層と、純CuまたはCu合金のCu系合金膜とを備えた配線構造であって、前記半導体層と前記Cu系合金膜との間に、基板側から順に、窒素、炭素、フッ素、および酸素よりなる群から選択される少なくとも一種の元素を含有する(N、C、F、O)層と、CuおよびSiを含むCu−Si拡散層との積層構造を含んでおり、且つ、前記(N、C、F、O)層を構成する窒素、炭素、フッ素、および酸素のいずれかの元素は、前記半導体層のSiと結合している。

(もっと読む)

半導体装置及びその製造方法、並びに表示装置

【課題】高融点バリアメタル層を形成すること無く、Si膜又はSiを主成分とする膜と良好なコンタクト特性を実現するAl合金膜を提供する。

【解決手段】半導体デバイス(TFT)は、チャネル部11を形成する様にSi半導体膜7上に配設された被酸化のオーミック低抵抗Si膜8と、オーミック低抵抗Si膜8と直接に接続し、且つ、接続界面近傍に、少なくともNi原子、N原子及びO原子を含むアルミニウム合金膜から成る、ソース電極9及びドレイン電極10とを有する。

(もっと読む)

半導体装置、その半導体装置の作製方法及びその半導体装置を有する電子機器

【課題】酸化物半導体を用いた薄膜トランジスタにおいて、電界効果移動度を向上させることを課題の一とする。また、薄膜トランジスタの電界効果移動度を向上させても、オフ電流の増大を抑制することを課題の一とする。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とゲート絶縁層の間に、該酸化物半導体層より導電率が高い酸化物クラスターを形成することによって、該薄膜トランジスタの電界効果移動度を向上させ、且つオフ電流の増大を抑制することができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の結晶欠陥発生を抑制することができる半導体装置の製造方法を提供する。

【解決手段】ウエハ上にSTI用のトレンチを形成し、そのトレンチに絶縁膜を埋め込む。次に、ウエハ表面に酸素を導入する。酸素導入は、酸素100%雰囲気下で、1100℃、60秒間、ウエハ表面にRTO(Rapid Thermal Oxidation)を行う。その後、高温アニールを行う。SRAM製造プロセスにおいて、転位が発生するおそれのある高温アニール工程とソース/ドレイン部のイオン注入工程の前に酸素導入を行うため、ウエハの結晶強度を高めることができ、アニール工程やイオン注入工程によって発生する転位を抑えることができる。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備えた保護回路等が必要となる。

【解決手段】ゲート電極15を被覆するゲート絶縁層37と、ゲート絶縁層37上においてゲート電極15と端部が重畳し、第2酸化物半導体層40と導電層41が積層された一対の第1配線層38及び第2配線層39と、少なくともゲート電極15と重畳しゲート絶縁層37及び該第1配線層38及び該第2配線層39における導電層41の側面部及び上面部の一部と第2酸化物半導体層40の側面部と接する第1酸化物半導体層36とを有する非線形素子30aを用いて保護回路を構成する。

ゲート絶縁層37上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子30aの特性を向上させることができる。

(もっと読む)

半導体素子の微細パターンの形成方法

【課題】複数の物質層間の溶解度差を利用してダブルパターニングを具現する半導体素子の微細パターンの形成方法を提供する。

【解決手段】半導体素子の微細パターンの形成方法は、基板100上に、空間を介して相互に離隔されている複数の第1マスクパターン120を、基板100の主面と平行方向に形成するステップと、溶解剤に対して第1溶解度を有する第1物質からなる複数のキャッピング層130を、複数の第1マスクパターン120のそれぞれの側壁及び上面に形成するステップと、溶解剤に対して第1溶解度より低い第2溶解度を有する第2物質からなる第2マスク層を、空間内に形成するステップと、溶解剤を利用してキャッピング層130を除去し、かつ、第2マスク層の一部を除去した後、空間に残った第2マスク層の残留部分を、複数の第2マスクパターン140Aとして形成するステップと、を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】 ソフトエラーを低減することが可能な半導体装置及びその製造方法を提供することを目的とする。

【解決手段】 電極パッドを有する半導体チップが形成される半導体基板と、前記電極パッドに設けられる内部接続端子と、前記複数の半導体チップと前記内部接続端子とを覆うように設けられる絶縁層と、前記絶縁層を挟んで前記内部接続端子と接続される配線パターンと、を有する半導体装置であって、前記絶縁層は、ポリイミド及び/又はポリイミド系化合物等のα線を遮蔽する材料を含んで構成されることを特徴とする。

(もっと読む)

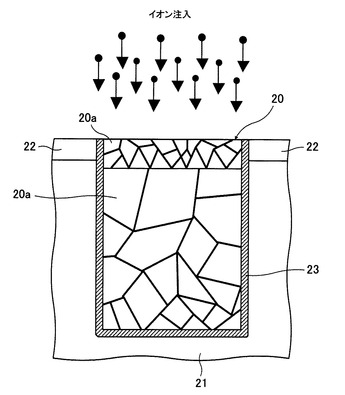

半導体装置の製造方法

【課題】配線のエレクトロマイグレーション耐性を向上させる。

【解決手段】めっき法を用いてCu配線20を形成する際、まず第1の電流密度の条件で第1の平均粒径を有する第1の金属膜を形成し、次いで、第1の電流密度よりも高い第2の電流密度の条件で第1の平均粒径よりも大きい第2の平均粒径を有する第2の金属膜を形成する。その後、第1,第2の金属膜の上部に所定元素を導入し、導入後、第1,第2の金属膜上にキャップ膜を形成する。

【選択図】図5  (もっと読む)

(もっと読む)

半導体装置及び半導体装置の製造方法

【目的】Cu配線上に形成されるCuとSiとを含有する化合物膜の余剰SiがCu配線中へと拡散することを防止した半導体装置を提供することを目的とする。

【構成】本発明の一態様の半導体装置は、SiとOとが他より多く含まれる領域を有するCu配線となるCu膜260,262と、Cu膜260,262上に選択的に形成された、CuとSiとを含有する選択キャップ膜280と、Cu膜260,262の側面側に形成された層間絶縁膜220と、を備えたことを特徴とする。

(もっと読む)

半導体デバイス内でのビアパターニングにおける金属キャップ層の侵食を低減する方法

【解決手段】

半導体デバイスの高性能な金属化システムにおいてビア開口をパターニングする間、開口(221A)が導電性キャップ層(213)を通って延び、適切なイオン衝撃が確立されて下層の金属領域(212)の材質が導電性キャップ層(213)の露出した側壁部分へ再分配され、それにより保護材質(212P)が確立される。その結果、後続のウエット化学的エッチング処理(215)において、導電性キャップ層(213)の過度な材質除去の可能性を大幅に低減することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】Nチャネル領域内、およびPチャネル領域内のチャネルに印加するストレスを制御でき、面積の増加抑制および歩留まりの低下を実現できる半導体装置およびその製造方法を提供する。

【解決手段】Nチャネル領域201内のコンタクトライナー513にSiより大きな元素イオンを注入して構成原子の結合を切断する。Pチャネル領域202内のコンタクトライナー513にSiより大きな元素イオンを注入して構成原子の結合を切断後、酸素などをイオン注入する。その後、熱処理を加えてNチャネル領域201内のコンタクトライナー513を収縮させてnチャネルコンタクトライナー518を形成し、Pチャネル領域202内のコンタクトライナー513を膨張させてpチャネルコンタクトライナー519を形成する。

(もっと読む)

半導体装置の製造方法

【課題】Viaホールと下層配線間の抵抗を下げるため、パンチスルー技術にてViaホール底のバリアメタル膜の除去時に、上層配線底のバリアメタル膜も同時に除去されて絶縁膜が深く掘り下げられることを防ぐ。

【解決手段】低誘電率絶縁膜203の表面を水素(H2)と水蒸気(H2O)の混合ガスにてプラズマ処理して、ヤング率を4.5GPaから70GPa程度の改質膜207を形成することにより、その後、上層に形成されたバリアメタル膜208をパンチスルー技術によって除去する際に、下層の低誘電率絶縁膜203へのダメージを低減する。

(もっと読む)

半導体素子の製造方法

【課題】 本発明は、トンネル酸化膜の形成時に酸化膜に窒素を蓄積させた後、後続で酸素を注入するための工程を行ってSi−N結合をSi−O−N結合に変更することにより、窒素プロファイル(N profile)の変化による特性劣化の防止、電気的ストレスの緩和及び酸素密度の増加などを通じてサイクリング(cycling)及び電荷保存(retention)特性などの素子特性を向上させることができる半導体素子の製造方法を提供するものである。

【解決手段】 半導体基板上に第1の絶縁膜を形成する段階と、前記半導体基板と前記第1の絶縁膜の界面に窒素を蓄積させて第2の絶縁膜を形成する段階と、前記第2の絶縁膜に酸素を注入して第3の絶縁膜に変更させる段階とを含む構成としたことを特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】リソグラフィの解像限界以上で、かつ、寸法制御性に優れた超微細パターンを容易に形成する。

【解決手段】パターニングすべき第1の膜として、例えばアモルファスシリコン膜13を形成し、このアモルファスシリコン膜13上にラインとスペースの比率が略3:1のパターン14、17を形成し、次いで、パターン14、17をマスクとしてアモルファスシリコン膜13を加工し、次いで、パターン14、17を両側から幅が略1/3となるまでスリミングした後、このスリミングされたパターンの反転パターン層として、例えばBSG膜18を形成し、次いで、このBSG膜18をマスクとしてアモルファスシリコン膜13を再加工して、ラインとスペースの比率が略1:1で、かつ、ピッチが元の略半分のパターンを形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート形成溝内に埋め込んで形成される金属系ゲート電極を有するトランジスタ群と抵抗とを有する半導体装置で、抵抗値のばらつきをなくした抵抗形成を可能とする。

【解決手段】半導体基板11に、第1トランジスタ群と、これよりも低い動作電圧の第2トランジスタ群と、抵抗3とを備え、第1トランジスタ群は、半導体基板11上に第1ゲート絶縁膜13を介してシリコン系材料層71で形成された第1ゲート電極15を有し、第2トランジスタ群は、半導体基板11上の第1層間絶縁膜38に形成したゲート形成溝42内に第2ゲート絶縁膜43を介して金属系ゲート材料を埋め込むように形成された第2ゲート電極47、48を有し、抵抗3は、半導体基板11上に絶縁膜61を介してシリコン系材料層71と同一層で形成された抵抗本体部62と、この上部に形成された抵抗保護層63を有することを特徴とする。

(もっと読む)

ドライクリーニング方法、基板処理装置、半導体装置の製造方法及び記憶媒体

【課題】被処理基板中の構造体に熱ストレスが加わり難いドライクリーニング方法を提供すること。

【解決手段】 酸化銅、及び有機汚染物質の少なくともいずれか一方が基板表面に形成、もしくは付着した被処理基板をチャンバ内に設置する工程(ステップ1)と、チャンバ内の雰囲気を有機化合物ガス雰囲気として被処理基板の基板表面にガスクラスターイオンビームを照射し、基板表面に形成、もしくは付着した酸化銅、及び有機汚染物質の少なくともいずれか一方を除去する工程(ステップ2)とを具備する。

(もっと読む)

半導体装置の製造方法

【課題】ビア抵抗の低減を図ることができる半導体装置の製造方法を提供する。

【解決手段】トレンチ5の底面のバリアメタル膜6を残存させつつ、ビア4の底面のバリアメタル膜6を除去する。次に、そのビア底面から露出する下層配線1を改質して、改質層7を形成する。次に、その改質層7を除去して、掘れ込み(凹部)8を形成する。そして、掘れ込み8、ビア4およびトレンチ5内にCu膜9を堆積させて、ビアプラグ10および上層配線11を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

21 - 40 / 57

[ Back to top ]