Fターム[5F033RR07]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化窒化物 (1,052)

Fターム[5F033RR07]の下位に属するFターム

SiON (946)

Fターム[5F033RR07]に分類される特許

81 - 100 / 106

引張応力を有するシリコン酸窒化膜を形成する方法

引張応力を有する緻密化されたシリコン酸窒化膜を形成する方法、及び緻密化されたシリコン酸窒化膜を含む半導体デバイスが開示される。緻密化されたシリコン酸窒化膜は、LPCVDプロセスにて基板上に多孔質SiNC:H膜を堆積すること、及びSiNC:H膜に酸素を混入し、それにより、多孔質SiNC:H膜より高い密度を有する緻密化されたSiONC:H膜を形成するために、多孔質SiNC:H膜を酸素含有ガスに曝すことによって形成されることができる。緻密化されたシリコン酸窒化膜は、半導体デバイスを含んだ基板上に含められ得る。  (もっと読む)

(もっと読む)

半導体装置およびその製造方法

【課題】 金属ゲート電極形成時のゲート絶縁膜や半導体基板へのダメージを低減する。

【解決手段】 金属ゲート電極12,22を形成する際、第1,第2のMOSFET10,20を形成する領域に、一方には所定エッチング条件でエッチングレートの低い第1の金属層31を薄く形成し、他方にはその所定エッチング条件でエッチングレートの高い第2の金属層32を厚く形成して、第1,第2の金属層31,32を同時にエッチングする。それにより、それらのエッチングレート差が厚さの違いで相殺され、第1,第2の金属層31,32のエッチングを同時あるいはほぼ同時に終了させることが可能になる。それにより、ゲート絶縁膜11,21やSi基板2へのエッチングダメージを最小限に抑えることが可能になる。

(もっと読む)

微細構造の製造方法

【課題】微細パターンを歩留まりよくエッチングできる微細構造の製造方法を提供する。

【解決手段】製造方法は、(a)被エッチング膜の上に、下層ハードマスク膜、上層ハードマスク膜を積層したエッチング対象物を準備し、(b)エッチング対象物の上にレジストパターンを形成し、(c)レジストパターンをマスクとして、上層ハードマスク膜をエッチングして上層ハードマスクを形成し、(d)工程(c)の後、レジストパターンを除去し、(e)工程(d)の後、上層ハードマスクをエッチングして細くし、(f)工程(e)の後、細くした上層ハードマスクをマスクとして下層ハードマスク膜をエッチングして下層ハードマスクを形成し、(g)上層ハードマスク、下層ハードマスクをマスクとして、被エッチング膜をエッチングするにあたり、上層ハードマスク膜は下層ハードマスク膜よりもレジストパターンをマスクとしたエッチングが容易な膜を用いる。

(もっと読む)

薄膜トランジスタ及びその作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な薄膜トランジスタ及びその作製技術を提供することを目的とする。また、薄膜トランジスタを構成する配線等のパターンを、所望の形状で制御性よく形成できる技術を提供することも目的とする。

【解決手段】薄膜トランジスタが有する配線や電極パターンは、第1の領域及び第2の領域を有する絶縁表面上に設けられた配線層と、配線層に接する電極層とを有し、前記配線層は前記第2の領域に設けられ、電極層は第1の領域に設けられ、電極層及び配線層に対するぬれ性は、前記第1の領域より前記第2の領域が高い領域に設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】 接続孔での接続信頼性を向上させることができる半導体装置の製造方法を提供する。

【解決手段】本発明に係る半導体装置の製造方法は、第1の絶縁膜10上に配線20を形成する工程と、第1の絶縁膜10上及び配線20上に、第2の絶縁膜30を形成する工程と、第2の絶縁膜30に、配線20上に位置する接続孔30aを形成する工程と、接続孔30aの底に位置する配線20をスパッタリングすることにより、接続孔30aの側面に被覆膜31を形成する工程と、第2の絶縁膜30上及び被覆膜31上にバリア膜41を形成する工程と、接続孔30aに導電膜42を埋め込む工程とを具備する。

(もっと読む)

半導体装置及びその製造方法

【課題】 接合リークを増大させることがなく、低抵抗なコンタクトを半導体基板の全面で安定して形成することができる半導体装置、及びその製造方法を提供する。

【解決手段】 半導体層を有する基板1上に、金属酸化物からなるライナ膜26と絶縁膜22からなる層間絶縁膜20を形成する。次に、絶縁膜22上に、コンタクトホール24の形成位置に開口部を有するマスクパターン23を形成する。そして、マスクパターン23をエッチングマスクとして絶縁膜22をエッチング除去し、ライナ膜26を露出させる。この後、露出したライナ膜26を真空中でエッチング除去し、半導体基板1を露出させ、当該真空中で連続して、露出した半導体基板1上に導電膜を形成することでコンタクト構造を形成する。

(もっと読む)

誘電体メモリ及びその製造方法

【課題】 COB構造を有する誘電体メモリにおいて、スタックコンタクトにおける下部コンタクトプラグのコンタクト抵抗の安定化を図る。

【解決手段】 不純物拡散層104に接続する第1のコンタクトプラグ108の上方に形成された配線109を覆う第2の絶縁膜110を形成する工程と、第2の絶縁膜110上に第3の絶縁膜111を形成する工程と、第3の絶縁膜111上に第1の水素バリア膜112を形成する工程と、第1の水素バリア膜112上にキャパシタ118を形成する工程と、第1の水素バリア膜112における第1のコンタクトプラグ108の上方に存在している部分を選択的に除去した後、キャパシタ108に対して熱処理を行う工程とを備える。これにより、熱処理時に、第1のコンタクトプラグ108の上面が第2の絶縁膜110及び第3の絶縁膜111によって覆われているので、第1のコンタクトプラグ108の酸化及び消失を防止することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】MIM型容量素子において、ヴィアホールのエッチング時に上部電極と下部電極ではコンタクト深さが異なるため、上部電極及び容量誘電膜の突き抜けによるリーク不良が発生する。

【解決手段】基板上に下部電極12a及び上部電極引き出し層12bを同一配線層に形成し、下部電極12a上にのみ容量絶縁膜13を形成し、容量絶縁膜13上から上部電極引き出し層12bを覆う上部電極14を形成し、上部電極14と上部電極引き出し層12bを電気的に接続することにより、MIM型容量素子を形成する。

(もっと読む)

半導体装置の製造方法

【課題】

コンタクト不良の発生を未然に防止することにより歩留まりを向上させた半導体装置の製造方法及び同方法により製造した半導体装置を提供すること。

【解決手段】

同一基板上に第1導電型の電界効果トランジスタと第2導電型の電界効果トランジスタとを形成する工程と、第1導電型の電界効果トランジスタ上に、この第1導電型の電界効果トランジスタのチャネル領域に対して第1の応力を付与する第1の膜と第1の酸化膜とを順次形成する工程と、第1の酸化膜と第2導電型の電界効果トランジスタとの上に、第2導電型の電界効果トランジスタのチャネル領域に対して第2の応力を付与する第2の膜を形成する工程と、第2の膜の表層を変質させて第2の酸化膜を形成する表層変質処理を行う工程と、この表層変質処理を行った第2の膜に所定のパターニングを施す工程とを有する製造方法により半導体装置を製造する。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】より高性能、高信頼性の記憶装置、及びその記憶装置を備えた半導体装置を低コストで、歩留まりよく作製できる技術を提供することも目的とする。

【解決手段】半導体装置に含まれる記憶素子を構成する有機化合物層と、有機化合物層を挟んで形成される一対の導電層において少なくとも一方の導電層との間に複数の絶縁物が存在するように、一対の導電層において少なくとも一方の導電層が複数の絶縁物を含むように形成する。本発明の記憶装置の一は、複数の絶縁物を含む第1の導電層と、複数の絶縁物を含む第1の導電層上に有機化合物層と、有機化合物層上に第2の導電層とを有する。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】信頼性が高く小型なTFTを作製するために、信頼性の高いゲート電極、ソース配線及びドレイン配線を形成するための半導体装置の作製方法及び半導体装置を提供することを課題とする。

【解決手段】絶縁表面を有する基板上に半導体膜を形成し、前記半導体膜上にゲート絶縁膜を形成し、前記ゲート絶縁膜上にゲート電極を形成し、前記ゲート電極に高密度プラズマにより窒化することによって前記ゲート電極の表面に窒化膜を形成する半導体装置の作製方法である。

(もっと読む)

表示装置、及び表示装置の作製方法

【課題】信頼性の高い表示装置を低いコストで歩留まり良く製造することができる技術を提供することを目的とする。

【解決手段】一導電型の不純物領域を含む半導体層と、半導体層上にゲート絶縁層と、ゲート電極層と、一導電型の不純物領域と接する配線層と、ゲート絶縁層上に設けられ、配線層と接する導電層と、導電層と接する第1の電極層と、第1の電極層上に電界発光層と、第2の電極層とを有し、配線層は導電層を介して第1の電極層と電気的に接続している。

(もっと読む)

半導体装置、及び半導体装置の作製方法

【課題】より高性能、高信頼性の記憶装置、及びその記憶装置を備えた半導体装置を低コストで、歩留まりよく作製できる技術を提供することも目的とする。

【解決手段】第1の導電層と、第1の導電層の側端部と接して設けられる第1の絶縁層と、第1の導電層及び第1の絶縁層上に設けられる第2の絶縁層と、第2の絶縁層上に設けられる第2の導電層とを有し、第2の絶縁層は、絶縁性材料によって形成されており、絶縁性材料が流動化したときの流動化物に対するぬれ性は、第1の導電層より第1の絶縁層の方が高い。

(もっと読む)

超低k(ULK)SiCOH膜および方法

【課題】 誘電率が2.7以下であり、弾性計数および硬度の改善等、機械的特性を向上させた超低誘電率(k)膜、および、かかる膜の製造方法を提供すること。

【解決手段】 本発明は、弾性係数および硬度が改善した多相超低k膜、ならびにこれを形成するための様々な方法を提供する。多相超低k誘電膜は、Si、C、O、およびHの原子を含み、誘電率が約2.4以下であり、ナノサイズの孔または空隙を有し、弾性係数が約5以上であり、硬度が約0.7以上である。好適な多相超低k誘電膜は、Si、C、O、およびHの原子を含み、誘電率が約2.2以下であり、ナノサイズの孔または空隙を有し、弾性係数が約3以上であり、硬度が約0.3以上である。  (もっと読む)

(もっと読む)

CMOSFET内の歪みを最適化するための構造体及び方法

【課題】 CMOSFET内の歪みを最適化するための構造体及び方法を提供すること。

【解決手段】 MOSFET内の歪みを最適化し、より具体的には、1つの種類(P又はN)のMOSFET内の歪みを最大にし、かつ、別の種類(N又はP)のMOSFET内の歪みを最小にし緩和する、PMOSFET及びNMOSFETの両方を含む歪みMOSFETの半導体構造体、及び歪みMOSFETを製造する方法が開示される。元の完全な厚さを有する歪み誘起CA窒化物コーティングが、PMOSFET及びNMOSFETの両方の上に形成され、この歪み誘起コーティングは、1つの種類の半導体デバイス内に最適化された十分な歪みをもたらし、別の種類の半導体デバイスの性能を劣化させる。歪み誘起CA窒化物コーティングは、別の種類の半導体デバイスの上で減少した厚さまでエッチングされ、減少した厚さの歪み誘起コーティングは、他方のMOSFET内でより少ない歪みを緩和し、他方のMOSFET内により少ない歪みをもたらす。

(もっと読む)

半導体素子及びその形成方法

【課題】MIMキャパシタを形成した後に金属配線を形成することにより無駄なマスク工程を省略し、キャパシタ形成時のエッチングでの金属配線の損傷を防止できる半導体素子及びその形成方法を提供すること。

【解決手段】層間絶縁膜100を貫通するコンタクトプラグ110を形成するステップと、層間絶縁膜100上にキャパシタを形成するための下部電極用導電層130、誘電層140、上部電極用導電層150を順次形成するステップと、上部電極用導電層150をパターニングして上部電極150を形成するステップと、誘電層140及び下部電極層130をパターニングして下部電極130を形成してキャパシタを形成するステップと、コンタクトプラグ110、キャパシタの上部電極150及び下部電極130に接続される第1金属配線120を形成するステップとを含む。

(もっと読む)

半導体装置及びその製造方法

強誘電体キャパシタ(23)を形成した後、表面の傾斜が緩やかな絶縁膜(24)を、高密度プラズマCVD法又は常圧CVD法等により形成する。その後、アルミナ膜(25)を絶縁膜(24)上に形成する。このような方法によれば、アルミナ膜(25)のカバレッジの低さが問題となることはなく、強誘電体キャパシタ(23)が確実に保護される。  (もっと読む)

(もっと読む)

半導体装置、表示装置、及びそれらの作製方法、並びにテレビジョン装置

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な半導体装置、表示装置及びその作製技術を提供することを目的とする。また、それらの半導体装置、表示装置を構成する配線等のパターンを、所望の形状で密着性よく形成できる技術を提供することも目的とする。

【解決手段】第1の導電層と第2の導電層の間に、導電性の有孔バッファ層を形成することによって、第1の導電層と第2の導電層との密着性を高める。有孔バッファ層が有する孔に、粒子状の導電性材料を侵入させ、焼成によって固化し、第2の導電層を形成する。孔内で固化した導電層がくさびのような働きをし、この働く力によって、第2の導電層は、第1の導電層と密着性よく安定して形成される。

(もっと読む)

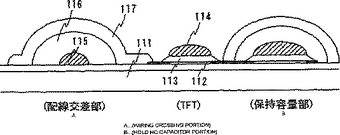

半導体装置およびその作製方法

島状の層間絶縁膜をソース線とゲート線が交差する領域に選択的に形成する。例えば、インクジェット法を用いて絶縁材料を含む液体をゲート線とソース線が交差する領域若しくは保持容量が形成される領域に滴下することにより、フォトリソグラフィー工程を削減し、TFT作製プロセス中において使用するマスク枚数を減らすことが可能となる。  (もっと読む)

(もっと読む)

延伸スペーサを利用した半導体デバイスおよびその形成方法

【課題】延伸スペーサを利用した半導体デバイスおよびその形成方法を提供する。

【解決手段】半導体デバイスは、半導体基板110を覆うゲートと、ゲートの側壁上にある誘電体ライナー150とを含む。この半導体デバイスは、誘電体ライナー150に隣接して誘電体ライナー150を越えるように半導体基板110に沿って横向きに延伸された延伸スペーサ170を含む。半導体デバイスは、半導体基板110の上面の下方に位置し、ゲート下のチャネル領域145に隣接するソース/ドレインをさらに含む。ソース/ドレインは、誘電体ライナー150および延伸スペーサ170下で延伸される。半導体デバイスは、ソース/ドレインの一部上を覆い、半導体基板110に沿って横向きに延伸するシリサイド領域190をさらに含む。従って、延伸スペーサ170はソース/ドレインの一部上において誘電体ライナー150とシリサイド領域190との間に形成される。

(もっと読む)

81 - 100 / 106

[ Back to top ]