Fターム[5F033RR07]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化窒化物 (1,052)

Fターム[5F033RR07]の下位に属するFターム

SiON (946)

Fターム[5F033RR07]に分類される特許

101 - 106 / 106

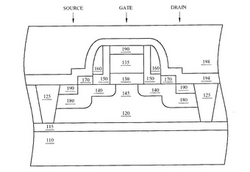

延伸スペーサを利用した半導体デバイスおよびその形成方法

【課題】延伸スペーサを利用した半導体デバイスおよびその形成方法を提供する。

【解決手段】半導体デバイスは、半導体基板110を覆うゲートと、ゲートの側壁上にある誘電体ライナー150とを含む。この半導体デバイスは、誘電体ライナー150に隣接して誘電体ライナー150を越えるように半導体基板110に沿って横向きに延伸された延伸スペーサ170を含む。半導体デバイスは、半導体基板110の上面の下方に位置し、ゲート下のチャネル領域145に隣接するソース/ドレインをさらに含む。ソース/ドレインは、誘電体ライナー150および延伸スペーサ170下で延伸される。半導体デバイスは、ソース/ドレインの一部上を覆い、半導体基板110に沿って横向きに延伸するシリサイド領域190をさらに含む。従って、延伸スペーサ170はソース/ドレインの一部上において誘電体ライナー150とシリサイド領域190との間に形成される。

(もっと読む)

半導体装置の製造方法

【課題】測定対象の収縮等が生じやすい条件下でも高い精度で測長を行うことができる半導体装置の製造方法を提供する。

【解決手段】Si基板上にレジスト膜を形成した後、レジスト膜に半導体集積回路用の回路パターン、第1のL字型測長用パターン3a,3b及び十字型のアライメント用モニタパターン4a,4bを形成し、これらのパターンに基づいて、Si基板をパターニングする。その後、Si基板の上方に、ポリSi膜を形成し、ポリSi膜上にレジスト膜を形成する。レジスト膜に半導体集積回路用の回路パターン、第2のL字型測長用パターン13a,13b及び十字型のアライメント用モニタパターン15bを形成する。このとき、第2のL字型測長用パターンが平面視で第1のL字型測長用パターンを180度回転させた方向を向くようにする。そして、これらのパターンをマスクとして、ポリSi膜をパターニングすることにより、ゲート電極を形成する。

(もっと読む)

表示装置の作製方法

【課題】本発明は、しきい値のずれが生じにくく、高速動作が可能な逆スタガ型TFTを有する表示装置の作製方法を提供する。また、スイッチング特性が高く、コントラストがすぐれた表示が可能な表示装置の作製方法を提供する。更には、少ない原料でコスト削減が可能であり、且つ歩留まりが高い表示装置の作製方法を提供する。

【解決手段】 本発明は、耐熱性の高い材料でゲート電極を形成した後、非晶質半導体膜の結晶化を促進する触媒元素を有する層、非晶質半導体膜、及びドナー型元素又は希ガス元素を有する層を形成し加熱して、非晶質半導体膜を結晶化すると共に触媒元素を結晶性半導体膜から除いた後、該結晶性半導体膜の一部を用いて半導体領域を形成し、該半導体領域に電気的に接するソース電極及びドレイン電極を形成し、ゲート電極に接続するゲート配線を形成して、逆スタガ型TFTを形成する。

(もっと読む)

回路基板、電気光学装置、及び電子機器

【課題】 トランジスタ等の能動素子が安定に動作し、大画面化と長期にわたって安定した表示動作とを可能にする。

【解決手段】 陰極(222)と陽極(23)とに狭持され、基板(2)の上方に配置された電気光学素子と、電気光学素子を駆動する能動素子(24)と、陰極(222)及び陽極(23)のうち少なくとも一方と基板(2)との間に配置された誘電率が所定の値以下の絶縁材料からなる絶縁膜(283、284)とから電気光学装置(1)を構成する。

(もっと読む)

多孔質膜の堆積方法

【課題】基板上に多孔質膜を堆積させる処理方法を提供する。

【解決手段】多孔質シリカ膜及びドープシリカ膜を堆積させる処理方法。本方法は、循環方式を用い、各サイクルは、最初にシリカをシリコンと共に共堆積させる段階と、次に選択的にシリコンを除去して多孔質構造体を形成する段階とを含む。好ましい実施形態では、共堆積は、プラズマ強化化学気相蒸着によって行われる。反応剤給送流れは、共堆積反応剤と選択的シリコン除去反応剤との混合物を含む。RF電力変調を使用して、共堆積段階及び選択的シリコン除去段階を制御し、後者は、RF電力が切られるか又は低レベルに低減される度に進行する。本発明を用いて、高度に均一な小さな孔隙及び望ましい空隙率プロフィールを有する多孔質膜を取得することができる。本方法は、半導体集積回路製造のための広範囲の低−k誘電体を形成するのに有利である。本方法はまた、他の用途のための他の多孔質膜を形成するのにも有利である。

(もっと読む)

フリップチップ用高性能シリコンコンタクト

本発明においては、前面(14)と背面(16)とを備える半導体基板(12)であって、基板を(12)通って前面(14)と背面(16)との間を延びる孔(18、20、22)を備える半導体基板(12)を用意する。孔(18、20、22)は、部分的に、内壁部分によって規定され、外側導電性シースを形成する。導電性材料(54)を、内壁部分の少なくとも一部に隣接して形成する。その後に誘電体材料層(56)を、孔内部に、導電性材料上であってそのラジアル方向内側に形成する。次に第2の導電性材料(60)を、孔内部に、誘電体材料層(56)上であってそのラジアル方向内側に形成する。後者の導電性材料は、内側導電性コアキシャル線要素を構成する。 (もっと読む)

101 - 106 / 106

[ Back to top ]