Fターム[5F033RR07]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 酸化窒化物 (1,052)

Fターム[5F033RR07]の下位に属するFターム

SiON (946)

Fターム[5F033RR07]に分類される特許

61 - 80 / 106

半導体装置及びその製造方法

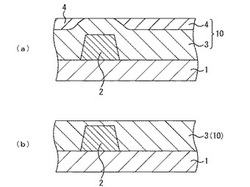

【課題】キャパシタ構造への水分・水素の浸入を可及的に防止するも、面内膜厚分布が極めて低く極めて優れた表面平坦性を有する層間絶縁膜を形成し、誘電体特性への影響やコンタクト抵抗のバラツキ等を抑えた信頼性の高い半導体装置及びその製造方法を提供する。

【解決手段】極低水分含有量のシリコン酸化膜である第1の絶縁膜3と、第1の絶縁膜3よりも水分含有量の多い、従って面内膜厚分布率の小さいシリコン酸化膜である第2の絶縁膜4との積層膜を形成し、これをCMPにより研磨する。強誘電体キャパシタ構造2の直上には第2の絶縁膜4が残らず除去され、第1の絶縁膜3の表面がある程度露出するまで研磨する。このとき、第1の絶縁膜3における第1の部分の上面から第2の絶縁膜4の上面にかけて表面平坦化されてなり、第1の絶縁膜3と、第1の絶縁膜3の第2の部分上に残る第2の絶縁膜4とからなる層間絶縁膜10が形成される。

(もっと読む)

表示装置の作製方法、及びエッチング装置

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。

【解決手段】チューブを絶縁層の開口形成領域上に絶縁層に接して配置し、そのチューブを通して処理剤(エッチングガス又はエッチング液)を絶縁層に吐出する。吐出(された処理剤(エッチングガス又はエッチング液)によって、絶縁層を選択的に除去し、絶縁層に開口を形成する。従って、導電層上に開口を有する絶縁層が形成され、絶縁層下の導電層が開口の底面に露出する。露出された導電層と接するように開口に導電膜を形成し、導電層と導電膜を絶縁層に設けられた開口において電気的に接続する。

(もっと読む)

半導体集積回路及びその製造方法

【課題】パワー・トランジスタに流れる電流ルートを明確にすると共に、パワー・トランジスタに流れる電流の最適化を図ることにより、パワー・トランジスタへのダメージ又はストレスを低減し、信頼性に優れた半導体集積回路を提供する。

【解決手段】半導体集積回路は、半導体基板上(100)に形成されたパワー・トランジスタ(100A)と、パワー・トランジスタ(100A)の直上に形成され、パワー・トランジスタの第1の電極及び第2の電極として機能する複数の第1の金属パターン及び複数の第2の金属パターンと、複数の第1の金属パターンのうち対応する第1の金属パターンと電気的に接続する複数の第1のバス(140〜142)と、複数の第2の金属パターンのうち対応する第2の金属パターンと電気的に接続する複数の第2のバス(150〜152)と、複数の第1のバス(140〜142)及び複数の第2のバス(150〜152)の各々には、1つのコンタクト・パッド(304)が設けられている。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。

【解決手段】導電層上にマスクを設け、マスクを設けた導電層上に絶縁膜を成膜し、マスクを除去することで開口を有する絶縁層を形成する。露出した導電層と接するように開口に導電膜を形成することによって、導電層及び導電膜は絶縁層を介して電気的に接続することができる。開口の形状はマスク形状を反映し、柱状(角柱、円柱、三角柱など)、針状などを用いることができる。

(もっと読む)

垂直型ウェハ間相互接続を設けるための金属充填貫通ビア構造体

【課題】 垂直型ウェハ間相互接続を設けるための金属充填貫通ビア構造体を提供する。

【解決手段】 垂直型ウェハ間相互接続構造体を設けるのに有用な貫通ビア接続を作成する方法、並びに、この方法によって形成される垂直型相互接続構造体が提供される。本発明の方法は、垂直型接続のために金属スタッドのみを使用し、それゆえに、金属スタッドによってアルファ線は発生されない。本発明の方法は挿入ステップ、加熱ステップ、薄層化ステップ及び裏面加工を含む。

(もっと読む)

表示装置の作製方法

【課題】材料の利用効率を向上させ、かつ、作製工程を簡略化して作製可能な表示装置及びその作製技術を提供することを目的とする。

【解決手段】光吸収層を形成し、光吸収層上に絶縁層を形成し、光吸収層及び絶縁層に選択的にレーザ光を照射し、絶縁層の照射領域を除去し絶縁層に開口を形成し、開口に光吸収層と接するように導電膜を形成する。露出した光吸収層と接するように開口に導電膜を形成することによって、光吸収層及び導電膜は絶縁層を介して電気的に接続することができる。

(もっと読む)

デバイス、方法(MIMキャパシタおよびその製造方法)

【課題】MIMキャパシタ・デバイスおよびMIMキャパシタ・デバイスの製造方法を提供すること。

【解決手段】このデバイスは、1つまたは複数の導電層を含み、上面、下面および側壁を有する上プレートと、1つまたは複数の導電層を含み、上面、下面および側壁を有するスプレッダ・プレートと、1つまたは複数の誘電層を含み、上面、下面および側壁を有する誘電ブロックとを含み、誘電ブロックの上面は上プレートの下面と物理的に接触し、誘電ブロックの下面はスプレッダ・プレートの上面の上にあり、上プレートと誘電ブロックの側壁は本質的に共面である。

(もっと読む)

自己整合されたデュアル応力層を用いるCMOS構造体及び方法

【課題】 デバイス性能を向上させ、チップの留まりを改善するために、CMOS構造体内に機械的応力を与える構造体及び方法を提供すること。

【解決手段】 第1のトランジスタの上に配置された第1の応力層及び第2のトランジスタの上に配置された第2の応力層が、当接するが、重ならない、CMOS構造体及びCMOS構造体を製造する方法が提供される。こうした重ならない当接により、第1のトランジスタ及び第2のトランジスタの一方の中のソース/ドレイン領域の上に、シリサイド層へのコンタクトを形成するとき、製造の柔軟性が向上する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、ゲート絶縁膜の膜厚が増加することを抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板10上に絶縁膜20を形成するステップと、絶縁膜上に第1の金属膜30を形成するステップと、第1の金属膜の上方に、酸素分子1モルあたりの金属酸化物を生成する際の生成エネルギーが負であって、かつ生成エネルギーの絶対値が第1の金属膜より大きい第2の金属膜50を形成するステップと、第1及び第2の金属膜にパターニングを行うステップと、所定の熱処理を行うステップとを備える。

(もっと読む)

ミドル・オブ・ザ・ライン(MOL)用途のための無電解コバルト含有ライナ

【課題】 従来技術のMOLメタラジを用いてその欠点を回避する新しいMOLメタラジとその製造方法を提供すること。

【解決手段】 酸素ゲッター層と金属含有導電性材料との間に配置されたCo含有ライナを含む半導体構造が提供される。Co含有ライナ、酸素ゲッター層及び金属含有導電性材料は、Co含有ライナが従来のTiNライナと取って代わるMOLメタラジを形成する。「Co含有」とは、ライナが、元素状Coのみを含むか、又は元素状CoとP又はBの少なくとも1つを含むことを意味する。高アスペクト比のコンタクト開口部内により良好な段差被覆性の本発明のCo含有ライナを提供するために、Co含有ライナが、無電解蒸着プロセスによって形成される。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】チップ面積及び製造コストの増大を抑制しつつ、レーザ照射用の冗長回路を備えた半導体装置及びその製造方法を提供する。

【解決手段】基板上に第1の能動層として、本来の機能を有する回路を形成する工程と、前記第1の能動層に絶縁層を形成する工程と、前記絶縁層上に、微細孔を形成する工程と、前記微細孔が形成された絶縁層上に半導体層を形成する工程と、前記半導体層に対してレーザ照射による熱処理を行うことで、前記微細孔を起点として略単結晶化された結晶粒を形成する工程と、前記略単結晶化された結晶粒を用いて第2の能動層としてのレーザリペア用の冗長回路を形成する工程とを有する。

(もっと読む)

高アスペクト比用途の異方性フィーチャを形成するためのエッチング方法

【課題】本発明は、エッチング工程における、高アスペクト比用途の異方性フィーチャの形成方法を提供する。

【解決手段】開示された方法は、側壁パッシベーション管理技法を通して、高アスペクト比のフィーチャのプロファイルと寸法の制御を有利に促進する。一実施形態において、側壁パッシベーションは酸化パッシベーション層をエッチング層の側壁及び/又は底部に選択的に形成することによって管理される。他の実施形態において、側壁のパッシベーションは余分な再堆積層を定期的に除去して平坦で均一なパッシベーション層をその上に維持することによって管理される。平坦で均一なパッシベーション層により、欠陥及び/又は下層のオーバーエッチングを起こすことなく、高アスペクト比のフィーチャを、基板上の高及び低フィーチャ密度領域の双方に所望の深さ及び垂直プロファイルの限界寸法に適した形で徐々にエッチングすることが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】 二重露光を用いて微細化を図れる半導体装置の製造方法を提供すること。

【解決手段】 第1のパターンを含むメモリセル領域と、第2のパターンを含む周辺回路領域を備えた半導体装置を製造する際に、メモリセル領域と周辺回路領域を含む基板の領域上にレジスト膜を形成し、メモリセル領域上のレジスト膜中に第1のパターンに対応した潜像を形成するための第1の露光と、周辺回路領域上のレジスト膜中に第2のパターンに対応した潜像を形成するための第2の露光を含む多重露光により、レジスト膜を露光する際に、レジスト膜上における第1の露光と第2の露光の境界領域12を、ガードリング5,7間の素子分離領域10’上に設定し、レジスト膜を現像してレジストパターンを形成し、レジストパターンをマスクにして被加工基板をエッチングする。

(もっと読む)

制御された二軸応力を有する超低誘電率膜および該作製方法

【課題】制御された二軸応力を有する超低誘電率層と、該低誘電率層を形成するための方法を提供する。

【解決手段】PECVDとスピン・コーティングとの一方によってSi、C、OおよびHを含む層を形成する工程と、それぞれ10ppm未満の非常に低い濃度の酸素および水を含む環境中で膜を硬化する工程とを組み込んだ、制御された二軸応力を有する超低誘電率層を形成するための方法を含む。この方法を用いて形成された2.8以下の誘電率を有する材料も含む。本発明は、46MPa未満の低い二軸応力を有する膜を形成するための問題を克服する。

(もっと読む)

半導体装置及びその製造方法

【課題】FUSI化されたゲート電極を有する半導体装置においても、ストレッサ膜を有効に形成できるようにして、半導体装置の電気的特性を向上できるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成され、ニッケルによりフルシリサイド化されたフルシリサイドゲート電極24Aを有するn型MISトランジスタ100Aと、ニッケルによりフルシリサイド化されたフルシリサイドゲート電極24Bを有するp型MISトランジスタ100Bとを有している。半導体基板1上には、該半導体基板1におけるフルシリサイドゲート電極24Aの下側部分のチャネル領域に応力歪みを生じさせるストレッサ膜である第2の下地絶縁膜17が、少なくともフルシリサイドゲート電極24Aを覆うように形成されている。

(もっと読む)

半導体装置およびその作製方法

【課題】工程数を増やすことなく、段切れ不良、及びコンタクト不良を防ぐ方法を提供し、それにより動作性能および信頼性の高い集積回路を作製することを課題とする。

【解決手段】配線の乗り越え部分において、回折格子パターン或いは半透膜からなる光強度低減機能を有する補助パターンを設置したフォトマスクまたはレチクルを配線形成用のフォトリソグラフィ工程に適用し、2層構造の下層配線となる導電層を形成し、下層配線が下層配線1層目と、1層目の幅より短い2層目の幅を有するようにレジストパターンを形成し、急峻な段差を緩和することを目的とした下層配線を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】FUSIゲート電極に達するコンタクト部と、ソース・ドレイン層に達するコンタクト部とで深さが異なることに起因する不具合を解消した半導体装置およびその製造方法を提供する。

【解決手段】層間絶縁膜4を厚さ方向に貫通して2つのソース・ドレイン層34上層部のシリサイド層35およびFUSIゲート電極32にそれぞれ達する2つのFUSIコンタクト部41が設けられている。FUSIコンタクト部41は、層間絶縁膜4を貫通するコンタクト開口部CH1内に、完全にシリサイド化されたFUSIコンタクト層411を充填して構成されており、FUSIゲート電極32と同じ高さを有している。

(もっと読む)

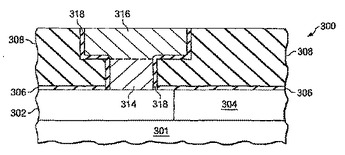

細孔シーリングライナーのデュアルダマシン方法及びデバイスへの統合

デバイスは、細孔シーリングライナーを有するダマシン層を使用し、半導体ボディを含んでいる。金属相互接続(302)からなる金属相互接続層が、半導体ボディ上に形成される。誘電層(308)が、金属相互接続層上に形成される。導電性トレンチフィーチャ(316)及び導電性バイアフィーチャ(314)が、誘電層内に形成される。細孔シーリングライナー(318)が、導電性バイアフィーチャの側壁に沿ってのみ、及び導電性トレンチフィーチャの側壁及び底面に沿って形成される。細孔シーリングライナーは、導電性バイアフィーチャの底面に沿っては実質的に存在しない。  (もっと読む)

(もっと読む)

自己整合銅キャッピング層の形成方法

銅相互接続線(14)上にキャッピング層を形成する方法。その方法は、相互接続線(14)およびそれが埋め込まれた誘電体層を覆うアルミニウム層(20)を供給する工程からなる。これは、堆積および化学的暴露によって達成され得る。ついで構造は、アニーリング、あるいは、例えば窒素原子を含む雰囲気下での、さらなる化学的暴露のような処理に供され、Alの銅線(14)への内部拡散および金属間化合物CuAlNの拡散バリヤを形成する窒化を生じさせる。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】高精度なパターン形成を行なうことが可能となる半導体装置の製造方法を提供する。

【解決手段】基板1の主表面上に絶縁膜7を形成する。絶縁膜7上に導電膜8を形成し、該導電膜8上に下層レジスト膜9、中間層10、反射防止膜11および上層レジスト膜を形成する。この上層レジスト膜の高さを検出することで露光時の焦点位置を検出する。露光時の焦点位置を検出するに際し、焦点検出光を上層レジスト膜に照射する。焦点位置を検出した後、上層レジスト膜を露光、現像し、レジストパターン12aを形成する。レジストパターン12aをマスクとして中間層10と反射防止膜11をパターニングし、下層レジスト膜9を現像する。これらのパターンをマスクとして導電膜8をエッチングし、ゲート電極を形成する。

(もっと読む)

61 - 80 / 106

[ Back to top ]