Fターム[5F033RR11]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | ハロゲンを含むもの(SiOFを含む) (665)

Fターム[5F033RR11]に分類される特許

201 - 220 / 665

半導体装置およびその製造方法

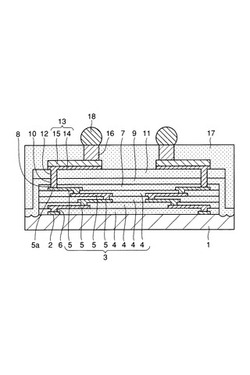

【課題】 シリコン基板および該シリコン基板上に設けられた低誘電率膜と配線との積層構造からなる低誘電率膜配線積層構造部を備えた半導体装置において、低誘電率膜が剥離しにくいようにする。

【解決手段】 シリコン基板1の上面の周辺部を除く領域には低誘電率膜4と配線5との積層構造からなる低誘電率膜配線積層構造部3が設けられている。低誘電率膜配線積層構造部3の上面には第1のパッシベーション膜7が設けられている。そして、第1のパッシベーション膜7および低誘電率膜配線積層構造部3の側面は第2のパッシベーション膜9によって覆われている。これにより、低誘電率膜4が剥離しにくい構造となっている。

(もっと読む)

半導体装置の製造方法、半導体装置、電子機器、半導体製造装置及び記憶媒体

【課題】基板上の凹部が形成された層間絶縁膜の露出面にバリア膜を成膜し、凹部内に下層側の金属配線と電気的に接続される銅配線を形成するにあたり、段差被覆性の良好なバリア膜を形成することができ、しかも配線抵抗の上昇を抑えた半導体装置の製造方法を提供する。

【解決手段】層間絶縁膜に形成された凹部21の底面に露出した下層側の銅配線13の表面の酸化膜を還元あるいはエッチングして、当該銅配線13の表面の酸素を除去した後、マンガンを含み、酸素を含まない有機金属化合物を供給することによって、凹部21の側壁及び層間絶縁膜の表面などの酸素を含む部位に自己形成バリア膜である酸化マンガン25を選択的に生成させる一方、銅配線13の表面にはこの酸化マンガン25を生成させないようにして、その後この凹部に銅を埋め込む。

(もっと読む)

半導体チップ及び半導体装置

【課題】半導体基板の裏面側から効率よく放熱する半導体チップを実現できるようにする。

【解決手段】半導体チップ10は、基板11と、基板11の素子形成面側に形成され、複数の半導体素子を含む集積回路12と、基板11における複数の半導体素子のうちの所定の半導体素子30と対応する領域に形成さた放熱プラグ31とを備えている。放熱プラグ31は、素子形成面と反対側の面に開口する非貫通孔に埋め込まれた基板11と比べて熱伝導率が大きい材料からなる。

(もっと読む)

半導体装置

【課題】層間絶縁膜としてLow−k膜を有する半導体装置において、温度サイクル試験時における層間絶縁膜の剥離を防止し、信頼性に優れた半導体装置を提供する。

【解決手段】銅を主導電層とする埋め込み配線5、8、11を内部に形成した層間絶縁膜4、7、10と、埋め込み配線5、8、11のキャップ絶縁膜6、9、12を積層した構造を備えた半導体装置において、相対的にヤング率の小さいLow−k膜からなる層間絶縁膜7と上面で接する相対的にヤング率の大きいキャップ絶縁膜6は、半導体装置の端部において、非設置となるように形成する。

(もっと読む)

半導体装置の製造方法

【課題】 金属配線を埋設する層間絶縁膜の厚さを精度良く制御可能な半導体装置の製造方法を提供する。

【解決手段】 素子が形成された半導体基板1上に、金属配線膜を堆積する工程と、金属配線膜を所定の配線パターンに加工して金属配線10を形成する工程と、金属配線10の上面と金属配線10の周囲の下地層6の上面の高低差で規定される段差値を測定する工程と、金属配線10と下地層6を被覆する絶縁膜11を、段差値の測定値と目標値の差分に基づいて設定された膜厚で堆積する工程と、絶縁膜11を化学的機械研磨により平坦化する工程を有し、絶縁膜11を堆積する工程において、段差値の測定値が目標値より大きい場合には、絶縁膜11の膜厚を段差値の測定値が目標値である場合の絶縁膜11の基準膜厚より厚く設定し、段差値の測定値が目標値より小さい場合には、絶縁膜11の膜厚を基準膜厚より薄く設定する。

(もっと読む)

半導体装置とその製造方法

【課題】高温かつ長時間の熱工程を経ても、酸化されないコンタクトプラグを備えた半導体装置とその製造方法を提供する。

【解決手段】半導体基板上にトランジスタを形成し、前記トランジスタ及び前記半導体基板を覆う層間絶縁膜を形成し、前記層間絶縁膜にこれを貫通する、1つ以上のコンタクトホールを開口し、前記コンタクトホールの側面に、酸化性ガスが拡散するのを防ぐ、絶縁性の酸化性ガス拡散防止膜を成膜し、前記酸化性ガス拡散防止膜の内側に、前記トランジスタの端子とコンタクトするコンタクトプラグ本体を埋め込んで、前記層間絶縁膜から発生する酸化性ガスが前記酸化性ガス拡散防止膜によって前記コンタクトプラグ本体に拡散するのを防止可能な構成を作り、この後、前記層間絶縁膜の上方に、前記コンタクトプラグ本体の1つと電気的に導通する、強誘電体膜を含む強誘電体キャパシタを形成する。

(もっと読む)

半導体デバイスの製造方法

【課題】本発明は、下層配線層を損傷させず、その上部にデュアルダマシン構造の配線要素を形成する半導体デバイスの製造方法を提供することを目的とする。

【解決手段】下層配線上に絶縁物で構成され該下層配線の金属材料の拡散を防止する拡散防止膜を形成し、該拡散防止膜の上部に第1絶縁膜を形成し、該第1絶縁膜の上部にエッチングストッパ膜を形成し、該エッチングストッパ膜の上部に第2絶縁膜を形成し、該下層配線の上部に、該第2絶縁膜、該エッチングストッパ膜、および、該第1絶縁膜を貫通して該拡散防止膜を露出するビアホールを形成し、該ビアホールの内部に、そのビアホールの内壁を覆う有機層を形成し、該第2絶縁膜の所定部位をエッチングにより除去して配線溝を形成し、該配線溝底に露出した該エッチングストッパ膜および該ビアホール底に露出した該拡散防止膜を同時に除去する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、異なる種類の複数のヒューズを積層した構成や、当該構成に対する具体的な救済及び半導体装置の識別付与の製造方法を提供することを目的とする。

【解決手段】

本発明の1つの実施形態では、所定の電圧値を印加、又は所定の電流値以上を流すことで切断される第1ヒューズと、レーザ光を照射することで切断される第2ヒューズと、レーザ光を反射するリフレクタ層とを備える半導体装置である、さらに、本発明の1つの実施形態に係る半導体装置では、第1ヒューズ上に絶縁層を介してリフレクタ層を積層し、リフレクタ層上に絶縁層を介して第2ヒューズを積層する。

(もっと読む)

半導体装置及びその製造方法

【課題】Nチャネル領域内、およびPチャネル領域内のチャネルに印加するストレスを制御でき、面積の増加抑制および歩留まりの低下を実現できる半導体装置およびその製造方法を提供する。

【解決手段】Nチャネル領域201内のコンタクトライナー513にSiより大きな元素イオンを注入して構成原子の結合を切断する。Pチャネル領域202内のコンタクトライナー513にSiより大きな元素イオンを注入して構成原子の結合を切断後、酸素などをイオン注入する。その後、熱処理を加えてNチャネル領域201内のコンタクトライナー513を収縮させてnチャネルコンタクトライナー518を形成し、Pチャネル領域202内のコンタクトライナー513を膨張させてpチャネルコンタクトライナー519を形成する。

(もっと読む)

半導体装置

【課題】製造過程において、バリア膜が絶縁層から剥離するのを防止することができる半導体装置を提供すること。

【解決手段】誘電率が2.8であるSiOCからなる低誘電率層4上には、誘電率が3.2であるSiOCからなる高誘電率層5が形成されている。高誘電率層5は、所定の膜厚Tに形成されている。高誘電率層5上には、SiO2からなる保護層6が形成されている。すなわち、低誘電率層4と保護層6との間には、高誘電率層5が介在されている。低誘電率層4、高誘電率層5および保護層6には、保護層6の上面から低誘電率層4まで掘り下がった配線溝7が形成されている。配線溝7の底面および側面には、Taからなるバリア膜8が形成されている。バリア膜8上には、Cuからなり、配線溝7を埋め尽くすCu配線9が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】歩留りが高く且つ配線間容量を十分に低減でき、且つ機械的強度を十分に得られるようにする。

【解決手段】半導体装置は、半導体基板の上に形成された第1の層間絶縁膜101と、第1の層間絶縁膜101に形成された複数の配線105と、第1の層間絶縁膜101に複数の配線105の少なくとも1つと接続するように形成されたビア113及びダミービア106とを有している。第1の層間絶縁膜101における互いに隣り合う配線105同士の間には空隙部109が選択的に形成されており、ダミービア106は、空隙部109と接する配線105Aの下側に該配線105Aと接続して形成され、ビア113及びダミービア106は、空隙部109を介することなく第1の層間絶縁膜101により周囲を覆われている。

(もっと読む)

半導体装置およびその製造方法

【課題】エアギャップにより配線間の寄生容量を低減しつつ、安定したエアギャップを形成できる半導体装置を提供する。

【解決手段】基板1と、この基板1上に形成された第1の絶縁膜2と、この第1の絶縁膜2上に形成された複数の金属配線3と、この金属配線3および上記第1の絶縁膜2を覆う第2の絶縁膜4と、この第2の絶縁膜4上に形成された第3の絶縁膜5とを有する。一対の隣り合う金属配線3の間に、溝部7内に、エアギャップ6が設けられている。金属配線3の間隔LWが所定の間隔LWに対する変動量に応じ、上記第2の絶縁膜4の膜厚は調整されている。

(もっと読む)

半導体装置

【課題】高い耐電圧特性、および耐リーク特性を有する配線構造を備える半導体装置、およびその製造方法を提供する。

【解決手段】本発明の実施の形態による半導体装置は、半導体素子が設けられた半導体基板と、前記半導体基板上に形成された、上下層の導電部材を電気的に接続する接続部材と、前記接続部材と同じ層に形成された第1の絶縁膜と、前記接続部材の上面の一部と接する第1の領域、および前記第1の領域上に位置し、前記第1の領域よりも幅の広い第2の領域を含む配線と、前記第1の絶縁膜上に、前記配線の前記第1の領域の側面の上側から少なくとも一部、および前記第2の領域の底面に接して形成された第2の絶縁膜と、を有する。

(もっと読む)

半導体装置の製造方法

【課題】

太幅配線と細幅配線を含む配線層の形成において新たに生じる問題を解決できる半導体装置の製造方法を提供する。

【解決手段】

半導体装置の製造方法は、半導体素子を形成した半導体基板上に下層絶縁膜を形成し、下層絶縁膜に太幅配線溝、細幅配線溝を含む配線溝を形成し、太幅配線溝に導電体層、塗布型無機絶縁膜を埋め込み、細幅配線溝に導電体層を埋め込み、塗布型無機絶縁膜を覆って、上層絶縁膜を形成し、上層絶縁膜にビア孔をドライエッチングし、太幅配線溝で塗布型無機絶縁膜を露出し、ビア孔底の塗布型無機絶縁膜をウェットエッチングして除去する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の外部端子に加わる外力により外部端子の下方の絶縁膜にクラックが生じるのを抑制または防止する。

【解決手段】半導体基板1の主面上には複数の配線層が形成されている。この複数の配線層のうちの最上の配線層MHの直下の第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成しない。上記第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下以外の領域には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成する。

(もっと読む)

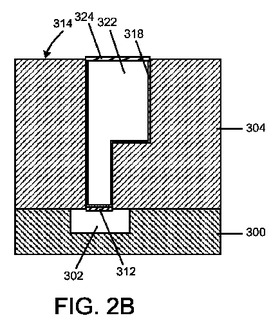

半導体デバイスのCuメタライゼーションへ選択的低温Ru堆積を統合する方法

半導体デバイスの製造に選択的低温Ru堆積を統合することで、バルクCu金属中でのエレクトロマイグレーション及びストレスマイグレーションを改善する方法。当該方法は、誘電体層(304)中に凹部を有するパターニング基板を供する工程であって、前記凹部は平坦化されたバルクCu金属(322)によって少なくとも実質的に充填されている工程、H2、N2、若しくはNH3、又はこれらの混合気体が存在する中で前記バルクCu金属及び前記誘電体膜を熱処理する工程、並びに、前記の熱処理されたバルクCu金属上にRu金属膜を選択的に堆積する工程、を有する。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】銅−マンガン合金技術を用いて銅コンタクトを形成する場合において、コンタクトホールの底部にもバリア層としてのマンガン酸化物層を形成させる。

【解決手段】半導体装置100は、半導体基板101上に形成された金属含有化合物層102と、金属含有化合物層102上を含む半導体基板101上に形成された絶縁体膜103と、絶縁体膜103に、金属含有化合物層102に達するように形成されたコンタクトホール104と、コンタクトホール104に形成されたコンタクトプラグと、絶縁体膜103及び金属含有化合物層102のそれぞれとコンタクトプラグとの間に形成されたマンガン酸化物層119とを備える。

(もっと読む)

半導体装置及びその製造方法

【課題】貫通電極と有し、信頼性の高い半導体装置を提供する。

【解決手段】半導体基体11上に絶縁層22が形成され、半導体基体11及び絶縁層22を貫通するビアホール14が形成され、ビアホール14の内側面に、絶縁層16,17を介して導電層19が形成された貫通電極26が構成され、ビアホール14の内側面に形成される絶縁層16,17の表面が、半導体基体11と半導体基体11上に形成される絶縁層22との界面の凹部15を埋め込んでほぼ平坦化する形状である半導体装置を構成する。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】本発明は、コンタクトプラグの高抵抗化を抑制することができ、また当該コンタクトプラグの構成材料のソース・ドレイン領域への拡散が起こらず、かつ簡略な製造プロセスにより作製可能な半導体装置を提供する。

【解決手段】本発明に係る半導体装置は、ゲート電極4、第一の層間絶縁膜7、第一のコンタクトプラグ8、第二の層間絶縁膜9および第二のコンタクトプラグ10を有する。第一の層間絶縁膜7の上面は、ゲート電極4の上面と同じ高さ位置である。第一のコンタクトプラグ8は、第一の層間絶縁膜7の膜厚方向に貫通して形成され、下面においてソース・ドレイン領域5と電気的に接続され、第一の電気抵抗率を有する。第二のコンタクトプラグ10は、第二の層間絶縁膜9の膜厚方向に貫通して形成され、下面において第一のコンタクトプラグ8の上面と電気的に接続され、第一の電気抵抗率より低い第二の電気抵抗率を有する。

(もっと読む)

デュアルダマシンプロセスおよびインプリントリソグラフィを用いた3次元メモリアレイ内のメモリ線およびビアの形成方法および装置

本発明は、多重深さインプリントリソグラフィマスクおよびダマシンプロセスを用いて3次元メモリアレイを形成するシステム、装置および方法を提供する。3次元メモリ内のメモリ層製造用のインプリントリソグラフィマスクが説明される。マスクは、ダマシンプロセスで用いられる転写材料内のインプリントを作製するためのフィーチャが形成される半透明材料を含む。マスクは複数のインプリント深さを有し、少なくとも1つのインプリント深さはメモリ線形成用の溝に対応し、少なくとも1つの深さはビア形成用の孔に対応する。この他にも数々の態様が開示される。  (もっと読む)

(もっと読む)

201 - 220 / 665

[ Back to top ]