Fターム[5F033RR11]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | ハロゲンを含むもの(SiOFを含む) (665)

Fターム[5F033RR11]に分類される特許

161 - 180 / 665

半導体装置の製造方法及び成膜システム

【課題】フッ素添加カーボン膜(CF膜)上にハードマスク用の薄膜であるSiCO膜あるいはSiCN膜を成膜するにあたり、その薄膜とフッ素添加カーボン膜との間で大きな密着性を得ること。

【解決手段】 SiCO膜をハードマスクとして使用する場合に、CF膜をシリコンの有機化合物例えばトリメチルシランガスを活性化したプラズマ雰囲気に例えば5〜10秒程度曝し、次いでこのプラズマに窒素プラズマを加えてフッ素添加カーボン膜の上にSiCN膜を成膜し、その後例えばトリメチルシランガスと酸素ガスとを活性化したプラズマによりSiCO膜を成膜する。SiCO膜の成膜時に、酸素の活性種がCF膜中の炭素と反応することが抑えられ、従ってCF膜の脱ガス量が低減する。またSiCN膜をハードマスクとして使用する場合も、同様に最初にトリメチルシランガスのプラズマ処理を行う。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の信頼性を向上させることができる製造方法を提供する。

【解決手段】半導体基板1に形成される半導体素子を覆う絶縁膜11が、埋め込み特性が良好とされる熱CVD法等によって形成される。その絶縁膜11を覆うように、耐湿性に優れているとされるプラズマCVD法によって絶縁膜14が形成される。その絶縁膜11および絶縁膜14を貫通するようにプラグ13が形成される。さらに、その絶縁膜14上に、誘電率が比較的低いLow−k膜からなる絶縁膜16が形成され、その絶縁膜16に、ダマシン技術によって、プラグ13に電気的に接続される配線20が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】配線層の配線同士間の容量を低くしたままで、機械強度の低下を防ぐことが可能な半導体装置およびその製造方法を提供すること目的とする。

【解決手段】本発明に係る半導体装置およびその製造方法によれば、下地層1,2,3上に形成された第1の配線層6と、第1の配線層6と同一面内に形成され、所定の温度で気化する配線層間膜4とを備える。そして、第1の配線層6上、および、配線層間膜4上に形成された拡散防止膜7を備え、第1の配線層6に沿って第1の配線層6と同一面内にエアギャップ8が設けられている。

(もっと読む)

半導体装置の製造方法

【課題】バリア膜を良好に形成することができながら、Cu配線中のMnの残留量を低減することができる、半導体装置の製造方法を提供する。

【解決手段】SiおよびOを含む第2絶縁層6に、第2溝11およびビアホール12が形成された後、Mnからなる金属膜18が第2溝11およびビアホール12の側面および底面に被着される。次いで、金属膜18中のMnと第2絶縁層6中のSiおよびOとを結合させるための熱処理が行われる。この熱処理の結果、第2溝11およびビアホール12の内面上に、MnSiOからなるバリア膜が形成される。

(もっと読む)

半導体装置の製造方法

【課題】溝を埋め尽くすように形成されるCu層中のMnの残留量の増加を生じることなく、溝の側面上における合金膜の膜剥がれの発生を防止することができる、半導体装置の製造方法を提供する。

【解決手段】SiおよびOを含む絶縁材料からなる第2絶縁層6に、第2溝11が形成される。次に、スパッタ法により、第2溝11の内面に、CuMn合金からなる合金膜18が被着される。この合金膜18は、第2溝11の内面に接する部分のMn濃度が相対的に高く、その表層部分のMn濃度が相対的に低くなるように形成される。次いで、合金膜18上に、Cuからなる第2配線14が形成される。第2配線14の形成後、熱処理により、第2配線と第2絶縁層6との間に、MnSiOからなる第2バリア膜13が形成される。

(もっと読む)

半導体装置

【課題】切断された電気ヒューズの切断状態を良好に保つ。

【解決手段】半導体装置200は、基板上に形成された下層配線120と、下層配線120上に下層配線120に接続して設けられたビア130と、ビア130上にビア130に接続して設けられた上層配線110とを含む電気ヒューズ100であって、切断状態において、電気ヒューズ100を構成する導電体が外方に流出してなる流出部が形成されることにより切断される電気ヒューズ100と、上層配線110および下層配線120の一方と同層に上層配線110および下層配線120の一方の側方に形成されるとともに、上層配線110および下層配線120と電気的に接続された熱拡散用上層配線152aを含む熱拡散部150aとを含む。

(もっと読む)

半導体装置の製造方法

【課題】素子全体の機械的な強度の低下を防ぎ、配線を伝播する信号の遅延を低減する。

【解決手段】各配線層100を構成する第1の絶縁層及び前記第3の絶縁層がシリコン炭化窒化膜、シリコン炭化物及び/又はシリコン酸化物を含み、下層配線層の第2の絶縁層はシリコン酸化物を含み、上層配線層の第2の絶縁層はフッ素添加シリコン酸化物及び/又は炭素添加シリコン酸化物を含む。下層配線層の第2の絶縁層の比誘電率を、上層配線層の第2の絶縁層の比誘電率よりも小さくする。

(もっと読む)

半導体装置の製造方法

【課題】溝の側面上における金属膜の膜剥がれの発生を防止することができながら、Cu配線中のMnの残留量を低減させることができる、半導体装置の製造方法を提供する。

【解決手段】第1配線5上に、SiおよびOを含む第2絶縁層6が形成された後、第2絶縁層6に、第2溝11およびビアホール12が形成される。次に、スパッタ法により、溝の内面およびビアホールの内面に、MnOからなる金属膜18が被着される。このとき、第2溝11の内面およびビアホール12の側面には、スパッタリングのエネルギーによって、金属膜18中のMnOが入り込み、MnSiOからなる第2バリア膜13が形成される。そして、金属膜18におけるビアホール12の底面に形成された部分が除去された後、ビアホール12にビア15が埋設されるとともに、第2溝11に第2配線14が埋設される。

(もっと読む)

半導体装置の製造方法

【課題】溝の側面上における合金膜の膜剥がれの発生を防止することができる、半導体装置の製造方法を提供する。

【解決手段】SiおよびOを含む絶縁材料からなる第2絶縁層6に、第2溝11が形成され、第2溝11と第1溝3とが対向する部分にビアホール12が貫通形成された後、スパッタ法により、CuMn合金からなる合金膜18が第2溝11およびビアホール12の側面および底面に被着される。そして、合金膜18における第2溝11の底面および第1配線5上に被着された部分が薄くされる。その後、合金膜18上に、Cuを主成分とする金属材料からなる第2配線14が形成される。第2配線14の形成後、熱処理により、第2配線と第2絶縁層6との間に、MnSiOからなる第2バリア膜13が形成される。

(もっと読む)

金属相互接続のための共形接着促進材ライナ

【課題】 金属相互接続のための共形接着促進材ライナを提供すること

【解決手段】 誘電体層を少なくとも1つのライン・トラフ及び/又は少なくとも1つのビア・キャビティを有するようにパターン化する。金属窒化物ライナをパターン化誘電体層の表面上に形成する。金属ライナを金属窒化物ライナの表面上に形成する。共形銅窒化物層を、原子層堆積(ALD)又は化学気相堆積(CVD)によって、金属ライナの直接上に形成する。Cuシード層を共形銅窒化物層の直接上に形成する。少なくとも1つのライン・トラフ及び/又は少なくとも1つのビア・キャビティは、電気めっき材料で充填される。共形銅窒化物層とCuシード層との間の直接接触は、強化された接着強度を与える。共形銅窒化物層をアニールして、露出した外側部分を連続的なCu層に変換することができ、このことはCuシード層の厚さを減すのに用いることができる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、絶縁膜の誘電率を低く維持すると共に、半導体装置の信頼性を高めること。

【解決手段】シリコン基板1の上方に層間絶縁膜29を形成する工程と、層間絶縁膜29に配線溝29aを形成する工程と、層間絶縁膜29の上面と配線溝29aの中とに導電膜27を形成する工程と、導電膜27を研磨することにより、層間絶縁膜29の上面から導電膜27を除去すると共に、配線溝29aの中に導電膜27を残す工程と、導電膜27の表面を還元性プラズマに曝す工程と、導電膜27の表面にシリサイド層34を形成する工程と、シリサイド層34の表面に窒化層36を形成する工程と、炭素を含むガス又は液に層間絶縁膜29の上面を曝す工程と、層間絶縁膜29の上面に紫外線を照射する工程と、導電膜27の上にバリア絶縁膜40を形成する工程とを有する半導体装置の製造方法による。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】より簡易な工程(処理内容)を用いて、導電層表面にキャップ膜を形成することを可能とする。

【解決手段】 基板の上に層間絶縁膜を形成する工程と、前記層間絶縁膜中に開口部を形成する工程と、前記開口部とを充填する導電層を形成する工程と、前記導電層の表面にキャップ膜を形成する工程と、を含み、前記キャップ膜を形成する工程において、導電層の表面の還元処理と、膜形成とが同時に行われる。

(もっと読む)

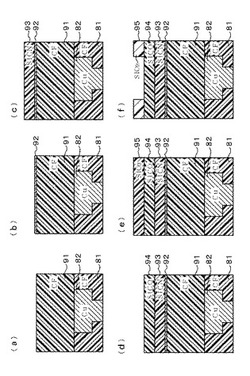

半導体装置とその製造方法

【課題】半導体基板の表裏両面間を貫通電極で接続するにあたって、貫通孔底部の角部におけるリーク電流の発生や絶縁膜のクラック等を抑制する。

【解決手段】半導体装置1は貫通孔3を有する半導体基板2を備える。貫通孔3は半導体基板2の第1の面2aに開口された第1の開口3aの開口径が第2の面2bに開口された第2の開口3bに近い側の内径より大きくなるように、第1の面2aの近傍を拡張させる拡張部4を備える。半導体基板2の第1の面2aには第1の絶縁層5と第1の配線層6とが設けられている。貫通孔3には拡張部4を充填しつつ内壁面を覆う第2の絶縁層7が設けられており、さらに第1および第2の絶縁層5、7の開口を介して第1の配線層6と接続された第2の配線層8が設けられている。

(もっと読む)

半導体装置とその製造方法

【課題】合成抵抗を用いることなく、複数の抵抗値を得ることが可能な抵抗素子を備えた半導体装置を提供する。

【解決手段】半導体基体上に形成された抵抗率の異なる複数の導電層と、複数の絶縁層とからなる抵抗素子を備える半導体装置を構成する。そして、この抵抗素子は、開孔部と、開孔部内に形成された複数の導電層の何れか一層と接続する接続配線と、接続配線の側面に形成される絶縁層とを備える。

(もっと読む)

成膜方法及び処理システム

【課題】例えばCu膜に対するバリヤ性及び密着性を高く維持することができる層構造を形成する成膜方法を提供する。

【解決手段】真空引き可能になされた処理容器132内で、表面に凹部2を有する被処理体Wの表面に成膜処理を施す成膜方法において、遷移金属含有原料ガスを用いて熱処理により遷移金属含有膜210を形成する遷移金属含有膜形成工程と、元素周期表のVIII族の元素を含む金属膜212を形成する金属膜形成工程とを有するようにする。これにより、例えばCu膜に対するバリヤ性及び密着性を高く維持する。

(もっと読む)

半導体装置の製造方法

【課題】レジストポイゾニングの発生を抑制する信頼性の高い半導体装置を実現する。

【解決手段】ビアホール111を形成した後に溝114を形成する工程において、ビアホール111の形成領域に露光を行う工程と、配線溝の形成領域に露光を行う工程が含まれる。すなわち、ビアホール111を形成した後にビアホール111内に化学増幅型レジスト108が埋設されても、その後再びビアホール111の形成領域に露光が行われるため、ビアホール111の内部に十分な露光がされるようになる。これにより、ビアホール111内の感光領域、すなわち領域112および領域113が現像液で除去され、ビアホール111の内壁面の少なくとも一部が露出し、所望の構造の溝114が得られる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】基板に発生する応力を低減できる半導体装置及び半導体装置の製造方法を提供する。

【解決手段】本発明の一態様に係る半導体装置は、半導体素子が形成される素子領域を有する基板と、素子領域の隣接部分の基板に形成されるビアホールと、ビアホール内に絶縁層を介して設けられる導通部と、基板と絶縁層との間に設けられる緩衝層とを備え、緩衝層は、基板の熱膨張係数と緩衝層の熱膨張係数との差が、基板の熱膨張係数と絶縁層の熱膨張係数との差より小さい材料から形成される。

(もっと読む)

半導体装置の製造方法

【課題】WPP技術を使用する半導体装置の信頼性向上を図ることができる技術を提供する。

【解決手段】半導体ウェハW3に形成されている製品チップ領域(例えば、製品チップ領域CAや製品チップ領域CB)に製品パターンを形成する。そして、製品チップ領域の外側にある外周領域の大部分にも製品パターンの一部を形成する。一方、外周領域に形成されているネーミング領域NRを覆うように開口部を有さないレジストパターンRMを形成する。外周領域に形成されているレジストパターンRMと製品チップ領域CBとの間に開口パターンKP1を形成する。このようなパターンが形成された半導体ウェハW3に対して、電解めっきを実施する。

(もっと読む)

薄いバリア層を用いた多孔性誘電体への溶媒および溶液の侵入の阻止および低減

基板を処理するための方法および装置が提供される。基板上に多孔性誘電体層が形成される。いくつかの実施形態では、誘電体を緻密な誘電体層によって覆うことができる。誘電体層がパターン形成され、基板の上に緻密な誘電体層が共形的に堆積される。緻密な共形の誘電体層は、多孔性誘電体層の孔を、孔に浸入する可能性がある化学種と接触しないように密封する。緻密な共形の封孔誘電体層の、フィールド領域とパターン開口部の底部とを覆う部分が、指向性の選択的なエッチングによって除去される。  (もっと読む)

(もっと読む)

半導体装置

【課題】配線とビアとの界面でのボイドの発生を抑制し、信頼性に優れた半導体装置を提供すること。

【解決手段】半導体装置1は、比誘電率が3.0以下の低誘電率の絶縁膜112中に形成され、配線幅が0.1μm以下の配線14と、配線14に接続された径が0.1μm以下のビア17と、絶縁膜112中に形成されたダミーメタル15とを有し、ダミーメタル15は、配線14の端部に対し、配線14の延在方向に沿って隣接し、ダミーメタル15と、配線14との間の距離Dが0.3μm以下である。

(もっと読む)

161 - 180 / 665

[ Back to top ]