Fターム[5F033RR11]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | ハロゲンを含むもの(SiOFを含む) (665)

Fターム[5F033RR11]に分類される特許

101 - 120 / 665

ビア構造とそれを形成するビアエッチングプロセス

【課題】ビア構造とそれを形成するビアエッチングプロセスを提供する。

【解決手段】ビアエッチングプロセスは、丸角とテーパ型側壁プロファイルを有するスルーサブストレートビアを形成する。その方法は、半導体基板を提供するステップと、半導体基板上に、ハードマスク層とパターン化フォトレジスト層を形成するステップと、ハードマスク中に開口を形成して、半導体基板の一部を露出するステップと、パターン化されたフォトレジスト層とハードマスク層をマスキング要素として、半導体基板の少なくとも一部を通過するビアを形成するステップと、トリミングプロセスを実行して、ビアの頂角を丸くするステップと、フォトレジスト層を除去するステップと、からなる。

(もっと読む)

プラズマ処理による酸化物又は他の還元可能な汚染物質の基板からの除去

【課題】VLSI技術及びULSI技術において多段相互接続は、アスペクト比の高いバイアや他の相互接続が注意深く処理されることを要する。これらの相互接続の確実な形成技術を提供する。

【解決手段】窒素と水素を含有する化合物、一般にアンモニアを使用し、次層を上へ堆積するに先立ち相対的に低い温度で酸化物又は他の汚染物質を還元する、プラズマ還元プロセスを提供する。酸化物の層の典型的な物理的スパッタ洗浄プロセスと比較して、層の粘着特性が改善され酸素の存在が減少する。このプロセスは、デュアルダマシン構造、とりわけ銅が応用されている場合の複雑な要求に特に有効であろう。

(もっと読む)

半導体装置の製造方法

【課題】 CVD−MnOxをバリア膜に用いても歩留りの低下を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】 N層以上の銅、又は銅合金配線4、8を有し、これらN層の銅、又は銅合金配線4、8のバリア膜としてCVD−MnOx膜を使用する半導体装置の製造方法であって、第1層乃至第N−1層のCVD−MnOx膜3は、セルフリミットがかかる前に成膜を完了させ、第N層のCVD−MnOx膜7は、セルフリミットがかかるように成膜する。

(もっと読む)

半導体装置

【課題】容量素子を構成する第1電極及び第2電極を形成するためのリソグラフィ工程で重ね合わせズレが生じた場合にも容量ばらつきを抑制できる半導体装置を提供する。

【解決手段】複数の配線層L1〜L5のそれぞれは、絶縁膜103〜106と、当該絶縁膜中に相互に離隔し且つ向かい合うように埋め込まれた第1電極101及び第2電極102とを有する。一の配線層の第1電極101と、その上方又は下方に設けられた他の配線層の第2電極102とは相互に向かい合うように配置されている。一の配線層の第1電極101の幅と、他の配線層の第2電極102の幅とは異なっている。

(もっと読む)

半導体装置の製造方法

【課題】シールリングの構造を最適化して、ダイシング部の切断面からの水分の侵入やクラックの伸展に対する障壁としての機能を確保したシールリングを備えた半導体装置の製造方法を提供する。

【解決手段】半導体基板1上の回路形成領域とダイシング領域との間にシールリング100が配設されている。シールリング100は、断面形状がT字型をなすシール層が積層された部分と、断面形状が矩形をなすシール層が積層された部分とを有している。

(もっと読む)

半導体集積回路装置の製造方法

【課題】Cuダマシン多層配線構造におけるセミ・グローバル配線の形成方法において、ダマシン配線構造を形成する際、ドライ・エッチングによりビア底のエッチ・ストップ絶縁膜を除去した後、ビア底表面上のカーボン系堆積物等を抑制する為に、窒素プラズマ処理を行うことが一般的である。その後、連続放電によって窒素プラズマ除電を行ってウエハ搬送するシーケンスを実行すると、ビア・チェーン終端部にて、ある閾値以上の長さを有するパッド引き出し配線に接続された終端部のビア底で、Cuえぐれが発生ことが、本願発明者らの検討によって明らかとなった。

【解決手段】本願発明は、ダマシン・セミ・グローバル配線等のビア・ホール形成工程において、ビア底エッチ・ストップ膜に対するドライ・エッチング処理後、同処理室内で行われる窒素プラズマ処理に引き続いて、アルゴン・プラズマによる除電処理を実行するものである。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体界面のダングリングボンドを終端させて、リーク電流が少ない半導体装置の製造方法を提供する。

【解決手段】ボンディングパッド40が設けられる最上層の配線層39の上に、フッ素を含んだ介在層41としてCVD法によりよって形成されたフッ素含有酸化シリコン膜(SiOF)を設ける。この上にパッシベーション膜42としてプラズマCVD法により形成した窒化シリコン膜を設け、フッ素に対するバリアとする。この後熱処理を行い、フッ素をシリコン基板の表面に拡散させる。

(もっと読む)

半導体集積回路装置の製造方法

【課題】近年、半導体集積回路装置の製造プロセスにおいて、窒化シリコン膜等が有する応力に起因する歪を利用したキャリア移動度向上技術が活用されている。これに伴って、ウエハの表側における複雑なデバイス構造上の窒化シリコン膜を高選択で除去するため、熱燐酸によるバッチ方式ウエット処理が必須となっている。これによって、ウエハの裏面の窒化シリコン膜も除去され、一群の歪付与工程の後のプロセスにおいては、ウエハの裏側の表面はポリ・シリコン部材ということとなる。しかし、一般的なウエハの裏面等の洗浄に使用する方法は、裏面が窒化シリコン膜等であることを前提とするものであり、その特性の異なるポリ・シリコン主体の裏面を有するウエハでは洗浄の効果が十分といえない恐れがある。

【解決手段】リソグラフィ工程の前に、FPM処理の後SPM処理を実行する2工程を含むウエハ裏面に対するウエット洗浄処理を実行する。

(もっと読む)

イメージセンサー装置および半導体イメージセンサー装置の製造方法

【課題】半導体イメージセンサー装置を提供する。

【解決手段】半導体イメージセンサー装置は、第一および第二半導体基板を含む。画素アレイと制御回路とが、第一基板の第一表面中に形成される。相互接続層が、第一基板の第一表面の上に形成され、制御回路を画素アレイに電気的に接続する。頂部導電層が、相互接続層を介して制御回路または画素アレイの少なくとも一つと電気的接続を有するように、相互接続層の上に形成される。第二基板の表面は、頂部導電層に接合される。導電性スルーシリコンビア(TSV)は第二基板を貫通し、頂部導電層と電気的接続を有する。第二基板の反対の表面上に端子が形成され、TSVに電気的に接続される。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】一般的なウエハ・レベル・パッケージ・プロセスでは、メッキ・プロセス中におけるスクライブ領域のアルミニウム系パッド電極の腐食を防止するために、製品領域における有機系保護膜と同層のパッド保護用樹脂膜でパッド電極をカバーしている。しかし、これでは再配線形成後にスクライブ領域のパッド電極に対するプローブ検査が実行できない。

【解決手段】本願発明は、ウエハ・レベル・パッケージ方式の半導体集積回路装置の製造方法において、チップ領域およびスクライブ領域の有機系保護膜を相互に連結した一体の膜パターンとし、ペレタイズ工程においては、スクライブ領域中央部の有機系保護膜を含む表層部分を先ず、レーザ・グルービングで除去することで幅広の溝を形成し、その後、この溝内の中央部をダイシング処理することで、ここのチップ領域に分離するものである。

(もっと読む)

半導体装置、その半導体装置の作製方法及びその半導体装置を有する電子機器

【課題】酸化物半導体を用いた薄膜トランジスタにおいて、電界効果移動度を向上させることを課題の一とする。また、薄膜トランジスタの電界効果移動度を向上させても、オフ電流の増大を抑制することを課題の一とする。

【解決手段】酸化物半導体層を用いた薄膜トランジスタにおいて、酸化物半導体層とゲート絶縁層の間に、該酸化物半導体層より導電率が高い酸化物クラスターを形成することによって、該薄膜トランジスタの電界効果移動度を向上させ、且つオフ電流の増大を抑制することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】相異なる膜質領域を有する層間絶縁膜において、膜界面における膜剥れや隣接配線間リークの発生を抑制する。

【解決手段】単層構造の層間絶縁膜である第3の絶縁膜107は複数の空孔120を有している。第3の絶縁膜107における単位体積当たりの空孔占有率は膜厚方向に変化している。

(もっと読む)

半導体装置およびその製造方法

【課題】本発明は、裏面コンタクト電極と拡散層とのコンタクト抵抗が低減して、半導体装置の動作速度の向上を図ることを可能にする。

【解決手段】基板10の表面側に形成された拡散層25P、26P、25N、26Nと、前記拡散層25P、26P、25N、26Nの表面に形成されていて前記拡散層25P、26P、25N、26Nよりも抵抗が低い低抵抗部27P、28P、27N、28Nと、前記基板10の裏面側より前記基板10を貫通して前記拡散層25P、26P、25N、26Nを通して前記低抵抗部27P、28P、27N、28Nに接続された裏面コンタクト電極63P、64P、63N、64Nを有する。

(もっと読む)

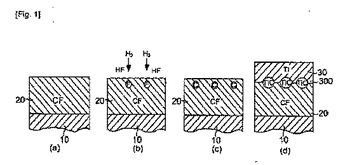

フッ化炭素膜の表面処理

半導体デバイスの製造方法は、絶縁性層をアニーリングする工程と、金属元素を含んだ障壁層を前記絶縁性層上に形成する工程とを含んでいる。前記絶縁性層は、フッ化炭素(CFx)膜を含んでいる。前記障壁層は、前記アニーリング工程後に、高温スパッタリングプロセスによって形成される。  (もっと読む)

(もっと読む)

低k誘電体ライナーを有するシリコン貫通ビア

【課題】 シリコン貫通ビアを有する半導体デバイスを提供する。

【解決手段】 回路面と前記回路面とは逆の背面を有する半導体基板、前記半導体基板を穿通して延伸するシリコン貫通ビア、及び前記シリコン貫通ビアと前記半導体基板の間に設置され、前記半導体基板の前記背面の表面の少なくとも一部の上に延伸する誘電体層を含む半導体デバイス。

(もっと読む)

半導体装置

【課題】多層配線を形成する際における配線の加工に要する工程を簡便にすることを課題

とする。また、開口径の比較的大きいコンタクトホールに液滴吐出技術やナノインプリン

ト技術を用いた場合、開口の形状に沿った配線となり、開口の部分は他の箇所より凹む形

状となりやすかった。

【解決手段】高強度、且つ、繰り返し周波数の高いパルスのレーザ光を透光性を有する絶

縁膜に照射して貫通した開口を形成する。大きな接触面積を有する1つの開口を形成する

のではなく、微小な接触面積を有する開口を複数設け、部分的な凹みを低減して配線の太

さを均一にし、且つ、接触抵抗も確保する。

(もっと読む)

半導体装置の製造方法

【課題】多層配線構造において、下層金属配線への接続用スルーホール内にボイドが発生することを防止する半導体装置の製造方法を提供する。

【解決手段】半導体基板上に金属配線3を形成し、全面に層間絶縁膜4を形成する。絶縁膜内にスルーホールを形成する。スパッタエッチングにより、スルーホール開口部に傾斜部を設け断面を大きくするとともに金属配線の表面の酸化Alを除去する。半導体基板を冷却し、基板温度20℃〜40℃で、スルーホールの内面を含む全面に第1のチタン膜6、窒化チタン膜7、第2のチタン膜8、第1のAl層9aを形成する。続いて基板を加熱して第2のAl層9bをリフローしながら形成した後、第3のAl層9cを形成する。

(もっと読む)

金属層間誘電体による拡散防止バリヤ層を有する集積回路およびその製造方法。

【課題】ライン間キャパシタンスを減少できる構造を有する集積回路および不純物が多層集積回路構造の次の層に存在する導電性要素に対し破壊的反応を起こすのを防止できる集積回路の製造方法を提供する。

【解決手段】低誘電率材料中での不純物の移動を防止できるキャップ層あるいはバリヤ層により、不純物が多層集積回路構造の次の層に存在する導電性要素に対し破壊的反応を起こすのを防止する。集積回路は第一の誘電体層と集積回路のより上層の導電層間に拡散防止バリヤ層を堆積して製造される。拡散防止バリヤ層はその次の金属層で不純物を含む誘電体層へその場で形成され、さらに、研磨を含む処理が多層誘電体構造に対してなされる。キャップ層あるいはバリヤ層にその場堆積は不純物を含む層を雰囲気にさらすのを防止し、そしてキャップ層あるいはバリヤ層により、水分、水素あるいはそのたのものにより、層が汚染されるのを防止することができる。

(もっと読む)

コバルト膜の形成方法

【課題】コバルト前駆体の使用効率の高い、化学気相成長方法によるコバルト膜の形成方法を提供すること。

【解決手段】上記コバルト膜の形成方法は、基体上にコバルト膜を形成する方法であって、少なくとも(A)一酸化炭素を含む気体の存在下でコバルトカルボニル錯体を昇華する工程と(B)基体上にコバルトカルボニル錯体の昇華物を供給してコバルトに変換する工程とを含むことを特徴とする方法である。

(もっと読む)

半導体装置

【課題】半導体装置の特性の安定化を図ることができるとともに、半導体装置の耐圧を向上することができる半導体装置を提供する。

【解決手段】半導体装置2の活性領域Aでは、半導体層4の上側の少なくとも一部に第1絶縁層18が形成されている。第1絶縁層18は、半導体層4が有するダングリングボンドを終端させる終端材料を含んでいる。耐圧領域Bでは、半導体層4の上側に第1絶縁層と異なる材料からなる第2絶縁層20が形成されており、第1絶縁層18は形成されていない。そして、第2絶縁層20が第1絶縁層18より絶縁度が高くされている。

(もっと読む)

101 - 120 / 665

[ Back to top ]