Fターム[5F033RR11]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | ハロゲンを含むもの(SiOFを含む) (665)

Fターム[5F033RR11]に分類される特許

141 - 160 / 665

半導体装置

【課題】開口部の底部に電極パッドとして露出させた外部接続電極に接続ツールを用いて導電体を接続する場合に、電極パッドの面積を拡大することなく、接続ツールの先端が開口部の縁に接触することを回避可能な仕組みを提供する。

【解決手段】半導体素子層7と、半導体素子層7の一方の面側に、複数の配線層13,15,17と複数の層間絶縁膜12,14,16,18により形成された積層配線部11と、複数の配線層のうちの一つに形成された外部接続電極17aと、外部接続電極17aの表面を露出させる状態で半導体素子層7から積層配線部11にかけて凹状に形成された開口部22とを備える固体撮像装置の構成として、外部接続電極17aから遠い方の開口径d1が、外部接続電極17aに近い方の開口径d2より大きくなるように、開口部22を形成した。

(もっと読む)

研磨方法

【課題】 二酸化珪素を主体とする層間絶縁膜とlow−k膜を、共に高速に研磨でき、更には、研磨傷が少なくできる研磨方法を提供する。

【解決手段】 表面に凹部及び凸部を有する層間絶縁膜と、この層間絶縁膜を被覆するバリア層と、前記凹部を充填し、バリア層を被覆する導電性物質層とを有する基板の研磨方法において、導電性物質層を研磨して前記凸部のバリア層を露出させる第1の化学機械研磨工程の後に、基板をショア硬度(Dスケール)で40以上のハードタイプパッド上に押圧した状態で、CMP用研磨液を供給しながら研磨定盤と基板とを相対的に動かすことによって、バリア層と凹部の導電性物質層と層間絶縁膜とを研磨し、更にショア硬度(Dスケール)で40未満のソフトタイプパッド上に押圧した状態で、上述のCMP用研磨液と同一組成のCMP用研磨液を供給しながら研磨定盤と基板とを相対的に動かすことによって、導電性物質層と層間絶縁膜を研磨する第2の化学機械研磨工程を行う研磨方法。

(もっと読む)

半導体装置

【課題】無線通信機能を有する半導体装置に振幅の大きい信号が供給された場合においても正常に動作し、且つ信頼性の高い半導体装置を提供する。

【解決手段】半導体装置は、交流電圧を生成するアンテナ101と、交流電圧を整流し、内部電圧Vinを生成する整流回路102と、第1の保護回路107と、第2の保護回路108と、を有する。第1の保護回路107は、第1のダイオード201と、第2のダイオード202と、を有し、第2の保護回路は、容量素子203と、トランジスタ204と、を有する。第1の保護回路は、アンテナ101で生成される交流電圧の絶対値がある値よりも大きい場合に、その余剰分をカットし、第2の保護回路108は、整流回路102で生成された内部電圧Vinが大きい場合に機能し、共振周波数をずらすことにより、半導体装置に入力される信号を減少させることができる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【目的】TDDB寿命を長くすることが可能な半導体装置の製造方法を提供することを目的とする。

【構成】本発明の一態様の半導体装置の製造方法は、基体上に絶縁膜を形成する工程(S104)と、前記絶縁膜上に、ポアが形成されるキャップ膜を形成する工程(S106)と、前記キャップ膜と前記絶縁膜に開口部を形成する工程(S110)と、前記開口部内に導電性材料を堆積させる工程(S116)と、前記開口部内に前記導電性材料が堆積させられた後に、前記ポアの一部を残しながら一部が前記キャップ膜中に食い込むように、前記キャップ膜上に前記導電性材料の拡散を防止する拡散防止膜を形成する工程(S122)と、を備えたことを特徴とする。

(もっと読む)

銅配線、銅配線の形成方法および半導体装置

【課題】銅配線本体の開放表面に形成されるマンガンを含むバリア層に最適な内部構成を持たせて、そのバリア機能を充分に発揮させることができる半導体素子の製造方法を提供する。

【解決手段】銅配線1は、電気絶縁層3に銅からなる配線本体8を備える。配線本体の外周81は、電気絶縁層に対向している第1の外周8aと電気絶縁層との間に形成された第1のバリア層7aと、配線本体の外周のうち電気絶縁層に対向していない第2の外周8bに接して形成された第2のバリア層7bとを備える。第1および第2のバリア層はそれぞれマンガンを含む酸化物層からなるとともに、各バリア層内の厚さ方向でマンガンの原子濃度が極大となる位置を有する。

(もっと読む)

半導体装置

【課題】金属パッドの下方に位置する層間絶縁膜にクラックが発生し、クラック内に水分が進入することがあっても、金属パッドの近傍の配線の信頼性が低下することを防止する。

【解決手段】半導体基板10上に形成された層間絶縁膜18と、層間絶縁膜18を貫通して設けられたリング用金属配線20Aと、層間絶縁膜18を貫通して設けられたコンタクト用金属配線20Bと、層間絶縁膜18上及びリング用金属配線20Aの全上面上に形成された第1の保護絶縁膜21と、第1の保護絶縁膜21上に形成された金属パッド23とを備え、リング用金属配線20Aは、層間絶縁膜18のうち金属パッド23の下方に位置する領域にリング状に設けられており、金属パッド23は、第1の保護絶縁膜21に形成された第1の開口部21aを通じてコンタクト用金属配線20Bに接続されている。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置及びその製造方法について、ホウ素含有タングステン層を核形成層とする場合に、コンタクト抵抗値の増大を抑制する。

【解決手段】半導体装置100は、半導体基板101上に形成された第1絶縁膜103と、第1絶縁膜103に埋め込まれた導電膜109を含み且つ半導体基板101に達するコンタクト110と、半導体基板101及び第1絶縁膜103のそれぞれと、導電膜109との間に形成され、高融点金属を含む第1バリア層107とを備える。更に、第1バリア層107と導電膜109との間に形成され、第1バリア層107よりも水分透過性の低い第2バリア層118を備える。

(もっと読む)

半導体装置の製造方法

【課題】 半導体ウエハ上に形成された低誘電率膜と配線との積層構造およびパッシベーション膜のうち、ダイシングストリートに対応する部分をレーザビームの照射により除去したとき、それらの除去面から欠落物が生じにくいようにする。

【解決手段】 半導体ウエハ21の上面に4層の低誘電率膜4および同数層の配線5を交互に形成し、その上に窒化シリコン等からなるパッシベーション膜7を形成する。次に、ダイシングストリート23に対応する領域におけるパッシベーション膜7、低誘電率膜4および配線5をレーザビームの照射により除去して溝26を形成する。次に、溝26内を含むそれらの上にポリイミド系樹脂等からなる保護膜9を形成する。これにより、パッシベーション膜7、低誘電率膜4および配線5のレーザビームの照射による除去面が保護膜9によって覆われるので、当該除去面から欠落物が生じるのを可及的に早い段階で確実に防止することができる。

(もっと読む)

半導体装置

【課題】配線層を薄くした場合にも電極パッド形成領域で配線層がなくなることを確実に防止できるようにし、配線層と電極パッドとを安定して電気的に接続させる。

【解決手段】半導体基板1上の第4層間絶縁膜10中に複数のコンタクト用配線11Bが形成されている。各コンタクト用配線11Bの上及び第4層間絶縁膜10の上に第1保護絶縁膜12が形成されており、第1保護絶縁膜12には、各コンタクト用配線11Bを露出させる第1開口部12aが形成されている。第1開口部12aの内部にはバリアメタル膜13を介して、コンタクト用配線11Bと電気的に接続する電極パッド14が形成されている。第1開口部12aの下側には、コンタクト用配線11Bが配置されていない領域が存在している。

(もっと読む)

表示装置

【課題】動作特性に優れ低温で製造可能な酸化物半導体を用いた表示装置の特性を活かすには、適切な構成を備えた保護回路等が必要となる。

【解決手段】ゲート電極15を被覆するゲート絶縁層37と、ゲート絶縁層37上においてゲート電極15と端部が重畳し、第2酸化物半導体層40と導電層41が積層された一対の第1配線層38及び第2配線層39と、少なくともゲート電極15と重畳しゲート絶縁層37及び該第1配線層38及び該第2配線層39における導電層41の側面部及び上面部の一部と第2酸化物半導体層40の側面部と接する第1酸化物半導体層36とを有する非線形素子30aを用いて保護回路を構成する。

ゲート絶縁層37上において物性の異なる酸化物半導体層同士の接合を形成することで、ショットキー接合に比べて安定動作をさせることが可能となり、接合リークが低減し、非線形素子30aの特性を向上させることができる。

(もっと読む)

半導体集積回路装置および半導体集積回路装置の製造方法

【課題】プリ・メタル層間絶縁膜の構成法としては、オゾンTEOSによる酸化シリコン膜の埋め込み特性の良好なCVD酸化シリコン系絶縁膜を成膜後、高温リフローさせて平坦化した後、CMPスクラッチ耐性が良好なプラズマTEOSによる酸化シリコン膜を積層し、更にCMPで平坦化することが考えられる。しかし、コンタクト・ホール形成プロセスにおいて、プリ・メタル層間絶縁膜中のクラックがコンタクト・ホール内に露出し、そこにバリア・メタルが入り込み、ショート不良の原因となることが明らかとなった。

【解決手段】本願発明はプリ・メタル工程において、エッチ・ストップ膜上にオゾンTEOS膜を形成後、一旦、ゲート構造上のエッチ・ストップ膜が露出するようにオゾンTEOS膜をエッチバックし、その後、残存オゾンTEOS膜上にプラズマTEOS膜を成膜し、このプラズマTEOS膜をCMPにより、平坦化するものである。

(もっと読む)

半導体装置の製造方法

【課題】Cu配線中のMnの残留量を減らすことができる、半導体装置の製造方法を提供する。

【解決手段】Cu層20の形成後、Cu層20上に、高純度Cuからなる犠牲層31が積層される。そして、犠牲層31の形成後、熱処理により、Cu層20と第2絶縁層6との間に、MnSiOからなる第2バリア膜13が形成される。このとき、第2バリア膜13の形成に寄与しない余剰のMnは、Cu層20中に拡散する。Cu層20上に高純度Cuからなる犠牲層31が積層されているので、Cu層20に拡散したMnの一部は、Cu層20中を犠牲層31に引き寄せられるように移動し、犠牲層31に拡散する。この犠牲層31へのMnの拡散により、Cu層20に含まれるMnの量が減少する。よって、Cu層20からなる第2Cu配線中のMnの残留量を減らすことができる。

(もっと読む)

半導体装置の製造方法

【課題】Cu配線中のMnの残留量を減らすことができる、半導体装置の製造方法を提供する。

【解決手段】合金膜18上に、SiおよびOを含む絶縁材料からなる犠牲層41が積層される。犠牲層41の積層後、熱処理が行われる。第2絶縁層6および犠牲層41にSiおよびOが含まれるので、熱処理が行われると、第2絶縁層6と合金膜18との界面および合金膜18と犠牲層41との界面において、Si、OおよびMnが結合し、それぞれMnSiOからなる第2バリア膜13および反応生成膜42が形成される。合金膜18に含まれるMnが反応生成膜42の形成に使用されることにより、第2バリア膜13の形成後、その第2バリア膜13の形成に寄与せずに合金膜18に残留するMnの量が減少する。そのため、合金膜18上に積層されるCu層20に拡散するMnの量が減少する。よって、Cu層20からなる第2Cu配線中のMnの残留量を減らすことができる。

(もっと読む)

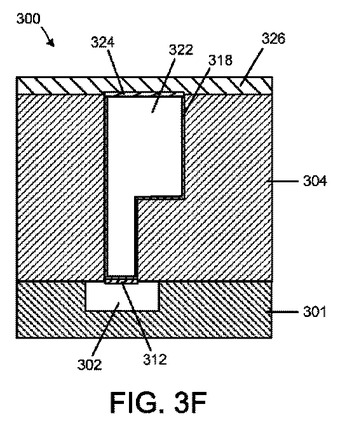

ローカルインタコネクトを備えた半導体装置

【課題】ローカルインタコネクトを備えた半導体装置を提供する。

【解決手段】ローカルインタコネクトを備えた半導体装置であって、基板上に配置され、実質的に同一線上にある第1ゲート線構造と第2ゲート線構造、前記第1ゲート線構造の両側の前記基板に形成された第1対ソース/ドレイン領域と前記第2ゲート線構造の両側の前記基板に形成された第2対ソース/ドレイン領域、及び前記第1ゲート線構造と前記第2ゲート線構造の両側の前記基板上に配置され、それらが前記第1対ソース/ドレイン領域のうちの1つと前記第2対ソース/ドレイン領域のうちの1つに接続された一対の導電線を含む半導体装置。

(もっと読む)

半導体装置の製造方法

【課題】Cu配線中のMnの残留量を減らすことができる、半導体装置の製造方法を提供する。

【解決手段】第2バリア膜13の形成後に、SiH4を含むガスを用いたPECVD法により、Cu層20上にSiおよびOを含む絶縁材料からなる犠牲層21が積層される。犠牲層21にSiおよびOが含まれるので、犠牲層21の積層過程で、Cu層20と犠牲層21との界面にMnSiOからなる反応生成膜22が生じる。この反応生成膜22の生成にMnが使用されることにより、Cu層20に含まれるMnの量が減少する。よって、Cu層20からなる第2Cu配線中のMnの残留量を減らすことができる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体基板に形成される貫通孔底部での絶縁層のノッチの発生、貫通孔下の配線層へのダメージを抑制し、電気的絶縁性の低下や配線層の接続不良を低減できる半導体装置及びその製造方法を提供する。

【解決手段】第一の絶縁層203と、第一の絶縁層上の第一の配線層204と、半導体基板201を貫通し、底部に第一の絶縁層を厚さ方向に除去した部分的なエッチ部を備えた貫通孔201aと、貫通孔の部分的なエッチ部の底部を除く内壁部から半導体基板の第二の面までを覆う第二の絶縁層206と、貫通孔の底部に、第一の配線層が露出するように第一の絶縁層に形成された開口部203aと、該開口部で第一の配線層と接すると共に貫通孔の第二の絶縁層上から半導体基板の第二の面の第二の絶縁層上に亘る第二の配線層202とを有し、開口部に接する第一の絶縁層が、半導体基板に接する第一の絶縁層より小さい厚さを有する。

(もっと読む)

ルテニウム金属キャップ層を形成する方法

ルテニウム(Ru)金属の堆積を半導体デバイスの製造に統合することで、銅(Cu)金属のエレクトロマイグレーション及びストレスマイグレーションを改善する方法が供される。本発明の実施例は、NHx(x≦3)ラジカル及びHラジカルによって、金属層及びlow-k誘電材料を含むパターニングされた基板を処理することで、前記low-k誘電材料に対する前記金属層上でのRu金属キャップ層の選択形成を改善する方法を有する。  (もっと読む)

(もっと読む)

半導体装置の製造方法

【課題】 サイズが異なる必要半導体装置形成領域22aおよび不必要半導体装置形成領域22b、22cを有する半導体ウエハを、必要半導体装置形成領域22aの4辺に沿うダイシングストリート23に沿ってダイシングブレードで切断することにより、必要半導体装置形成領域22aを有する半導体装置を得る半導体装置の製造方法において、ダイシングブレードに銅の目詰まりが生じないようにする。

【解決手段】 不必要半導体装置形成領域22b、22cにおいては、ダイシングストリート23およびその両側に対応する領域を除く領域にのみ銅からなる柱状電極14を形成し、当該ダイシングストリート23およびその両側に対応する領域には柱状電極14は形成しない。これにより、ダイシングブレードに銅の目詰まりが生じないようにすることができる。この場合、半導体ウエハ上に複数層の低誘電率膜と同数層の配線とを交互に積層して形成し、その上に絶縁膜を介して形成された上層配線の接続パッド部上に柱状電極14を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】低誘電率膜配線積層構造部の一部を除去するためのレーザ照射によるレーザ加工を行なったときに発生する不要物が半導体基板の上面側の絶縁膜等に付着することによる悪影響をほとんど皆無とすることができる半導体装置およびその製造方法を提供する。

【解決手段】ダイシングストリート22に対応する部分における半導体ウエハ21の上面に4層の低誘電率膜5および封止膜16が形成されたものを準備し、次に、ブレードを用いて、ダイシングストリート22を含む所定幅領域の半導体ウエハ22の下面側に第1の溝29を形成する。次に、半導体ウエハ21の下面側からのレーザ照射によるレーザ加工により、第1の溝29の部分に残存する半導体ウエハ22および低誘電率膜5に、第1の溝29よりも幅狭の第2の溝30を形成する。

(もっと読む)

半導体装置の製造方法

【課題】溝の側面に対する合金膜の付着性(サイドカバレッジ)を向上させることができる、半導体装置の製造方法を提供する。

【解決手段】合金膜18は、バイアススパッタ法により形成される。そして、そのバイアススパッタ法による合金膜18の形成時には、第2溝11およびビアホール12の内面に向けて飛散するスパッタ粒子のエネルギーにより、第2溝11およびビアホール12の底面に付着しているスパッタ粒子が弾き飛ばされ、その弾き飛ばされたスパッタ粒子が第2溝11およびビアホール12の側面に再付着(リスパッタ)するように、スパッタ粒子を加速するためのRFバイアスが設定される。

(もっと読む)

141 - 160 / 665

[ Back to top ]