Fターム[5F033RR15]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 不純物を含むもの (1,419) | BPSG (694)

Fターム[5F033RR15]に分類される特許

101 - 120 / 694

半導体ウェハ上に銅層を形成する方法

【課題】アスペクト比の高い開口部内に空隙を形成することなく銅層を埋め込むことの可能な電気めっき方法を提供すること。

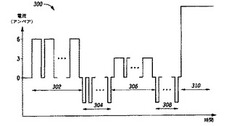

【解決手段】ウェハ上に銅層を形成する方法は、制御システムを有する電気めっきチャンバ内にウェハを配置する段階と、第1期間302の間にウェハに対する第1電力を正にパルス化する段階と、第1期間302に続く第2期間304の間にウェハに対する第2電力を負にパルス化する段階と、第2期間304に続く第3期間306の間にウェハに対する第3電力を正にパルス化する段階とを備える。

(もっと読む)

デバイス構造体およびその形成方法

【課題】 相互かみ合い型導電線を有するキャパシタ構造体ならびにそれを製造する方法を提供する。

【解決手段】 相互かみ合い型構造体は、少なくとも1つの第1の金属線と、少なくとも1つの第1の金属線に平行で、しかも少なくとも1つの第1の金属線から分離されている少なくとも1つの第2の金属線と、少なくとも1つの第1の金属線の端部に接触し、しかも少なくとも1つの第2の金属線から分離されている第3の金属線とを含むことができる。少なくとも1つの第1の金属線はいずれの金属ビアにも垂直に接触しないが、少なくとも1つの第2の金属線は少なくとも1つの金属ビアに垂直に接触することができる。相互かみ合い型構造体の複数の層を垂直に積み重ねることができる。代わって、相互かみ合い型構造体は、複数の第1の金属線と複数の第2の金属線を含むことができ、それぞれの金属線はいずれの金属ビアにも垂直に接触しない。キャパシタを形成するために、回転の有無を問わず、相互かみ合い型構造体の複数の実例を横方向に複製し接合するか、あるいは垂直に積み重ねるか、またはその両方を行うことができる。

(もっと読む)

半導体集積回路装置

【課題】多層配線の下地半導体基板への配線引き出し部のコンタクト抵抗均一化を図った半導体集積回路装置の提供。

【解決手段】半導体集積回路装置は、半導体基板と、前記半導体基板上に複数層積層形成された配線と、前記配線の引き出し領域に前記配線の延長部として形成されて、所定幅のスペースを介して対向するメタル片対により構成されるフックアップ部73と、前記フックアップ部のメタル片対のスペースを貫通するように埋め込まれたコンタクト導体72とを有し、前記配線の少なくとも2層の間で前記フックアップ部のメタル片対のスペース幅を異ならせた。

(もっと読む)

半導体装置及び半導体装置の作製方法

【課題】配線間の寄生容量を十分に低減できる構成を備えた半導体装置を提供することを課題の一とする。

【解決手段】金属薄膜の一部または全部を酸化させた第1の層と酸化物半導体層の積層を用いるボトムゲート構造の薄膜トランジスタにおいて、ゲート電極層と重なる酸化物半導体層の一部上に接するチャネル保護層となる酸化物絶縁層を形成し、その絶縁層の形成時に酸化物半導体層の積層の周縁部(側面を含む)を覆う酸化物絶縁層を形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、配線層の平坦性を保つためのダミーパターンを有する半導体装置とその製造方法を提供することを目的とする。

【解決手段】半導体装置の機能を実現するうえで必要な機能パターンと、半導体装置の所定の層に、前記機能パターンと共に複数のダミーパターンとを備え、第一の大きさの複数のダミーパターンが配置され、前記第一の大きさの複数のダミーパターンが配置されない領域に、第二の大きさの複数のダミーパターンが配置され、前記第一の大きさの複数のダミーパターンと前記機能パターンとの間に前記第二の大きさの複数のダミーパターンが配置され、第一所定方向に配置された前記第一の大きさの複数のダミーパターンと、第二所定方向に配置された前記第二の大きさの複数のダミーパターンとは隣り合い、前記第一の大きさのダミーパターン間の幅は、前記第二の大きさのダミーパターン間の幅よりも大きい。

(もっと読む)

カーボン・ナノチューブを選択的に成長させる方法

【課題】1つ以上のカーボン・ナノチューブを選択的に成長させる方法を提供する。

【解決手段】本方法は、上面を有する絶縁層を基板上に形成するステップと、絶縁層内にビアを形成するステップと、ビアの側壁及び底面を含め、絶縁層上に活性金属層を形成するステップと、ビアの内部での1つ以上のカーボン・ナノチューブの選択的な成長を可能にするために、イオン・ビームを用いて上面の部分にある活性金属層を除去するステップとを含む。

(もっと読む)

半導体装置の製造方法

【課題】CMP工程でその表面が研削され、平坦化された層間絶縁膜IL中にドライエッチングによりコンタクトホール20a等を形成する時、素子分離絶縁膜8a上に形成された最上層がシリサイド層12b、下層がポリシリコン層12aからなる配線層12の、該シリサイド層12bがオーバーエッチングにより消失することを防止する。

【解決手段】N+型埋め込み層2形成時に生じたシリコン段差に起因してN型エピタキシャル層4の表面にも段差が生じる。係る段差の高い部分に形成されたP型分離層5の上に素子分離絶縁膜8aを形成する。該素子分離絶縁膜8a上に上層がシリサイド層12b、下層がポリシリコン層12aからなる配線層12を形成するが、配線層12を形成する前に該素子分離絶縁膜8aの薄膜化を行い、配線層12最上層のシリサイド層12b表面とN+型ソース層15等の表面間の段差を、該素子分離絶縁膜8aの薄膜化する前に比べ小さくする。

(もっと読む)

半導体装置及びその製造方法

【課題】ゲート電極間を埋め込む膜に吸湿性の高い膜を用いた半導体装置において、金属配線の信頼性劣化を防ぐ。

【解決手段】半導体装置50は、基板1上に形成された複数のゲート電極2と、複数のゲート電極2上を含む基板上を覆う第1の層間絶縁膜5と、第1の層間絶縁膜5上を覆う第2の層間絶縁膜6と、第1の層間絶縁膜5及び第2の層間絶縁膜6を貫通し、それぞれ基板1上の所定箇所又は複数のゲート電極2のいずれか一つに達する複数のコンタクトプラグ7と、第2の層間絶縁膜6上に形成され、コンタクトプラグ7に接続された金属配線9を含む配線形成層8とを備える。第1の層間絶縁膜5は、少なくとも一つのゲート電極2上方に第1の凹部5aを有すると共に、複数のゲート電極2及び基板1に接する下部膜3と、第1の凹部5a以外の部分において下部膜3上に配置された上部膜4とを有し、第1の凹部5a内に、第2の層間絶縁膜6が埋め込まれている。

(もっと読む)

半導体集積回路装置

【課題】CMP法により研磨される絶縁膜の平坦性を向上する。

【解決手段】半導体基板1の主面上に形成されたMISFETQ1を覆う層間絶縁膜9の上層に配線10を形成するとともに、その配線10間の間隔が広い領域にダミー配線11を配置する。また、ダミー配線11はスクライブ領域にも配置される。さらに、ダミー配線11は、ボンディングパッドの周辺領域およびマーカの周辺領域には、配置されない。また、MISFETのゲート電極と同層にダミーゲート配線を設ける。また、浅溝素子分離領域にダミー領域を向ける。これらダミー部材を設けた後に、CMP法で絶縁膜を平坦化する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】主にアルミニウム系通常配線を有するLSIの製造工程BEOLプロセスでは、配線の信頼性に関して、EM耐性およびSM耐性の向上が特に重要である。アルミニウム系配線に関する不良の中でも、配線メタル膜の膨張や欠けの発生は、EM耐性およびSM耐性を大きく劣化させる要因となる。

【解決手段】本願発明は、層間絶縁膜を成膜するプラズマCVDチャンバのウエハ・ステージ上に於いて、アルミニウム系配線メタル膜のパターニングの後であって層間絶縁膜の成膜前に、ウエハのデバイス面に対して、不活性ガスを主要な成分の一つとして含む雰囲気下、アルミニウム系配線メタル膜および層間絶縁膜の成膜温度よりも高いウエハ温度において、プラズマ・アニール処理を実行することにより、配線メタル層の側壁部の付着物が完全に除去され、膨張不良の原因が取り除かれ、更に、不動態化の進行、ストレス開放等により、欠け不良を抑制するものである。

(もっと読む)

半導体装置の作製方法

【課題】電界メッキ法やCMP法を使わないことで製造コストを落として配線を形成する半導体装置の作製方法を提供する。

【解決手段】絶縁膜を形成する工程と、絶縁膜上にマスクを形成する工程と、選択的にエッチングして絶縁膜に開口部を形成する工程と、マスク上および開口部に第1導電膜を形成する工程と、液滴吐出法により開口部の第1導電膜上に導電材料を含む液滴を滴下する工程と、レーザー光を選択的に照射して導電材料を加熱して第2導電層を形成する工程と、マスク上および第2導電層上に第3導電膜を形成する工程と、マスクを除去すると同時にマスク上に形成された第1導電膜および第3導電膜を除去し、第1導電層および第3導電層を形成する工程とを有する半導体装置の作製方法を提供する。

(もっと読む)

表示装置およびその作製方法

【課題】表示装置の高精細化に伴い、画素数が増加し、ゲート線数、及び信号線数が増加する。ゲート線数、及び信号線数が増加すると、それらを駆動するための駆動回路を有するICチップをボンディング等により実装することが困難となり、製造コストが増大するという問題がある。

【解決手段】同一基板上に画素部と、画素部を駆動する駆動回路とを有し、画素部に酸化物半導体を用いた薄膜トランジスタを用い、さらに駆動回路の少なくとも一部の回路も酸化物半導体を用いた薄膜トランジスタで構成する。同一基板上に画素部に加え、駆動回路を設けることによって製造コストを低減する。

(もっと読む)

半導体装置

【課題】ヒューズ用開口部からガードリング外への水分等の伝達をより強固に防止する。

【解決手段】下地絶縁膜3上に第1シリコン膜パターンからなるシリコンヒューズとシリコン配線パターン7が形成されている。第1シリコン膜パターンとは別途形成された第2シリコン膜パターンからなり、上方から見てヒューズ5の周囲を取り囲み、一部分がシリコン配線パターン7上を跨いで下地絶縁膜上に環状に形成されたシリコンガードリング11が形成されている。シリコンガードリング11と交差している部分のシリコン配線パターン7表面にシリコン表面絶縁膜9が形成されている。シリコン配線パターン7とシリコンガードリング11はシリコン表面絶縁膜9により互いに絶縁されている。シリコンガードリング11上に金属材料からなる環状のガードリング17,19,25,27が上方から見てヒューズ5の周囲を取り囲んで形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu配線層上にCuバンプを形成可能とする半導体装置を提供する。

【解決手段】半導体装置は、シリコン基板1上に形成される保護層6と、前記保護層6に形成され、前記シリコン基板1に形成される半導体素子と電気的に接続するCu配線層9と、前記Cu配線層9を被覆し、前記保護層6上に形成される樹脂膜10と、前記樹脂膜10に形成される開口領域を介して前記Cu配線層9と接続するパッド電極12と、前記パッド電極12上に形成されるCuから成るスタッドバンプ26とを有する。

(もっと読む)

半導体装置の製造方法

【課題】低コストかつ作業効率の高い半導体装置の製造方法を提供する。

【解決手段】シリコン基板110の上に回路パターンを形成し、回路パターンが形成されたシリコン基板110の上に層間絶縁膜140を形成する。層間絶縁膜140に対して第1の加速電圧でイオン注入を行い第1イオン層310を形成する。続いて第1の加速電圧より高い第2の加速電圧でイオン注入を行い第2イオン層320を形成する。その後、層間絶縁膜140を、第2イオン層320の波形上端部320Puが表出するまで研磨する。

(もっと読む)

半導体装置及びその製造方法

【課題】Cu配線層上にCuワイヤを実装可能とする半導体装置を提供すること。

【解決手段】本発明の半導体装置は、シリコン基板1上に形成される保護層6と、前記保護層6に形成され、前記シリコン基板1に形成される半導体素子と電気的に接続するCu配線層9と、前記Cu配線層9を被覆し、前記保護層6上に形成される樹脂膜10と、前記樹脂膜10に形成される開口領域11を介して前記Cu配線層9と接続するパッド電極12と、前記パッド電極12上にワイヤボンディングされるCuワイヤ14とを有し、前記Cuワイヤ14と前記Cu配線層9との間には合金層13が配置されることを特徴とする。

(もっと読む)

ダイシングされた集積回路における破壊の抑制

【課題】低誘電率誘電体を使用するICの歩留り損失及び初期故障を抑止する。

【解決手段】半導体デバイスは基板210及びダイ縁部を有する個片化されたダイ110を備える。相互接続誘電体層220a、220b、220c、220dが基板上に配置され、集積回路がその相互接続誘電体層内に配置された相互接続部230を有する。トレンチ250が、相互接続誘電体層内で、かつシール・リング270と相互接続誘電体層の残部との間に配置される。シール・リングは、相互接続誘電体層内で、かつトレンチと集積回路の間に配置され、相互接続誘電体層の残部はトレンチとダイの縁部との間に配置される。

(もっと読む)

半導体装置及びその製造方法

【課題】エロージョンの発生及び研磨残渣の発生がない金属からなる配線又はプラグを形成できるようにする。

【解決手段】半導体基板1上の層間絶縁膜3にコンタクトホール3aを形成する。続いて、層間絶縁膜3上に金属を含む化合物及び第1の還元性ガスを供給することにより、コンタクトホール3aを含む層間絶縁膜3の上に第1のシード層5を形成する。続いて、第1のシード層5上に金属を含む化合物及び第2の還元性ガスを供給することにより、第1のシード層5の上に第2のシード層6を形成する。続いて、第2のシード層6の上に、金属をコンタクトホール3aを埋め込むように形成する。続いて、CMP法により、層間絶縁膜3のコンタクトホール3aを除く上面に残存する金属、第2のシード層6及び第1のシード層5を除去することにより、コンタクトホール3aにプラグ7Aを形成する。

(もっと読む)

半導体装置

【課題】下層導電層の表面を十分保護することができ、信頼性が高く、配線容量が小さなデュアルダマシン配線を有する半導体装置の製造方法を提供する。

【解決手段】導電性領域11を有する下地と10、下地の表面を覆う絶縁性エッチストッパ膜12と、絶縁性エッチストッパ膜上に形成された層間絶縁膜と、層間絶縁膜表面から第1の深さで形成された配線用溝と、配線用溝底面から導電性領域に達する接続用孔と、配線用溝および接続用孔を埋め込んで形成されたデュアルダマシン配線である。層間絶縁膜が配線用溝の側面および底面を包む第1種の絶縁層15と、第1種の絶縁層よりも下に配置され、第1種の絶縁層とエッチング特性の異なる第2種の絶縁層56とを含む。接続用孔は、断面で見た時に第1種の絶縁層内で傾斜し、上方に向かって次第に開口が増大する部分を有する。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの微細化が進展しても、広いキャパシタ面積を確保し、容量を増大させることが可能なキャパシタを備える、半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、基板111と、基板上に、第1の電極材で形成された複数の第1の電極層と、第1の電極材と異なる第2の電極材で形成された複数の第2の電極層とが、キャパシタ絶縁膜を介して交互に積層されたキャパシタ102と、第1及び第2の電極層の側方に形成されており、第1の電極層と電気的に接続され、第2の電極層と電気的に絶縁されている、1つ以上の第1のコンタクトプラグ171Aと、第1及び第2の電極層の側方に形成されており、第2の電極層と電気的に接続され、第1の電極層と電気的に絶縁されている、1つ以上の第2のコンタクトプラグ171Bとを備える。

(もっと読む)

101 - 120 / 694

[ Back to top ]