Fターム[5F033RR15]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 不純物を含むもの (1,419) | BPSG (694)

Fターム[5F033RR15]に分類される特許

681 - 694 / 694

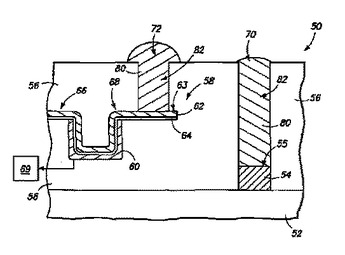

電気的接続部を形成する半導体処理方法及び半導体構造

無電解メッキを利用して、半導体基板に関連する電気的相互接続部を形成することができる。例えば、半導体基板は、その上に無電解メッキに適する表面を持つダミー構造を有するように、且つその上にダミー構造とほぼ同じ高さを有するディジット線を有するように形成することができる。層はダミー構造及びディジット線上に形成され、開口はその層を通ってダミー構造及びディジット線の上部表面まで形成される。続いて、導電性材料が開口内に無電解メッキされて、開口内に電気的接続部を形成することができる。ダミー構造まで延びる開口はキャパシタ電極を通ることができ、したがって、そのような開口内に形成される導電性材料を利用して、キャパシタ電極への電気的接続部を形成することができる。  (もっと読む)

(もっと読む)

メモリセル形成のためのインサイチュ表面処理

有機メモリセルの製造中などに実施されうるものなど、導電層上にパッシブ層を形成するためのシステムおよび方法が開示され、これは、一般に、従来の無機メモリデバイスに固有の不具合を低減させる。パッシブ層は硫化銅(Cu2S)などの導電促進化合物を含み、これは、導電材料の上部から形成される。この導電材料はメモリセルにおいて下部電極として作用し、導電材料の上部が、フッ素(F)系ガスから生成されたプラズマによる処理によってパッシブ層に変換されうる。  (もっと読む)

(もっと読む)

高度に選択的な酸化ケイ素エッチング組成物

少なくとも一種のカルボン酸からなる溶媒中に溶解した少なくとも一種の酸性フッ化物供給源化合物の生成物を含有し、更に約(0.5)〜約(3)溶液重量%のフッ化水素酸と約(1)〜約(5)溶液重量%の水とを含む酸化ケイ素エッチング溶液であって、ここで酸性フッ化物供給源化合物の総濃度は、溶媒1キログラム当たり約(1.25)〜約(5.0)モルである、前記酸化ケイ素エッチング溶液。金属表面から酸化ケイ素と金属のケイ酸塩とを選択的に除去する方法も開示する。 (もっと読む)

アモルファス炭素膜のCVD堆積用の液体前駆体

アモルファス炭素材料を堆積するための方法が提供される。一態様では、本発明は、処理チャンバに基板を位置決めするステップと、該処理チャンバに処理ガスを導入するステップであって、該処理ガスがキャリアガス、水素および1つ以上の前駆体化合物を含むステップと、二重周波数RF源から電力を印加することによって該処理ガスのプラズマを生成するステップと、該基板上にアモルファス炭素層を堆積するステップとを含む基板処理方法を提供する。 (もっと読む)

強誘電体キャパシタデバイスおよびFeRAMデバイス

1つ以上のコンタクトプラグが通過して延びている基板と、上記基板上に形成された第1の層間絶縁膜とから、強誘電体キャパシタデバイス(例えばFeRAMデバイス)が形成されている。上記第1の層間絶縁膜上にはスペーサ層が形成されていて、このスペーサ層上には第1の酸素バリア層が形成されていて、この第1の酸素バリア層上にはバッファ層が形成されている。上記バッファ層上において、上記バッファ層と上記コンタクトプラグとの間に下地材料の層が形成されていて、第1の電極と第2の電極との間に誘電体層が挟まれている。上記デバイスに第2の酸素バリア層が塗布される。上記スペーサ層があれば、上記下地材料と上記コンタクトプラグとの界面まで酸化が及ぶことが抑制される。なぜなら、上記界面が、上記第1の酸素バリア層の下に位置しているからである。この結果、電気コンタクトが破損することはない。  (もっと読む)

(もっと読む)

半導体デバイスにおける造形部分のパターン形成技術

【課題】 パターン形成される造形部分の微小寸法を縮小する技術を提供すること。

【解決手段】 半導体の処理のための技術が提供される。1つの態様において、半導体デバイスに1つまたはそれ以上の造形部分をパターン形成するための方法は、以下のステップを含む。反射防止材のエッチング中に、1つまたはそれ以上の造形部分の少なくとも1つの微小寸法が縮小される。リソグラフィ構造もまた提供される。

(もっと読む)

無定形炭素層を含むマスキング構造

多数層を有するマスキング構造が形成される。そのマスキング構造は、無定形炭素層と該無定形炭素層上に形成されたキャップ層とを含む。無定形炭素層は透明無定形炭素を含む。キャップ層は非酸化物材料を含む。マスキング構造は、半導体装置の製作中、エッチング・プロセスにおけるマスクとして使用可能である。 (もっと読む)

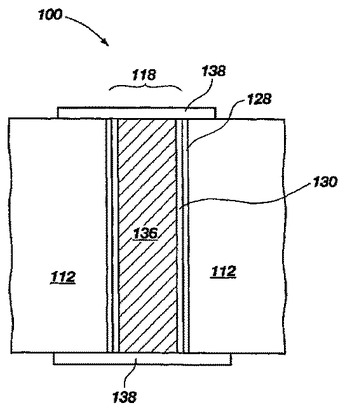

導電性構成部品、貫通ビア及び導電性貫通ウェーハ・ビアを含む半導体構成部品を製造するためのプロセス及び集積化スキーム

半導体構成部品に導電性ビアを形成するための方法が開示される。この方法は、第1の表面及び反対側の第2の表面を有する基板112を設けるステップを含む。この基板に、第1の表面と反対側の第2の表面の間に延びる少なくとも1つの穴118が形成される。基板のこの少なくとも1つの穴を画定している側壁にシード層128が形成され、導電層130でコーティングされ、この少なくとも1つの穴の内部の残りの空間に、導電性材料又は非導電性充てん材料136が導入される。基板を貫通した導電性ビアを、ブラインド・ホールを使用して形成する方法も開示される。本発明の導電性ビアを含む基板を有する半導体構成部品及び電子システムも開示される。  (もっと読む)

(もっと読む)

半導体装置、半導体装置の製造方法及びプラズマCVD用ガス

本発明は、420℃以下の熱履歴を経たフッ素添加カーボン膜からなる絶縁膜を備えた半導体装置に関する。本発明の特徴は、前記フッ素添加カーボン膜中の水素原子の含有量が、前記熱履歴を経る前において、3原子%以下であることにある。 (もっと読む)

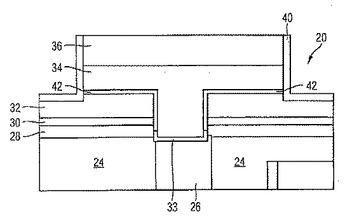

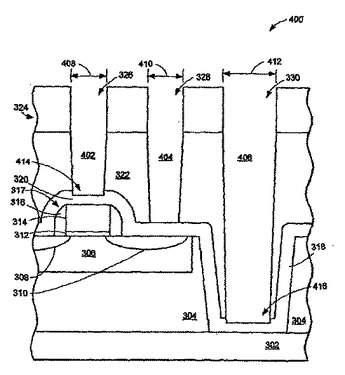

集積回路におけるコンタクトサイズをサイジングすることによって多層コンタクトを製造するための方法

集積回路を形成するための方法(600)は、第1半導体基板(202)上の半導体デバイス(317)表面上の誘電材(322)における第1深さに第1開口部(228)、(338)、(402)をエッチングし、第1半導体基板(202)表面上の誘電材(322)において第2深さに第2開口部(230)、(340)、(404)をエッチングする。第1開口部(228)、(338)、(402)、及び第2開口部(230)、(340)、(404)は、エッチングラグに起因してほぼ同時に第1及び第2深さにエッチングするためにそれぞれ異なってサイズされる。第1開口部(228)、(338)、(402)、及び第2開口部(230)、(340)、(404)は、導電材で充填される。  (もっと読む)

(もっと読む)

集積回路技術における超均一シリサイド

集積回路(100)の形成方法(900)およびその構造体が提供される。半導体基板(102)上にゲート誘電体(104)が形成され、半導体基板(102)上のゲート誘電体(104)上にゲート(106)が形成される。半導体基板(102)にソース/ドレイン接合部(504/506)が形成される。ソース/ドレイン接合部(504/506)上に超均一シリサイド(604/608)が形成され、半導体基板(102)の上方に誘電体層(702)が堆積される。次いで、誘電体層(702)に、超均一シリサイド(604/608/606)へのコンタクトが形成される。  (もっと読む)

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッドの下層におけるクラックの発生を抑制しつつ、ボンディングパッドの下層を有効活用して装置の小型化を図る。

【解決手段】半導体装置10は、半導体基板11と、外部との電気的接続をとるための接続領域12aを有するボンディングパッド12と、半導体基板11とボンディングパッド12との間に介在する第1層間絶縁層13と、第1層間絶縁層13に埋設されたメタル配線層14とを備える。メタル配線層14は第1層間絶縁層13より硬度の小さい材質からなる。メタル配線層14の少なくとも一部は、積層方向において接続領域12aと重なり、接続領域12aと重なるメタル配線層14の領域には、積層方向に貫通し、メタル配線層14をその層方向において分離している切欠部30a〜30eが形成されているとともに、この切欠部30a〜30eに第1層間絶縁層13の一部が埋め込まれている。

(もっと読む)

半導体集積回路装置の製造方法

【課題】 アルミニウムを主成分とする導体膜パターンを有する半導体集積回路装置の信頼性を向上させる。

【解決手段】 アルミニウムを主成分とする導体膜16dを有する第1層配線L1をドライエッチング法によってパターニングした後、その加工側壁の側壁保護膜18およびエッチングマスクとして使用したフォトレジストパターン17aをプラズマアッシング処理によって除去する。続いて、絶縁膜15bおよび第1層配線L1の表面に付着した塩素成分を、酸素ガスとメタノールガスとの混合ガスを用いたプラズマアッシング処理によって除去する。この際、フォトレジストパターン17a等のアッシング除去処理時は、ウエハの主面温度が相対的に低くなるようにし、塩素成分の除去処理時は、ウエハの主面温度が相対的に高くなるようにする。また、それらのプラズマアッシング処理を別々の処理室で行う。

(もっと読む)

多層配線構造

【課題】シールドによる配線容量の増加を抑え、シールド効果も補償できる多層配線構造を提供する。

【解決手段】半導体基板100上の酸化膜4上に所定の間隔で平行に配置された下層メタル配線3と、下層メタル配線3上の層間絶縁膜5上に下層メタル配線3と平行でかつ下層メタル配線3間に位置するように配置されたシールド用の配線メタル配線1と、メタル配線1上の層間絶縁膜6上に下層メタル配線3と重なるように配置された上層メタル配線2とから多層配線を構成し、シールド効果と同時に上層メタル配線2の全容量値の低減を図る。

(もっと読む)

681 - 694 / 694

[ Back to top ]