Fターム[5F033RR15]の内容

半導体集積回路装置の内部配線 (234,551) | 絶縁膜の材料 (22,565) | 無機材料 (16,592) | 不純物を含むもの (1,419) | BPSG (694)

Fターム[5F033RR15]に分類される特許

61 - 80 / 694

半導体装置の作製方法

【課題】簡単な工程で絶縁膜、半導体膜、導電膜等の膜パターンを有する基板を作製する方法、さらには、低コストで、スループットや歩留まりの高い半導体装置の作製方法を提供することを目的とする。

【解決手段】基板上に形成された絶縁膜、半導体膜又は導電膜上に接して第1の膜を形成する工程と、第1の膜上に第1のマスク材料を含有する溶液を吐出して第1の膜上に第1のマスクを形成する工程と、第1のマスクを用いて第1の膜をパターニングして絶縁膜、半導体膜又は導電膜表面上に塗れ性の低い領域と塗れ性の高い領域を形成する工程と、第1のマスクを除去する工程と、塗れ性の低い領域に挟まれた塗れ性の高い領域に、第2のマスク材料を含有する溶液を吐出して第2のマスクを形成する工程と、第2のマスクを用いて、パターニングされた第1の膜をエッチングするとともに絶縁膜、半導体膜又は導電膜をエッチングする。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の金属配線の平坦化を行う場合、金属配線を下地層に形成した溝に埋め込むと、金属配線の配置をするとき、その変更工程が困難になるという問題があった。また、金属配線に寄生容量がついてしまい、電気信号の遅延などが発生してしまうという問題があった。

【解決手段】本発明の半導体装置の構造は、金属配線下の下地層である絶縁膜を加工して突起部を設ける。この突起部と所定の距離だけ離間して金属配線を設ける。この突起部により、平坦化のための研磨工程でも、不測の余剰研磨が発生しない。また、突起部と金属配線とが離間することにより、金属配線の配置の変更を容易に行うことができると共に、金属配線の寄生容量を低減できる。

(もっと読む)

半導体装置の製造方法

【課題】メタルゲートプロセスにおけるプリメタル層間絶縁膜の平坦性を向上できるようにする。

【解決手段】まず、半導体基板1の上に、ゲート絶縁膜3を介在させてゲート電極4を形成する。その後、半導体基板1にゲート電極4をマスクとしてソース・ドレイン領域を形成する。続いて、ゲート電極4を覆うように半導体基板1上の全面に第1の酸化シリコン膜10を形成する。その後、ゲート電極4をストップ膜とするCMP法により、第1の酸化シリコン膜10を平坦化する。続いて、ゲート電極4を含む第1の酸化シリコン膜10の上に、第2の酸化シリコン膜11を形成する。その後、ゲート電極4をストップ膜とするCMP法により、第2の酸化シリコン膜10を平坦化する。さらに、ゲート電極4を含む第2の酸化シリコン膜10の上に、第3の酸化シリコン膜12を形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】コンタクト孔に埋め込まれる金属プラグの材料が層間絶縁膜に染み出すのを防止できる半導体装置を提供する。

【解決手段】隣り合う2つのメモリセル1のサイドウォール間の不純物拡散領域に電気的接続されるコンタクトプラグ40が、層間絶縁膜18を貫通して設けられている。コンタクト孔41の側壁は、層間絶縁膜18より緻密なシール膜42で覆われている。コンタクトプラグ40は、シール膜42の表面およびコンタクト孔41の底面部を覆うように形成されたバリアメタル膜43と、バリアメタル膜43に包囲された状態でコンタクト孔41内に埋め込まれた金属プラグ44とを含む。

(もっと読む)

トレンチゲートMISデバイスの構造及び製造方法

【課題】より単純に製造でき、かつ平坦なトポロジを得ることができ、更にトレンチの上部曲がり部における降伏電圧の問題が解消されたトレンチゲートMISデバイスを提供すること。

【解決手段】トランジスタセルを含む活性領域と、トランジスタセルを含まないゲート金属領域と、ゲート金属層とを含み、半導体チップの表面のパターンに、活性領域からゲート金属領域に至るトレンチが形成されており、このトレンチが絶縁材料の層で裏打ちされた壁部を有し、導電性ゲート材料がトレンチ内に設けられており、導電性ゲート材料の上面が半導体チップの上面より下側に位置し、非導電層が活性領域及びゲート金属領域の上に位置し、ゲート金属領域におけるトレンチの一部の上側の非導電層に開口が形成されており、ゲート金属がトレンチ内の接触領域のゲート材料と接触するように、開口が前記ゲート金属で満たされているトレンチゲートMISデバイス。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置の製造方法において、ヒューズ層を覆う絶縁膜の膜厚を精度良く調整する。

【解決手段】半導体基板10上の第2の層間絶縁膜17上にヒューズ層18Tが形成され、ヒューズ層18Tは第3の層間絶縁膜20で覆われる。第3の層間絶縁膜20上には、キャップメタル24に覆われたパッド電極23が形成され、それらは第1及び第2のパッシベーション膜25,26に覆われる。次に、ヒューズ層18T上で開口する第1のレジスト層27をマスクとして、ヒューズ層18T上で第2のパッシベーション膜26から第3の絶縁膜の厚さ方向の途中までをエッチングする。その後、パッド電極23上で開口する第2のレジスト層30をマスクとして、パッド電極23上で第1及び第2のパッシベーション膜25,26及びキャップメタル層24をエッチングしてパッド電極23の表面を露出する。その後、保護膜32を形成する。

(もっと読む)

エッチング方法、エッチングシステムおよびエッチング装置

【課題】シリコン酸化膜にコンタクト部に到達する高アスペクト比のホールを形成する際に、ホール内のコンタクト材料とコンタクト部との間で十分なコンタクトがとれるようなホールを形成すること。

【解決手段】基板上にBおよびPの少なくとも一方を含むシリコン酸化物からなる第1の酸化膜と、その上に形成された、BおよびPを含まないシリコン酸化物からなる第2の酸化膜とを有し、さらに第1の酸化膜および第2の酸化膜の界面より下方に形成されたコンタクト部を有する被処理体を準備し(ステップ1)、第2の酸化膜と前記第1の酸化膜をエッチングしてコンタクト部に到達するホールを形成し(ステップ2)、HFガスおよび不活性ガスを用いたドライプロセスにより第1の酸化膜をエッチングし、第1の酸化膜のコンタクト部上方領域のホール部分を広げる(ステップ3)。

(もっと読む)

半導体装置及びその製造方法

【課題】トリミング素子からのトリミング時の気化ガスの圧力によりトリミング素子の下部の層間絶縁膜にクラックが入るのを防止する。

【解決手段】層間絶縁膜2上にトリミング素子Tを形成する。トリミング素子Tの上を層間絶縁膜3aで被覆する。トリミング素子Tの斜め上方領域の層間絶縁膜3a上にクラック誘導体Gを形成する。トリミング素子T及びクラック誘導体Gはレーザー光の照射領域に配置される。レーザー光を照射すると、トリミング素子Tの周辺及びクラック誘導体Gの周辺の層間絶縁膜3a等に重畳して広く延在する高温領域6が形成され、該高温化した層間絶縁膜3a等の剛性が低下する。その結果、トリミング素子Tの上辺のコーナー部に気化ガスの圧力がかかりやすくなり、トリミング素子Tの下辺のコーナー部にかかる気化ガスの圧力が小さくなるので、トリミング素子Tの下側の層間絶縁膜2のクラック5発生を防止できる。

(もっと読む)

半導体装置

【課題】コンタクト抵抗の上昇を防止することが可能な半導体装置を提供すること。

【解決手段】シリコン基板に形成される複数の拡散領域と、複数の拡散領域にボトム部が接続して形成される複数のコンタクトプラグ33と、ボトム部を含んでシリコン基板上に形成されるアモルファスカーボン膜24とを備え、ボトム部はアモルファスカーボン膜24を貫通して拡散領域に接合される。アモルファスカーボン層24をコンタクトプラグ33形成時のエッチングストッパ層として用いることで、拡散領域がオーバーエッチングによりダメージを受けることが防止される。

(もっと読む)

半導体装置及びその製造方法

【課題】ダイシング等で半導体装置を個片化する際に加工のダメージ又は膜の残留応力などに起因して発生する、基板上の膜の剥離を抑制することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置101,102の周辺すなわち個片化のための加工ラインの近傍の基板1上に溝6を形成する。その溝の内部では基板上に成膜される薄膜が少なくとも1部で不連続となることにより、万一、半導体装置の端部から膜剥がれが発生したとしても、この溝部でその進行を阻止する。

(もっと読む)

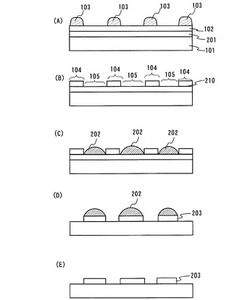

パターン付基板の作製方法、及び半導体装置の作製方法

【課題】隣接する膜パターンの間隔を制御することが可能なパターン付基板の作製方法を

提供する。また、膜パターンの幅の制御が可能で、特に、幅が細く且つ厚みのあるパター

ン付基板の作製方法を提供する。また、アンテナのインダクタンスのバラツキが少なく、

起電力の高い導電膜を有する基板の作製方法を提供することを課題とする。また、歩留ま

り高く半導体装置を作製する方法を提供することを課題とする。

【解決手段】基板、絶縁膜又は導電膜上に珪素及び酸素が結合し且つ前記珪素に不活性な

基が結合する膜を形成した後、珪素及び酸素が結合し且つ前記珪素に不活性な基が結合す

る膜表面に印刷法を用いて組成物を印刷し、組成物を焼成して膜パターンを形成すること

を特徴とする。

(もっと読む)

半導体装置の製造方法

【課題】ゲート電極に形成された研磨後のキャップ絶縁膜の厚さを容易に推定できる半導体装置の製造方法を提供する。

【解決手段】半導体装置形成領域に第1の導電膜よりなるゲート電極15、半導体装置非形成領域に絶縁膜形成部16、及び絶縁膜よりなり、ゲート電極の上面及び絶縁膜形成部の上面を覆うキャップ絶縁膜17を形成し、次いで、キャップ絶縁膜を覆う層間絶縁膜28を形成し、次いで、キャップ絶縁膜上に形成された層間絶縁膜にゲート電極の延在方向と交差する方向に延在する溝47を形成すると共に、溝の下方に位置する層間絶縁膜に不純物拡散層を露出するコンタクトホール22,23を形成し、次いで、溝及びコンタクトホールを埋め込む第2の導電膜51を形成し、次いで、CMP法により第2の導電膜を研磨することでコンタクトプラグを形成し、その後、絶縁膜形成部に形成されたキャップ絶縁膜の厚さを測定する。

(もっと読む)

半導体装置の製造方法

【課題】ビット線材料埋設体の形状のばらつきに起因するビット線の配線抵抗値のばらつきを防ぐ半導体装置の製造方法を提供する。

【解決手段】製造方法は、第一溝4内に第一のビット線材料埋設体6および第二のビット線材料埋設体10からなるビット線11を形成する第一工程と、ビット線11に含まれる不純物を拡散させて第一不純物拡散領域13を形成する第二工程と、ピラー部1bを形成する第三工程と、ピラー部1bに対向する配線17を第二溝15内に形成する第四工程と、ピラー部1bの先端部に、第二不純物拡散領域19を形成する第五工程と、を具備し、第一工程が、第一溝4を完全に埋め込むように第一ビット線材料を形成した後に第一ビット線材料表面を平坦化し、第一溝4底部に残るように第一ビット線材料をエッチバックする工程を具備する。

(もっと読む)

半導体集積回路及びその製造方法

【課題】金属層からなるガードリングで囲まれたトリミング素子形成領域のヒューズ上の保護膜の開口からヒューズ上の層間絶縁膜に浸入した水分等がガードリングに形成されたヒューズ引き出し電極用の開口を通ってデバイス形成領域に浸入することを防止する。

【解決手段】ヒューズ5aを取り囲む第1ガードリング30とその外側の第2ガードリング40に囲まれたヒューズ電極引き出し領域41を形成する。ヒューズ5aと連続し層間絶縁膜6とフィールド酸化膜4の間をヒューズ電極引き出し領域41まで延在するヒューズ電極5と、該ヒューズ電極5と接続する第1ヒューズ引き出し電極7cと、該第1ヒューズ引き出し電極7cと接続する第2ヒューズ引き出し電極9cとを形成し、該第2ヒューズ引き出し電極9cを層間絶縁膜8上に形成された第2ガードリング40を構成する第2電極の開口24を通してデバイス素子形成領域80に引き出す。

(もっと読む)

半導体装置の製造方法

【課題】安定した形状の信頼性の高いエアギャップを効率良く形成する半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法では、半導体基板上に、ビアホール及びエアギャップ用トレンチを含む複数のホールを有する層間絶縁膜を形成する。次に、エアギャップ用トレンチ内に有機材料を埋め込んだ後、硬化させる。また、ビアホール内にビアプラグを形成する。この後、エアギャップ用トレンチ内に埋め込まれた有機材料を除去することにより、エアギャップを形成する。

(もっと読む)

半導体装置及びその製造方法

【課題】どのようなレイアウトの配線に対しても、個々の配線ごとにエアギャップ部を設ける。エアギャップ部によって、配線の寄生容量を低減する。

【解決手段】半導体装置は、層間絶縁膜と、層間絶縁膜内に埋め込まれた配線と、配線の側面と層間絶縁膜との間に設けられたエアギャップ部と、を有する。半導体装置の製造方法は、配線の側面上に第2のサイドウォール膜を形成した後、第2のサイドウォール膜の一部が露出するように第1の絶縁膜を形成する。次に、第2のサイドウォール膜を除去することによりサイドスペースを形成した後、サイドスペースが埋め込まれないように第2の絶縁膜を形成することによりサイドスペースから構成されるエアギャップ部を形成する。

(もっと読む)

固体撮像素子とその製造方法

【課題】配線やコンタクトホールの寸法の微細化に際しても、コンタクト抵抗の低減を図ることが可能であり、且つ、暗電流の発生が少ない固体撮像素子およびその製造方法を提供する。

【解決手段】固体撮像素子1では、配線24と転送電極膜102とが、2層のコンタクトホールにより接続されている。下側のコンタクトホールAは、その底部にチタンシリサイド膜105が形成されている。そして、上側のコンタクトホールBは、チタンシリサイドを構成中に含まず、下側のコンタクトホールとの間が中間配線層としてのタングステン膜107により接続されている。ここで、上下の両コンタクトホールA,Bには、純粋なチタンは残っていない。また、撮像画素領域におけるフォトダイオード121の上方の層内レンズ膜127は、下方のコンタクトホールAに対して積層上方に選択的に形成されている。

(もっと読む)

半導体ウエハとその製造方法、及び半導体チップ

【課題】半導体チップ領域内へのクラック伝播を抑制でき新規な構造を持つ金属リングを有する半導体ウエハを提供する。

【解決手段】半導体ウエハは、半導体素子が形成された第1半導体チップ領域と、半導体素子が形成された第2半導体チップ領域と、第1半導体チップ領域と第2半導体チップ領域との間に挟まれたスクライブ領域とを有し、第1半導体チップ領域は、第1半導体チップ領域に形成された半導体素子を囲む金属リングを含み、金属リングは、下側金属層と下側金属層上に重なる上側金属層とを含む複数の金属層で形成され、上側金属層の第1半導体チップ領域外側の側面が、下側金属層の外側の側面と揃っているか、または、下側金属層の外側の側面に対して第1半導体チップ領域内側に位置しているように、下側金属層上に上側金属層が重なっている。

(もっと読む)

半導体装置の製造方法

【課題】本発明は、簡素な製造工程でありながら、ボイドを発生させずにトランジスタセルの高密度化を実現する半導体装置の製造方法を提供することを目的とする。

【解決手段】半導体層60にトレンチ型のゲート90が形成され、該ゲート90の両側に拡散層50が形成されたトランジスタセルを複数含むセル部61と、該セル部61を囲むガードリング部62とを有する半導体装置の製造方法であって、

前記ゲート90及び前記拡散層50が形成された前記半導体層60の表面に、層間絶縁膜120を形成する工程と、

前記セル部61に形成された前記層間絶縁膜120を、エッチバックにより薄膜化する工程と、

前記層間絶縁膜120の前記拡散層50上の位置に、孔状又は溝状のコンタクト部130を形成する工程と、

前記層間絶縁膜120上に、金属膜140を形成する工程と、を含むことを特徴とする。

(もっと読む)

半導体デバイス及びその製造方法

本願は、半導体デバイス及びその製造方法に関するものである。本発明の半導体デバイスの製造方法は、半導体基板を提供する工程と、半導体基板に、該半導体基板に形成されたゲート絶縁層及び該ゲート絶縁層に形成された犠牲ゲートを含むゲート領域と、ソース/ドレイン領域とを含むトランジスタ構造を形成する工程と、第1の層間絶縁層を堆積し、犠牲ゲートを露出させるように該第1の層間絶縁層に対して平坦化を行う工程と、犠牲ゲートを除去して、リプレースメントゲートホールを形成する工程と、第1の層間絶縁層におけるソース/ドレイン領域に対応する位置に、第1のコンタクトホールを形成する工程と、第1のコンタクトホール及びリプレースメントゲートホールに第1の導電材料を充填して、ソース/ドレイン領域に接触する第1のコンタクト部と、リプレースメントゲートとを形成する工程とを含む。本発明によれば、リプレースメントゲートと第1のコンタクト部は、同一の工程で同じ材料を堆積して形成することができるため、製造プロセスを簡単化できた。  (もっと読む)

(もっと読む)

61 - 80 / 694

[ Back to top ]