Fターム[5F033UU03]の内容

半導体集積回路装置の内部配線 (234,551) | レイアウト、シミュレーション (1,514) | 配線の設計、レイアウト (1,445) | 同一層のみのもの (292)

Fターム[5F033UU03]に分類される特許

281 - 292 / 292

半導体集積回路装置

【課題】 半導体集積回路装置の設計中あるいは設計完了後の論理変更を容易とする。

【解決手段】 所定の回路が形成された主領域と、主領域に形成された回路の論理変更に用いる予備素子領域とを有する。予備素子領域は、Pチャンネルトランジスタ領域111〜113と、Nチャンネルトランジスタ領域121〜123と、Pチャンネルトランジスタ領域上及びNチャンネルトランジスタ領域上に設けられた複数のゲート電極131〜134、141〜144と、ゲート電極よりも上層の配線層に形成されたバイパス配線151〜155と、バイパス配線よりも上層に位置する主配線層とを備える。バイパス配線151〜155は、いずれも主配線層とバイパス配線とを分離する絶縁層に形成されたコンタクトホールによって、少なくとも2箇所で主配線層と接続可能に構成されている。

(もっと読む)

半導体装置

【課題】 配線層に接続するメタルヒューズを容易に形成することができると共に、溶断後のメタルヒューズの溶断面が露出するようなことがなく、その溶断面露出に起因したヒューズの酸化を防止することができるヒューズ信頼性の高い半導体装置を得ることにある。

【解決手段】 隣り合うメタルヒューズ3,4を有し、その一方のメタルヒューズ3が溶断された複数の配線層1a,1b、2a,2bを備える半導体装置において、前記メタルヒューズ3,4で接続すべき配線層1a,1b間および2a,2b間に跨って配置され、当該配線層間のヒューズ形成領域の両側にバリアメタル7a,7b、8a,8bを有する電極パッド5,6と、前記バリアメタル7a,7b間および8a,8b間に埋め込まれた埋め込み膜9と、この埋め込み膜9によって前記バリアメタル7a,7b間および8a,8b間のヒューズ形成領域で前記埋め込み膜9に形成された空洞10とを備え、この空洞内10にメタルヒューズ3,4を埋め込み形成したものである。

(もっと読む)

半導体装置

【課題】 多層配線構造において、層間の密着性を良好にする。

【解決手段】 半導体装置100には、半導体基板(不図示)上に、配線124が形成された第一の層間絶縁膜120と、ビア126が形成された第二の層間絶縁膜122とを含む多層配線構造が形成されている。半導体装置100は、配線124およびビア126が形成された回路領域110と、回路領域110を隔離するシールリングが形成されたシールリング領域112と、シールリング領域112の外周に形成された外周領域114とを含む。外周領域114において、第二の層間絶縁膜122中に、金属材料により構成されたダミービア136が形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】 ボイドの発生の有無を短時間で且つ容易に確認できる半導体装置及びその製造方法を提供する。

【解決手段】 本発明に係る半導体装置の製造方法は、絶縁膜上に複数の配線パターン1〜4を形成する工程と、前記絶縁膜及び前記複数の配線パターンの上に層間絶縁膜を形成する工程と、前記層間絶縁膜上に該層間絶縁膜とは異なる物質(例えばW)からなる物質層を堆積する工程と、前記複数の配線パターンのうち隣り合う配線2,3間の容量を測定する工程と、前記容量が所定値より小さい場合は、前記隣り合う配線間に位置する該層間絶縁膜の少なくとも一部にボイドが形成されていると判断し、前記容量が所定値以上の場合は、前記隣り合う配線間に位置する該層間絶縁膜にボイドが形成されていないと判断する工程とを具備する。

(もっと読む)

半導体装置及びその設計方法

【課題】 半導体集積回路において、端子電極の後に積層され、素子の平坦化を担う金属層により、端子電極間のクロストークが生じる。

【解決手段】 回路素子の近接配置される端子電極20〜24に対応して、平坦化金属層に電極領域タイル30〜34を生成する。当該タイルは、たかだか1つの端子電極にしか重ならないように定められる。当該タイル30〜34とパターンルールによって他のタイルが排除される排他領域とからなる電極領域レイアウト70が得られる。この電極領域レイアウト70に、標準タイル72が二次元的に配列されたパターンを合成する。標準タイル72は、電極領域レイアウト72以外の部分に選択的に合成され、2つの端子電極に跨って配置されることが防止される。

(もっと読む)

積層型半導体装置

【課題】 複数の半導体チップを積層するともに、半導体チップを貫通して設けられる貫通配線を用いて半導体チップ間の電気的接続を確立する積層型半導体装置において、貫通配線の不良に起因した歩留まり低下を抑制する。

【解決手段】 半導体チップ204、213をそれぞれ貫通する貫通配線205、209を有する積層型半導体装置において、貫通配線205、209に対して平行配置された予備貫通配線206、210を設け、スイッチ回路203、207、211を用いて、信号の伝達経路を貫通配線と予備貫通配線との間で切り替えることができるようにする。

(もっと読む)

電気光学装置の製造方法、電気光学装置、及び電子機器

【課題】 良好な素子特性を有する非線形素子を備え、もって高画質表示を可能にした電気光学装置を歩留まりよく製造する方法を提供する。

【解決手段】 基板上に、第1導電層と絶縁層と第2導電層とを積層してなる非線形素子と、該非線形素子から延出されたコンタクト部と、前記非線形素子およびコンタクト部を覆う層間絶縁膜と、前記コンタクト部と電気的に接続された画素電極とを具備した電気光学装置の製造方法であって、本線部106bとコンタクト部36を迂回する支線部106aとを有する金属膜106をパターン形成する工程と、前記金属膜106を陽極酸化処理することにより前記金属膜106上に酸化膜からなる絶縁層を形成する工程と、前記支線部106aの先端部を残して前記金属膜106を除去し、前記第1導電層および導電層を形成する工程と、前記絶縁層上に前記第2導電層およびコンタクト部36を形成する工程とを含む製造方法とした。

(もっと読む)

接触抵抗が低減された半導体デバイス

【課題】パワー半導体デバイスの電気抵抗を小さくする。

【解決手段】 第1の導電性の材料から構成され、表面に電極を有する半導体ダイと、前記第1の導電性の材料の抵抗率よりも低い抵抗率を有する第2の材料から構成され、前記電極の上に設けられた導電性本体とを備える半導体デバイスと、第1の導電性の材料から構成された、半導体デバイスの電極の表面にバリア層を形成するステップと、前記第1の材料の電気抵抗率よりも電気抵抗率が低い第2の導電性の材料から構成されたシード層を、前記バリア層の上に形成するステップと、前記第2の材料から構成された前記シード層の上に導電製本体を形成するステップとを有する、半導体デバイスを製造するための方法に関する。

(もっと読む)

金属メッシュ構造を含む半導体集積回路

集積回路に使用する金属メッシュ構造が説明される。一実施形態では、半導体集積回路は、例えば1つまたは複数の能動半導体デバイスを有するデバイス層を含む第1領域を備える。回路は回路配線を含む金属化層含むことがある第2領域も備える。回路は更に第1領域と第2領域の間に挿入された金属メッシュ層を含み、金属メッシュ層は、別の金属化層の少なくとも一部分の上に実装されることがある。  (もっと読む)

(もっと読む)

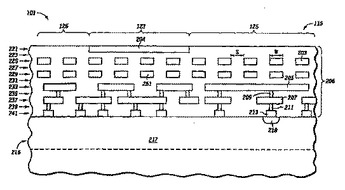

半導体の整合補助部

半導体デバイス用の整合補助部(115)に関する。整合補助部は、高い反射度を有する領域(123)と、低い反射度を有する隣接領域(125)とを備える。低い反射度を有する領域には、半導体デバイスの相互接続層(225)に配置され、かつ半導体デバイスの能動回路(218)の上方に配置されている、1層以上のタイル(203)が含まれる。一部の例では、整合補助部のタイルの走査方向への間隔は、整合補助部の走査に使用される光(例えば、レーザ光)の波長より短い。他の例では、整合補助部のタイルの走査方向への幅が、整合補助部の走査に使用される光の波長より短い。  (もっと読む)

(もっと読む)

信号バス配置

【課題】 バスのピッチ幅を広くすることなく信号線間のクロストークノイズを低減する。

【解決手段】 2次元レイアウトにおいて、隣接信号線BUS_A<0:L>およびBUS_B<0:M>は、異なるバスに属するする信号線となるようにバス信号線を配置する。異なるバスは、それぞれ異なるタイミングで変化する信号を伝達し、同一バス内の信号線は実質的に同一タイミングで変化する信号を伝達する。

(もっと読む)

基板ノイズの分配方法

ノイズ分配器を導入することによってノイズの抑制が得られる差動集積回路または平衡集積回路を備えた大きな抵抗率の基板の中において、ノイズ分配のための方法が開示される。典型的には2個の集積されたトランジスタA、Bまたはトランジスタの群によって形成される差動集積回路または平衡集積回路に隣接して小さな抵抗率の経路を生成することにより、外部のノイズ・ソース5からのノイズが差動集積回路または平衡集積回路の分岐に関して等方的にされる。通常の場合には小さな抵抗率の経路は集積されたトランジスタに関して対称的に作成され、それによりノイズを均等に分配するノイズ分配器が形成される。この時、ノイズ分配器は基板またはウエルと同じ種類の不純物が添加された浮動基板接触体10として作成される。この基板またはウエルの中に、差動回路または平衡回路が備えられる。さらに、ノイズを分配する小さな抵抗率の経路の構造をシミュレーションすることによって、ノイズ分配器の形状が最適化されるであろう。ノイズを分配する小さな抵抗率の経路の構造体は、小さな抵抗率の経路が維持される限り、連続である必要はない。 (もっと読む)

281 - 292 / 292

[ Back to top ]