Fターム[5F033UU03]の内容

半導体集積回路装置の内部配線 (234,551) | レイアウト、シミュレーション (1,514) | 配線の設計、レイアウト (1,445) | 同一層のみのもの (292)

Fターム[5F033UU03]に分類される特許

81 - 100 / 292

半導体装置、下層配線設計装置、下層配線設計方法およびコンピュータプログラム

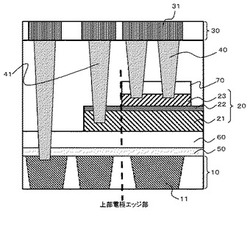

【課題】MIMキャパシタの構造破壊に起因するリーク電流の上昇を低減する構成を備えた半導体装置を提供することを課題とする。

【解決手段】複数の下層配線11を備える下層配線層10と、下層配線層10の上方に設けられる、下部電極21と容量誘電膜22と平面形状が下部電極21より小さい上部電極23とを下からこの順に積層したMIMキャパシタ20と、MIMキャパシタ20の上方に設けられ、ビア40、41を介して下部電極21および上部電極23のそれぞれに接続する複数の上層配線31を備える上層配線層30と、を備えた半導体装置であって、上部電極23の平面形状は矩形に構成され、上部電極23の平面のいずれか一以上の辺であるエッジ部の直下には下層配線11が配置されていない半導体装置を提供する。

(もっと読む)

配線設計方法および配線設計装置

【課題】対向する金属配線を有する配線構造において特性の安定化や性能の向上を図ると共に高耐圧化を実現する。

【解決手段】配線設計装置は、対向する金属配線間に与えられる最大の電位差をVmaxとしたときに配線間距離dminを与える関係式Vmax=A×ln(dmin/d0)+B(A,Bは定数、d0は基準となる距離)を予め記憶する記憶部1と、金属配線間の距離を、想定される最大電位差Vmaxに対してVmax=A×ln(dmin/d0)+Bにより得られる配線間距離dmin以上として設定する設計部2とを備える。

(もっと読む)

ダミーパターンの配置方法及びダミーパターンを備えた半導体装置

【課題】従来よりも簡単にダミーパターンを配置し、スクライブ領域に隣接した半導体チップの形成領域において、層間絶縁膜が薄くなるのを抑制する方法を提供する。

【解決手段】配線層を備えた半導体チップの形成領域と、該形成領域を囲むスクライブ領域とを備えた半導体チップにおいて前記配線層と同じ層からなるダミーパターンを配置する方法であって、前記配線層から少なくとも所定距離だけ離間する位置に第1のダミーパターンを設定する段階と、前記スクライブ領域に隣接する所定幅の範囲内において、前記配線層から少なくとも所定距離だけ離間しかつ前記第1のダミーパターンから少なくとも所定距離だけ離間する位置に第2のダミーパターンを設定する段階と、を備えたダミーパターンの配置方法を提供することによって、上記課題を解決できる。

(もっと読む)

離間された導電配線に電気的接続を提供する方法

集積回路及び形成方法は、少なくとも1つの直線的に延在する導電配線の斜端に形成されたコンタクト領域を提供する。実施形態では、コンタクトランディングパッドを有する導電配線は、マスク材料に配線をパターン化することと、材料配線の延在方向に対して角度を形成するために少なくとも1つの材料配線を切断することと、マスク材料の斜端面から拡張部を形成することと、前記材料配線及び拡張部をマスクとして用いてエッチングすることによって基本的な半導体をパターン化することとによって形成される。他の実施形態では、少なくとも1つの導電配線は、斜端面を作るように導電配線の延在方向に対して角度を付けて切断されるとともに、電気的コンタクトランディングパッドは、斜端面にコンタクトして形成される。 (もっと読む)

電気接点の製造方法

【課題】 端子の先端に、水平方向に突出する突起を所望の形状で形成できる電気接点の製造方法を提供すること。

【解決手段】 母材を、電気接点20Aの形状にパターニングされたマスク30で覆ってエッチング液で母材の不要な部分を除去することにより、電気接点20Aを形成する。電気接点20Aの先端24の第1の突起24a及び第2の突起24bは、マスクの先端34に設けた突起形成部31a,31bにより形成されるが、突起形成部31a,31bの形状を突起の形状及び形成領域のL/S(ラインアンドスペース)の比率に応じて調整することにより、前記第1の突起24a及び第2の突起24bを所望の形状で形成することが可能となる。

(もっと読む)

半導体装置の製造方法

【課題】半導体装置内の埋め込みコンタクトホールを簡略な工程で形成するための半導体装置の製造方法を提供する。

【解決手段】シリコン基板101上に1又は複数の半導体素子が作り込まれてなる半導体装置に埋め込みコンタクトを形成するにあたり、半導体素子層の全面に層間絶縁膜109を形成する(第1工程)。次いで、半導体装置内のシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bからなる2つの領域が露出するように層間絶縁膜にコンタクトホール109aを形成する(第2工程)。そして、コンタクトホールから露出しているシリコン106、107、ポリシリコン104A、104B、又は金属シリサイド108A,108Bの表面に無電解めっき法により選択的に金属膜111を形成する(第3工程)。

(もっと読む)

半導体集積回路設計装置および半導体集積回路設計方法

【課題】タイミングマージンの厳しい信号のメタル配線における膜厚変動を抑制することのできる半導体集積回路設計装置および半導体集積回路設計方法を提供する。

【解決手段】半導体集積回路設計装置1は、指定信号メタルパターン抽出部11が、指定された信号名のメタルパターンを記憶装置1000に格納されたレイアウトデータから抽出し、メタルパターン周囲領域設定部12が、指定信号メタルパターン抽出部11により抽出されたメタルパターンの周囲に所定の領域を設定し、メタル被覆率評価部13が、メタルパターン周囲領域設定部12により設定された周囲領域のメタル被覆率を算出して、そのメタル被覆率が所定値以上あるかどうかを評価し、メタル被覆率が所定値未満と評価されたときは、ダミーメタル挿入部14が、上述の周囲領域にダミーメタルを挿入する。

(もっと読む)

半導体装置及びその製造方法

【課題】連続した耐湿リングを備える半導体装置を製造すること。

【解決手段】直線状に延びる第1延伸部パターン21apと第1延伸部パターン21apと直交する方向に延びる垂直部パターン22pとを有するマスクP1と、直線状に延びる第2延伸部パターン22bpを有するマスクP1'とを用いて、耐湿リング20の溝形状のビアパターンを露光する半導体装置の製造方法であって、第1マスクP1又は第2マスクP1'の何れか一方を用いて、耐湿リング20の溝形状のビアパターンを露光し、次に、他方のマスクを用いて、耐湿リング20の溝形状のビアパターンを露光し、垂直部パターン22pによって露光された部分22mと、第2延伸部パターン21bpによって露光された部分21bmとが直交し且つ第1延伸部パターン21apによって露光された部分21amと、第2延伸部パターン21bpによって露光された部分21bmとが離間するように露光する。

(もっと読む)

半導体装置

【課題】半導体デバイスに対する多様な要求に対し、柔軟に対応することができる半導体デバイスを提供する。

【解決手段】基板(2)と、ゲート絶縁膜(6)を介して基板(2)の上に設けられるゲート電極(3)と、ゲート電極(3)に隣接して配置されるサイドウォール(5)とを具備する半導体装置(1)を構成する。ゲート電極(3)は、引き出し電極部分(3−2)と実効ゲート電極部分(3−1)とを備えることが好ましい。また、引き出し電極部分(3−2)は、第1方向に沿って延伸する素子分離(9)の上に形成され、第1方向に沿った第1側面(16)(17)を有する部分とする。実効ゲート電極部分(3−1)は、素子分離(9)で分離される領域の上に形成され、第1側面(16)(17)を含む面に交差する面に沿った第2側面を有する部分とする。サイドウォール(5)は、第1側面(16)(17)を覆うことなく第2側面を覆うものとする。

(もっと読む)

半導体装置

【課題】低電圧化による誤動作を抑制した半導体装置を提供する。

【解決手段】複数のメモリセルと、センスアンプと、外部と電気的に接続するための複数のパッドを含む、1または複数のパッド列とを有し、パッド列は、パッド列の端部およびパッド列の内部に配置された、センスアンプに接地電位を供給するための複数のセンスアンプ接地用パッドと、少なくとも信号を入力するための信号用パッドとを含み、センスアンプ接地用パッドと信号用パッドの間に、信号用パッドを除く、他の種類のパッドが少なくとも1つ配置されている構成である。

(もっと読む)

半導体装置およびその製造方法

【課題】

厚い配線を形成すると、絶縁膜との間に剥離が生じやすい。

【解決手段】

半導体装置は、複数の半導体素子を形成した半導体基板と、半導体基板上方において、半導体基板表面とほぼ平行な第1レベルに延在する第1の配線パターンであって、異なるレベルの配線またはパッドとの接続領域を含む平面形状を有し、第1の厚さを有する主配線領域と主配線領域の側壁から1つ以上の段差を形成して外側に張り出し、第1の厚さより薄い第2の厚さを有し、主配線領域から連続する張り出し配線領域とを有する第1の配線パターンと、第1の配線パターンを囲む第1の絶縁領域と、を有する。

(もっと読む)

二回のカット工程によって多結晶シリコンのライン端部短縮の問題を解決する方法

【課題】ゲートストリップを二回のカット工程によって端部を改善する製造方法の提供。

【解決手段】第1アクティブ領域40と、第2アクティブ領域42とを有する基板を提供するステップと、基板にゲート電極層を形成するステップと、第1ゲートストリップ60と、第1ゲートストリップに実質的に平行する第2ゲートストリップ62と、第1アクティブ領域と第2アクティブ領域の間に位置して、第1ゲートストリップと第2ゲートストリップに平行していないが、互いに接続する犠牲ストリップ66とを残すように、ゲート電極層をエッチングするステップと、第1ゲートストリップと第2ゲートストリップの一部を覆い、犠牲ストリップ及び第1ゲートストリップと第2ゲートストリップの一部を開口部に露出させる遮蔽部を形成するステップと、開口部に露出される犠牲ストリップ及び第1ゲートストリップと第2ゲートストリップの一部をエッチングするステップを含む。

(もっと読む)

半導体素子及び半導体素子のパターン形成方法

【課題】多様な幅を有するパターンを同時に形成しつつ、一部領域ではダブルパターニング技術によりパターン密度を倍加させる半導体素子のパターン形成工程及び該工程を容易に適用可能な構造の半導体素子を提供する。

【解決手段】半導体素子は、第1方向に相互平行に延びている複数のラインパターンを含む。複数のラインパターンのうちから選択される複数の第1ラインパターンは、第2方向に沿って交互に選択されて両側で各々隣接している2つのラインパターンの両端部のうち、素子領域の第1端部にさらに近い各端部に比べて、第1端部からさらに遠く位置する第1端部を有する。複数のラインパターンのうちから選択される複数の第2ラインパターンは、第2方向に沿って交互に選択され、両側で各々隣接している2つのラインパターンの両端部のうち、第1端部にさらに近い各端部より、第1端部からさらに近く位置する第2端部を有する。

(もっと読む)

パッシベーション層のクラックの発生を防止した集積回路の製造方法

【課題】パッシベーション層のクラックの発生を防止する。

【解決手段】エッチング及びダマシン法を用いて製造される集積回路においては、金属配線層から周囲の誘電体材料に応力が伝達されることによって、デバイスに組み込まれる配線層(400)の周囲の誘電体材料にクラックが発生することが一般的である。本発明は、周囲の誘電体層に伝達される応力を低減することができると考えられる丸められたコーナを有する配線層を形成することにより、この問題を解決する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】バンプの配列に疎密差があったときに発生する応力を緩和できる、半導体装置及び半導体装置の製造方法を提供する。

【解決手段】電極端子群を備える配線基板と、バンプ3群が形成されたバンプ形成面7を備え、バンプ3群が前記電極端子群と対向するように前記配線基板上に実装された半導体チップとを具備し、バンプ形成面7は、バンプ3が配置された領域の面積密度が第1密度である第1領域9と、バンプ3が配置された領域の面積密度が前記第1密度よりも小さい第2密度である第2領域10と、第1領域9と第2領域10との境界部分に設けられた第3領域11とを備え、第3領域11は、バンプ3が配置された領域の面積密度が、前記第2密度よりも大きく、前記第1密度よりも小さい。

(もっと読む)

リバースエンジニアリングを防ぐための導電性チャネル擬似ブロック処理方法及びその回路

【課題】リバースエンジニアリングに対して集積回路構造を偽装するための技術及び構造を提供する。

【解決手段】集積回路構造は、制御された外形を有する材料の複数の層により構成される。シリサイド金属層は、基板の活性領域において備えられ、活性領域に隣接して接続しているチャネル接続においてギャップを有する。そのチャネルはチャネルブロック構造を有し、チャネルブロック構造は、導電性又は絶縁性のどちらかであるように、リバースエンジニアリングにおいて識別可能であるようにみえる。

(もっと読む)

半導体装置およびその製造方法

【課題】 従来のエアギャップ構造より、さらに容量及び容量ばらつきを低減することができる。

【解決手段】 基板上の絶縁膜17上に、銅を主成分として含む配線26を形成する。それから、リザーバーパターン用絶縁膜21、22及びバリア絶縁膜29を形成し、配線26の上面および側面上と絶縁膜17及び絶縁膜29上に銅の拡散を抑制または防止する機能を有する絶縁膜31を形成する。このとき、狭い配線間スペース底部の絶縁膜17の膜厚保は、配線26上の絶縁膜31の膜厚より、薄く成膜することで細線ピッチの配線容量を効率良く低減する。その後、低誘電率からなる絶縁膜36及び絶縁膜37を成膜する。その際、配線26の隣接配線間において、対向する配線側面の上方での堆積速度が下方での堆積速度より大きくなるように絶縁膜36を形成し、エアギャップを形成する。最後に、層間CMPによって、絶縁膜37を平坦化する。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】繋ぎ露光において、マスクパターンの一端部を幅広に形成したマスクを使用しなくても、マスクの相対的な位置ずれに伴う配線抵抗の増大や配線信頼性の低下などの電気的な特性劣化を抑制する。

【解決手段】本発明の半導体装置は、半導体基板上で隣り合う第1の露光領域及び第2の露光領域のうち、第1の露光領域に第1の露光マスクを用いて形成された第1配線パターン101と、第1配線パターン101と繋ぎ合わせるための配線パターンとして、第1配線パターン101と同層でかつ第2の露光領域に第2の露光マスクを用いて形成された第2配線パターン102と、第1配線パターン101と第2配線パターン102との繋ぎ合わせ部分に形成されたビア103,104と、ビア103,104の間に形成された繋ぎパターン105とを備える。

(もっと読む)

半導体装置

【課題】製造バラツキに関わらず、切断箇所を制御できる構成の電気ヒューズを得る。

【解決手段】半導体装置200は、基板(不図示)上に形成された上層ヒューズ配線112、下層ヒューズ配線122、および上層ヒューズ配線112の一端と接続され、上層ヒューズ配線112と下層ヒューズ配線122とを接続するビア130から構成される電気ヒューズ100を含む。上層ヒューズ配線112には、一端側で配線幅が狭くなった幅変動領域118が設けられている。

(もっと読む)

半導体装置

【課題】ワード線の抵抗の低減及びワード線間容量の低減が可能な半導体装置を提供する。

【解決手段】ワード線3A及び3B方向に延在し、隣接する2つのセル列(L4n+1とL4n+2、L4n+3とL4n+4)を1本のワード線3A,3Bで接続することを特徴とする半導体装置50を採用する。

(もっと読む)

81 - 100 / 292

[ Back to top ]