Fターム[5F033UU03]の内容

半導体集積回路装置の内部配線 (234,551) | レイアウト、シミュレーション (1,514) | 配線の設計、レイアウト (1,445) | 同一層のみのもの (292)

Fターム[5F033UU03]に分類される特許

121 - 140 / 292

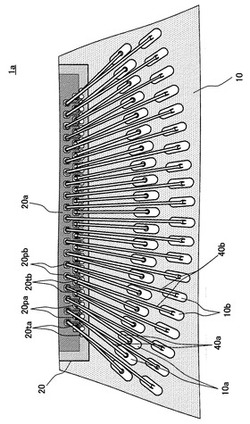

半導体装置

【課題】半導体装置の信頼性を向上させる。

【解決手段】列状に配置された複数の電極パッド20paと、電極パッド20paの夫々に電気的に接続され、電極パッド20paの列より外側に位置する、列状に配置された複数の試験パッド20taと、を有する半導体素子20と、半導体素子20を搭載し、半導体素子20の搭載領域以外に、複数の電極端子10aを列状に配置した配線基板10と、を備え、全ての試験パッド20taが、電極端子10aと電極パッド20taとを電気的に接続するボンディングワイヤ40aの下に位置している半導体装置が提供される。当該半導体装置1aによれば、ボンディングワイヤ40a自体の変形によってもたらされる、半導体素子20の電極パッド20pa,20pb間の短絡を解除し、半導体装置の製造歩留りを高め、より高い信頼性を有する半導体装置を提供することができる。

(もっと読む)

半導体装置

【課題】ダイシング時に半導体チップの側壁からのクラックが侵入するのを抑制することで信頼性向上を図る。

【解決手段】半導体チップ領域10の表面の端部上に、集積回路領域31を取り囲んでクラックストッパ用シールリング30が形成されている。クラックストッパ用シールリング30は、集積回路領域31の外の半導体基板11上に形成された積層構造体であり、第1ダミー金属層20、第2ダミー金属層21、第3ダミー金属層22が、それぞれ、第1層間絶縁膜12、第2層間絶縁膜14、第3層間絶縁膜16を間に挟んで積層されている。第1ダミー金属層20、第2ダミー金属層21、第3ダミー金属層22は、集積回路領域31の半導体素子や配線とは第1乃至第3の層間絶縁膜12,14,16によって電気的に絶縁されている。

(もっと読む)

クロック配線構造、半導体装置、及び半導体装置の製造方法

【課題】配線形状のばらつきを効果的に抑制することのできる配線構造、半導体装置、及び半導体装置の製造方法を提供すること

【解決手段】本発明にかかる配線構造は、クロック配線11と、クロック配線11と同層において、クロック配線11に沿ってその両側に設けられた一対の第1シールド配線12と、クロック配線11と絶縁層を介した異なる層において、クロック配線11及び一対の第1シールド配線12の対向する領域を覆うように設けられた第2シールド配線13と、一対の電極(上部電極17、下部電極18)が絶縁層を介して対向配置されたMIM容量30と、を備え、MIM容量30の一対の電極のうち少なくとも一方が、第2シールド配線13と同層に設けられているものである。

(もっと読む)

半導体装置の製造方法

【課題】全ての開口部の寸法誤差とばらつきを低減できると共に、マスク開口パターンの設計が容易で、製造コストの増大を抑制することができる半導体装置の製造方法を提供する。

【解決手段】非感光性ポリイミド樹脂からなる表面保護膜1に、異なる開口面積を有する複数の開口部21,22がウエットエッチングにより形成されてなる半導体装置200の製造方法であって、複数の開口部21,22を形成するためのマスク開口パターンをレイアウトするにあたって、複数の開口部21,22の中で最小の開口面積を有する最小開口部21より小さな開口面積を有する基準開口パターン21aを設定し、開口部21,22の外周に沿って、基準開口パターン21aの片側サイドエッチ量L21だけ内側に、該片側サイドエッチ量L21の2倍以下の間隔d1,d2をおいて、基準開口パターン21aをレイアウトする。

(もっと読む)

集積回路及びその製造方法

【課題】配線層の上に層間絶縁膜を堆積した集積回路において熱処理を施すと、配線間の狭い間隙部と、これにつながる広い開口部との接続部分にて、層間絶縁膜の破裂が起こり得る。

【解決手段】間隙部10と開口部12との接続部分に位置する配線4bの角部を面取りして、間隙部10の端部62を開口部12へ向けて末広がり形状とする。このようにパターニングした配線層の上に層間絶縁膜を堆積する。層間絶縁膜は間隙部10の狭い溝に起因して当該位置に空洞を形成し得る。端部62を設けることで、層間絶縁膜の堆積に関して、間隙部10と開口部12との接続部分での不連続性が緩和され、間隙部10の空洞の端が層間絶縁膜によって封止されにくくなり、熱処理での空洞の気圧上昇に伴う層間絶縁膜の破裂が抑制される。

(もっと読む)

半導体装置

【課題】層間絶縁膜としてLow−k膜を有する半導体装置において、温度サイクル試験時における層間絶縁膜の剥離を防止し、信頼性に優れた半導体装置を提供する。

【解決手段】銅を主導電層とする埋め込み配線5、8、11を内部に形成した層間絶縁膜4、7、10と、埋め込み配線5、8、11のキャップ絶縁膜6、9、12を積層した構造を備えた半導体装置において、相対的にヤング率の小さいLow−k膜からなる層間絶縁膜7と上面で接する相対的にヤング率の大きいキャップ絶縁膜6は、半導体装置の端部において、非設置となるように形成する。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置のサイズの増大を防止でき、コンタクト部を安定して形成できる。

【解決手段】N型電界効果トランジスタ12およびP型電界効果トランジスタ13が共有するゲート部11と、ゲート部11上に形成された、応力が異なる少なくとも2つの応力発生膜12a,13aと、応力発生膜12a,13aが重なる境界部16に形成された、ゲート部11の長手方向に沿った形状のコンタクト部14と、を有する半導体装置10により、半導体装置のサイズの増大が防止され、コンタクト部が安定して形成される。

(もっと読む)

半導体装置の設計方法、設計装置及びプログラム

【課題】適切な密度のダミーパターンを生成することができる半導体装置の設計方法、設計装置及びプログラムを提供することを課題とする。

【解決手段】半導体装置内において実パターンの隙間を埋めるように形成するダミーパターンの設計方法であって、半導体装置の全領域を一定の大きさに分割した領域から、全ての実パターンを一定量だけ拡大した領域を除去して得られる残存領域を求め、その残存領域において前記分割領域の各々を一定量だけ縮小してダミーパターンを生成するダミーパターン生成ステップと、前記ダミーパターンにおいて、密度条件を満たしていないダミーパターンがある場合は、前記ダミーパターン生成ステップにおける前記分割領域のすべて若しくは一部の縮小量、及び/又は前記実パターンの拡大量を変更して前記ダミーパターン生成ステップを繰り返す密度検証ステップとを有する半導体装置の設計方法が提供される。

(もっと読む)

半導体装置とその製造方法

【課題】接合性の低下をすることなく、パッド間の絶縁性を保つことができ、パッド周辺の保護膜のクラックも防止することができる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板と、前記半導体基板上に形成された層間絶縁膜1と、層間絶縁膜1上に形成されたメタル層5と、メタル層5と同じ層に形成された配線間絶縁膜2と、メタル層5および配線間絶縁膜2の上に形成され、メタル層5を露出する開口部を有する第1保護膜8と、前記開口部に露出したメタル層5と接続したパッドメタル7とを備え、パッドメタル7の周辺に対応した部分に、溝部11が形成されており、溝部11はパッドメタル7で覆われている。

(もっと読む)

半導体装置及びその製造方法

【課題】歩留まりの低下がなく、配線間容量を実用上十分に低減できる配線構造を有する半導体装置を得られるようにする。

【解決手段】半導体装置は、半導体基板100の上に形成された第1の層間絶縁膜101と、該第1の層間絶縁膜101に形成された複数の溝部に埋められた、導電性部材からなる複数の下部配線105とを有している。第1の層間絶縁膜101における複数の下部配線105の隣り合う配線同士の間には、第1の層間絶縁膜が除去されてなる空隙部101cが選択的に形成されている。また、空隙部101cの下端部の位置は、各下部配線105の下端部の位置よりも低い。

(もっと読む)

半導体装置

【課題】複数列のゲート電極を備える半導体装置におけるトランジスタ特性のばらつきを低減する。

【解決手段】半導体基板70の上部にゲート長方向に並んで複数列に設けられたゲート電極10と、複数列のゲート電極10と同層に設けられてこれらを互いに電気的に接続するゲート接続部30と、を備え、ゲート接続部30が、複数列のゲート電極10のうち最も端に位置するゲート電極10bよりもゲート長方向の外側に突出する突出部32を有することを特徴とする半導体装置100。

(もっと読む)

半導体装置及びその製造方法

【課題】 光アニールされる際の半導体基板の昇温時間を遅らせることなく温度ムラを低減することができ、回路性能の向上に寄与する。

【解決手段】 主波長が1.5μm以下の照射光による光アニール工程を経る半導体装置であって、半導体基板上に形成された、回路動作に関与する集積回路パターン21,22を有する回路パターン領域20と、基板上に回路パターン領域20と離間して形成され、集積回路パターンに用いられるゲートパターン21と同じ構造で回路動作に関与しないダミーゲートパターン31が主波長の0.4倍以下のピッチで周期的に配置されたダミーパターン領域30とを備えた。

(もっと読む)

半導体装置

【課題】電気ヒューズを切断する際のショートを防ぐことができる。

【解決手段】半導体装置100は、半導体基板(不図示)上に形成され、それぞれ異なる層に形成された第1の配線122と、第2の配線134と、第1の配線122と第2の配線134の間の層に設けられ、第2の配線134の一端部分に接続されるとともに第1の配線122に接続されたビア128とを含む電気ヒューズ200と、第2の配線134と同層に形成され、第2の配線134の一端部分の周囲を取り囲むように形成されたガード配線部160とを含む。平面視において、第2の配線134は、他端から一端部分の方向に延在して形成され、ガード配線部160は、第2の配線134の一端部分を中心として、当該一端部分の周囲三方を取り囲むように形成される。

(もっと読む)

半導体装置の製造方法

【課題】歩留りが高く、且つ、配線間容量を十分に低減できる構造を備えた半導体装置を提供する。

【解決手段】半導体装置の製造方法は、基板上に絶縁膜を形成する工程と、絶縁膜の内部に複数の配線溝を形成する工程と、複数の配線溝の内部に複数の配線を形成する工程と、絶縁膜及び複数の配線の上に、複数の配線間の領域のうち選択的に領域を露出する開口部を有するレジストマスクを形成する工程と、レジストマスクを用いたエッチングにより、複数の配線間の領域のうち選択的に露出した領域の絶縁膜を除去してエアギャップ溝を形成する工程と、レジストマスクを除去した後に、複数の配線上を覆うように層間絶縁膜を堆積することによってエアギャップを形成する工程とを含む。

(もっと読む)

配線構造の製造方法

【課題】低誘電率膜内に孤立ビアを形成する際に、レジストポイゾニングの発生を抑制する。

【解決手段】 基板1上に形成されたp−SiOC膜12内に、第1配線15と、第1ダミー配線15aを形成する。次に、p−SiOC膜22を形成し、p−SiOC膜22上にキャップ膜23を形成する。キャップ膜23及びp−SiOC膜22内に、第1配線15と接続するビア28と第2配線29とからなるデュアルダマシン配線を形成するとともに、孤立したビア28の周辺にダミービア28aを形成する。

(もっと読む)

レイアウト設計プログラム、該プログラムを記録した記録媒体、レイアウト設計装置、およびレイアウト設計方法

【課題】配線後の配線密度およびエッジ長の均一化を図ること。

【解決手段】配線のレイアウトを決定するときに、各部分領域の配線の配線密度およびエッジ長の最大値を制限する。さらに、配線のレイアウト後において、配線の配線密度が小さい部分領域にダミー配線を挿入することにより、各部分領域の配線の配線密度およびエッジ長の最小値を制限する。これにより、各部分領域の配線の配線密度およびエッジ長を一定の範囲内に抑え、研磨後の基板表面の凹凸差を低減させる。

(もっと読む)

ボンディングパッドを有する半導体装置及び同装置の製造方法

【課題】ボンディングパッドと半導体基板との間生じる浮遊容量の低減を図ることのできる半導体装置及び同装置の製造方法を提供する。

【解決手段】半導体基板上に複数の絶縁膜から形成される絶縁層を介して形成されたボンディングパッドを有する半導体装置の製造する際に、少なくとも一の絶縁膜形成工程後に、半導体基板の所定領域に形成する半導体素子の導電部と同一材料からなるダミーパッドを、前記導電部と同時に、ダミーパッドの幅よりも広い間隔を空けてドット状に形成し、このダミーパッド上に絶縁膜を形成した後、その絶縁膜を、ダミーパッドの厚み分まで平坦化してダミーパターン層を形成し、このダミーパターン層上に、絶縁膜を介してボンディングパッドを形成する。

(もっと読む)

半導体集積回路装置の製造方法

【課題】 製造プロセスへの付加を抑えコスト・TATを増大させることなくタイミング最適化が可能となる半導体集積回路装置の製造方法を提供することを目的とする。

【解決手段】 タイミング制約違反の有無を判定し、タイミング制約違反が検出された場合にこれを解消する為に信号やクロックの更なる遅延が必要な最適化対象配線333とこれに所定間隔以下で近接する隣接配線361の間(隣接配線間)の一部又は全部にボイド形成抑止領域381を設定し、ボイド形成抑止領域内の最適化対象配線と隣接配線の間(隣接配線間)に絶縁膜を形成し、ボイド形成抑止領域外の最適化対象配線と隣接配線の間(隣接配線間)にボイド371a,bを形成する。

(もっと読む)

半導体装置

【課題】高周波配線を含む半導体装置において、エロージョンやディッシングを効果的に防いで半導体装置を安定的に製造するとともに、高周波配線への周囲のダミーメタルからの影響を低減して特性を向上させる。

【解決手段】半導体装置100は、半導体基板上の多層配線層中に設けられた高周波配線102と、多層配線層中の半導体基板と高周波配線102が設けられた層との間の第2の配線層122bに設けられたダミーメタル104とを含む。ダミーメタル104は、平面視で、高周波配線102の外縁で囲まれる第1の領域106とその周囲の第2の領域108とを含む高周波配線近傍領域110と、それ以外の外部領域112とにそれぞれ分散配置され、高周波配線近傍領域110のダミーメタル104間の平均間隔が、外部領域112のダミーメタル104間の平均間隔よりも広い。

(もっと読む)

半導体装置

【課題】MOSトランジスタを有する半導体装置であって、エリアパッド下のMOSトランジスタの特性変動を抑制することが可能な半導体装置を提供する。

【解決手段】MOSトランジスタとエリアパッドを有する半導体装置10であって、結晶方位面<110>を表面とするシリコンを材料とする半導体チップ11と、ソース領域、ゲート領域及びドレイン領域がシリコンの結晶方位<110>の方向に並び、半導体チップ11内に形成される複数のMOSトランジスタ12と、半導体チップ11上のエリアパッドとして2次元状に形成された複数の接合用電極パッド13と、複数の接合用電極パッド13それぞれの上に形成された接合用バンプ14とを備え、複数の接合用電極パッド13は、その中心点が結晶方位<110>の方向に対して斜めの方向に並ぶことを特徴とする。

(もっと読む)

121 - 140 / 292

[ Back to top ]