Fターム[5F033UU03]の内容

半導体集積回路装置の内部配線 (234,551) | レイアウト、シミュレーション (1,514) | 配線の設計、レイアウト (1,445) | 同一層のみのもの (292)

Fターム[5F033UU03]に分類される特許

101 - 120 / 292

半導体装置

【課題】電源供給能力が高い半導体装置を提供する。

【解決手段】本発明の半導体装置1(100)は、機能回路21が形成された半導体基板2と、機能回路21の中央部Oの直上位置近傍を通る基幹配線33と、基幹配線33の端部に接続された電源パッド4と、機能回路21の略中央部と基幹配線33とを接続する接続配線34、5、6と、を備え、基幹配線33と電源パッド4とは同一層に形成される。このような構成により、半導体基板の機能回路の中央部近傍に効率良く電源供給を行うことができ、電源供給能力が高い。

(もっと読む)

ローカルインタコネクトを備えた半導体装置

【課題】ローカルインタコネクトを備えた半導体装置を提供する。

【解決手段】ローカルインタコネクトを備えた半導体装置であって、基板上に配置され、実質的に同一線上にある第1ゲート線構造と第2ゲート線構造、前記第1ゲート線構造の両側の前記基板に形成された第1対ソース/ドレイン領域と前記第2ゲート線構造の両側の前記基板に形成された第2対ソース/ドレイン領域、及び前記第1ゲート線構造と前記第2ゲート線構造の両側の前記基板上に配置され、それらが前記第1対ソース/ドレイン領域のうちの1つと前記第2対ソース/ドレイン領域のうちの1つに接続された一対の導電線を含む半導体装置。

(もっと読む)

有機電界発光表示装置の配線修理構造及びその修理方法

【課題】配線間のショート欠陥を容易に修理できるようにした有機電界発光表示装置の配線修理構造及びその修理方法を提供すること。

【解決手段】第1配線20及び第2配線40の間で発生したショート欠陥を修理する有機電界発光表示装置の配線修理構造において、第1配線20とのショート欠陥部分が切断されて切断された部分が残りの部分と断絶された第2配線40と、第2配線40と隣接するように配置され、ショート欠陥部分と隣接した一領域が切断されて切断された部分が残りの部分と断絶された第3配線50と、第2配線40が第3配線50の切断された部分を通じて電気的な連結状態を維持するように第2配線40の残りの部分と第3配線50の切断された部分を電気的に連結する第1リペアパターンRP1と、を備える。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】 Mnを含むバリア層を有するCu配線の高抵抗化を防止する半導体装置、および半導体装置の製造方法を提供する。

【解決手段】 半導体基板上方に形成された酸素を含有する絶縁層と、絶縁層中に形成された第1配線と、絶縁層中に形成され、第1配線と接続し、且つマンガン、酸素、及び銅からなる第2配線と、絶縁層内に形成され、第2配線と接続し、第1配線と離間して形成され、且つマンガン、酸素、及び銅によって埋め込まれた突起部と、を有し、突起部は、第2配線の下側に形成されており、突起部は、ビア形状および/または溝形状を有し、第2配線は、突起部よりも配線幅が太い。

(もっと読む)

膜厚予測方法、レイアウト設計方法、露光用マスクのマスクパターン設計方法、及び、半導体集積回路の作製方法

【課題】回路パターンの上に形成される薄膜の膜厚をより正確に予測し得る膜厚予測方法を提供する。

【解決手段】膜厚予測方法にあっては、第2の被処理層の断面形状に関する第1の実測データベース、回路パターンの周辺長と第2の被処理層の厚さとの関係に関する第2の実測データベース、第2の被処理層の平坦化レートに関する第3の実測データベース、第2の被処理層の基準膜厚Tblkを予め求めておき、基板の上に形成すべき第1の被処理層を所定の大きさの碁盤目状のメッシュに区切り、各メッシュ(i,j)におけるパターン面積率αij、回路パターンの周辺長Lij、第2の被処理層の初期厚さT2_INI_ij、基準膜厚Tblk、第1の実測データベース、第2の実測データベース及び第3の実測データベースに基づき、第2の被処理層の初期膜厚予測値Prij及び第2の被処理層の平坦化量Hijを求め、第2の被処理層を平坦化した後の第2の被処理層の膜厚を予測する。

(もっと読む)

配線パターン生成装置、配線パターン生成プログラム、半導体装置の製造方法、露光用マスク、および、画像表示装置

【課題】光学式欠陥検査に適した配線パターンを自動生成できるようにする。

【解決手段】配線パターンを自動生成に必要な情報を取得する情報取得手段4aと、前記情報取得手段4aが取得した各情報を基に、各パッド間を全て同角の配線で接続するために必要となる補正量を算出する補正量算出手段4cと、一方のパッド群における各パッドからは基準方向に対して同角で傾斜する配線が延び、他方のパッド群における各パッドからは前記補正量算出手段が算出した補正量の分だけ前記基準方向との直交方向に配線が延びるように、各パッド間を導通させる配線のレイアウトパターンを決定する配線処理手段4dと、を備えて配線パターン生成装置を構成する。

(もっと読む)

半導体記憶装置

【課題】不良解析の際に、メモリセルのレイアウトを制限したり、工程数を増加することなく、メモリセル数を数えやすくすること。

【解決手段】半導体基板2上にメモリセル3aの繰り返しパターンが形成されたメモリセルアレイ領域3を有し、メモリセルアレイ領域3上に形成された所定層の電源配線4a、接地配線4bを、少なくともメモリセルアレイ領域3において、メモリセル3aの配置と対応させて縦方向及び横方向に格子状にレイアウトしている。

(もっと読む)

半導体装置、半導体装置の製造方法および半導体パッケージの製造方法

【課題】半導体基板に形成されたダミーパターンを有するフィールド領域を有し、このフィールド領域をよぎる貫通電極が形成される半導体装置において、貫通電極の側壁に生じるノッチの発生を確実に防止することにより、品質および信頼性の安定性を図る。

【解決手段】

複数の能動素子が形成されているアクティブ領域と、アクティブ領域以外のフィールド領域とを有する半導体基板と、能動素子のいずれかに電気的に接続された少なくとも1つの電極パッドと、を含む。半導体基板の裏面からフィールド領域を経由して電極パッドに電気的に接続された少なくとも1つの貫通電極が形成される。フィールド領域は、半導体基板に絶縁膜を形成することにより得られる絶縁領域と絶縁領域内に半導体基板の基材を残すことにより得られるダミー部が設けられている。貫通電極の外縁が絶縁領域とダミー部との界面と交差しない位置にダミー部を設ける。

(もっと読む)

半導体装置およびその製造方法

【課題】TFTに接続された各配線を形成する際のプラズマエッチング工程においてチャージアップに起因するプラズマダメージが生じることを防止する。

【解決手段】TFT10のソース領域13sに接続されたソース配線17s、TFT10のドレイン領域13dに接続されたドレイン配線17d、およびTFT10に対して電気的に接続されない配線18を共通のプラズマエッチング工程によって形成する際、ソース配線17sとドレイン配線17dとの間隔を、ソース配線17sと配線18との間隔およびドレイン配線17dと配線18との間隔よりも狭くする。

(もっと読む)

半導体装置

【課題】細幅配線間のTDDB寿命の低下、および細幅配線間のショートによる歩留まり低下を抑制する半導体装置を提供する。

【解決手段】半導体装置10は、ダマシン配線からなる配線層を有し、0.5μm以上の幅を有する第1の配線12と、前記第1の配線12に隣接し前記第1の配線12から0.5μm未満の間隔で配置された第2の配線14と、前記第2の配線14に隣接し前記第1の配線12から0.5μm以下の間隔で配置された第3の配線16と、を備え、前記第2および第3の配線は同電位を有するよう構成されている。

(もっと読む)

相互接続構造(改善された耐エレクトロマイグレーション特性を有する集積回路のための相互接続構造)

【課題】 集積回路(IC)デバイスのための相互接続構造を提供する。

【解決手段】 集積回路(IC)デバイスのための相互接続構造は、第1の幅w1で形成された1つ以上のセグメント及び1つ以上の追加の幅W2・・・wNで形成された1つ以上のセグメントを有する細長い導電性ラインを備え、第1の幅は前記1つ以上の追加の幅のそれぞれよりも狭く、1つ以上の追加の幅で形成された1つ以上の導電性セグメントの全長L2・・・LNに対する第1の幅で形成された1つ以上の導電性セグメントの全長L1の関係は、導電性ラインの全長L=L1+L2+・・・LNが臨界長さに関係なく最小の所望の設計長さを満足するように、導電性ラインに流れる電流の所定の大きさに対して、エレクトロマイグレーション・ショート・レングス効果の利点が維持されるように選択される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】実用上十分な動作速度およびエレクトロマイグレーション耐性を有する半導体装置を製造する。

【解決手段】半導体基板の上面に層間絶縁膜101が形成されており、層間絶縁膜101内に下層配線105が形成されている。層間絶縁膜101の上面および下層配線105の上面にはライナー絶縁膜106が形成されており、ライナー絶縁膜106の上面には層間絶縁膜108が形成されている。層間絶縁膜108内に上層配線113が形成されており、下層配線105と上層配線113とはビア109を介して接続されている。そして、ビア周辺領域140に形成されたライナー絶縁膜106の膜厚は、ビア周辺領域140の外側に形成されたライナー絶縁膜106の膜厚よりも厚い。

(もっと読む)

回路構造とそれを定義するためのフォトマスク

【課題】フォトマスクパターンがOPCによって従来技術よりも更に容易に補正できるラインとピックアップパッドとを含む回路構造およびそのフォトマスクを提供する。

【解決手段】回路構造とそれを定義するフォトマスクを提供する。回路構造が複数のピックアップパッド320と平行な複数のライン310とを含み、連続的に配列されたラインの一部にそれぞれ1つのピックアップパッドが配置される。1つのピックアップパッドを配置された任意のラインのピックアップパッドが、ラインの一側において隣接するラインの不連続点330を通過して、次のラインに接続される。フォトマスクが上記ラインを定義する複数のラインパターンと前記ピックアップパッドを定義する複数のピックアップパッド定義パターンとを有する。

(もっと読む)

半導体装置、通信モジュールおよび電子機器

【課題】安定した利得が得られるアンテナ素子を備えた半導体装置、通信モジュールおよび電子機器を提供すること。

【解決手段】半導体装置10は、能動素子が形成された能動面1aを有する半導体基板1と、能動面1a上に少なくとも1層以上の絶縁性樹脂層を介して設けられた第1の配線層8と、第1の配線層8に形成されたスロットアンテナ11と、スロットアンテナ11に接続された共振用キャパシタ13とを備え、スロットアンテナ11は、矩形状の開口部11bを有する平面型のアンテナ素子である。

(もっと読む)

半導体装置及び検査方法

【課題】半導体装置のワイヤ流れによる不具合の発生を防止することが可能な技術を提供すること。

【解決手段】本発明の一態様に係る半導体装置10は、半導体チップ11に設けられた回路ブロック12と、回路ブロック12上に設けられた接続パッド15(1br)と、接続パッド15(1br)と電気的に接続され、ボンディングされるボンディングパッド17(1)とを備え、回路ブロック12は、接続パッド15(1br)を介してボンディングパッド17(1)と接続される。

(もっと読む)

半導体装置

【課題】回路パターンの形状のばらつきを抑制しつつ、半導体装置を小型化することができる半導体装置を提供する。

【解決手段】この半導体装置10は、複数の回路パターン140及び第1のダミーパターン142を備える。複数の回路パターン140は、互いに等間隔で配置され、回路の一部として使用される。複数の回路パターン140は、最も外側に位置する2つの回路パターン140bと、他の回路パターン140aに分けられる。第1のダミーパターン142は、2つの回路パターン140bそれぞれの外側に配置されている。回路パターン140bと第1のダミーパターン142の間隔は、回路パターン140の配置間隔Sに等しい。そして、第1のダミーパターン142の幅W2はいずれの回路パターン140の幅W1より狭く、例えば最小デザインルールで規定されている幅である。

(もっと読む)

半導体装置

【課題】製造工程時間の増加を招くことなく、複数の凹部に埋め込まれた部材表面の平坦性を向上することのできる技術を提供する。

【解決手段】相対的に面積の大きい第1ダミーパターンDP1と相対的に面積の小さい第2ダミーパターンDP2とをダミー領域FAに配置することによって、素子形成領域DAとダミー領域FAとの境界BL近くまでダミーパターンを配置することができる。これにより、分離溝内に埋め込まれた酸化シリコン膜の表面の平坦性をダミー領域FAの全域において向上することができる。さらに、ダミー領域FAのうち相対的に広い領域を上記第1ダミーパターンDP1で占めることで、マスクのデータ量の増加を抑えることができる。

(もっと読む)

半導体素子の垂直チャネルトランジスタ及びその形成方法

【課題】ワードラインの抵抗が減少され、活性ピラー間の絶縁膜のエッチング過程における窒化膜損失が最小化される垂直チャネルトランジスタの形成方法及びそのトランジスタを備えた半導体素子を提供すること。

【解決手段】基板上に、活性ピラーの各々の下部を取り囲んでいるゲート電極(805)を備える前記活性ピラーを形成するステップと、前記活性ピラー間のギャップ領域を埋め込むように第1絶縁膜(807A)を前記活性ピラー上に形成するステップと、前記ゲート電極を全方向にわたって露出させ、前記ギャップ領域の底面は露出しないように、前記第1絶縁膜を部分的に取り除くステップと、残留する前記第1絶縁膜の上に前記ギャップ領域を埋め込むように導電膜を形成するステップと、前記ゲート電極を外周表面の全方向にわたって取り囲んで前記接続するワードラインを形成するために、前記導電膜をパターニングするステップと、を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置の信頼性を向上させる。

【解決手段】半導体素子11は、半導体素子11の主面に形成された電極パッド10と、半導体素子11の主面及び電極パッド10の周辺部を被覆することにより、電極パッド10表面に露出領域を画定するカバー層12と、カバー層12及び電極パッド10の露出領域を被覆するとともに、電極パッド10の中心を基準として点対称となる部位に、露出領域に到達し且つカバー層12を露出させる貫通孔13hを有する絶縁層13と、を備える。このような構成の半導体装置1によれば、半導体装置の信頼性が向上する。

(もっと読む)

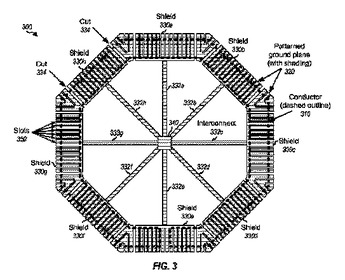

パターン化された接地平面を有するインダクタ

パターン化された接地平面を有するインダクタが、説明される。一設計においては、インダクタは、第1の層上に形成された導体と、その導体の下の第2の層上に形成されたパターン化された接地平面と、を含む。パターン化された接地平面は、オープンな中心エリアと、導体の形状に整合した形状と、を有する。パターン化された接地平面は、複数のシールド、例えば、八角形の形状の導体の8つの辺についての8つのシールド、を含んでいる。各シールドは、導体に垂直に形成された複数のスロットを有する。パターン化された接地平面を別個のシールドへと分割することと、各シールド上にスロットを形成することとは、パターン化された接地平面上の渦電流の流れを防止するのに役立ち、これは、インダクタのQを改善することができる。複数の相互接続は、複数のシールドを回路接地へと結合し、この回路接地は、導体の中心に位置することができる。  (もっと読む)

(もっと読む)

101 - 120 / 292

[ Back to top ]