Fターム[5F033UU03]の内容

半導体集積回路装置の内部配線 (234,551) | レイアウト、シミュレーション (1,514) | 配線の設計、レイアウト (1,445) | 同一層のみのもの (292)

Fターム[5F033UU03]に分類される特許

21 - 40 / 292

半導体装置

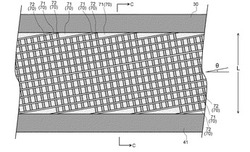

【課題】パワー半導体素子において、周辺の電界強度を緩和する構造を小さな面積で実現する。

【解決手段】周辺領域Qにおいては、半導体層との間に周辺層間絶縁層(絶縁層)を介して複数の多結晶シリコン層70が、ソース電極30から端部ドレイン電極41の間にかけて設けられる。多結晶シリコン層70には、その長手方向が水平方向から傾斜した(傾斜角θ、0<θ<90°)傾斜部が設けられている。多結晶シリコン層70の傾斜部においては、p型領域71と、n型領域72とが長手方向に交互に多数形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】トランジスタ間接続配線が吊りワード線と短絡してしまうのを回避すること。

【解決手段】第1の方向(X)に複数本並べて配置された活性領域(50)の各々は、第1の方向(X)と直交する第2の方向(Y)に離間して配置された2つの縦型トランジスタ(51)と、この2つの縦型トランジスタ(51)の間に位置するピラー(1a)と、から成る。半導体装置(100)は、複数本の活性領域(50)の中央の位置で、第1の方向(X)へ延在して配置された吊りワード線(23)と、2つの縦型トランジスタ(51)間を接続するために、第2の方向(Y)に延在し、かつ吊りワード線(23)を迂回するように構成されたトランジスタ間接続配線(21、10A、16)と、を備える。

(もっと読む)

半導体装置および基板

【課題】アライメントマークを用いて形成される半導体装置であり、ダイシングおよびクラックに起因する半導体チップの品質低下を抑制し、半導体チップの微細化を容易にすることが可能な構成を有する半導体装置および基板を提供する。

【解決手段】主表面を有する半導体基板と、半導体基板の一方の主表面上に形成された多層構造回路ICと、多層構造回路ICのうち最上層と同一の層に形成される、平面視において多層構造回路を取り囲むように配置される保護壁GRと、最上層と同一の層に形成される位置合わせマークM2Bとを備える。上記位置合わせマークM2Bは少なくとも一部において保護壁GRと接するように形成される。

(もっと読む)

回路のレイアウト装置,処理方法およびプログラム

【課題】 回路のレイアウト装置で,EOEの発生しやすい箇所を推定することを目的とする。

【解決手段】 回路レイアウト装置1は,被研磨対象となる回路の配線パターンを含む回路情報を取得する回路情報取得部11,回路を任意の単位領域でメッシュ状に区切り,各メッシュ領域について,メッシュ領域の配線密度とメッシュ領域の各辺に隣接する周辺領域の各々における配線密度とを示すメッシュ情報を生成するメッシュ情報生成部12,各メッシュ領域について,メッシュ領域と各周辺領域の密度の関係がEOEの発生条件に該当するメッシュ領域を抽出し,そのエラー情報を生成するエラー抽出部13を備える。

(もっと読む)

半導体装置

【課題】フリップチップ実装に用いられる半導体チップと実装基板との電気的な接続信頼性を向上させた半導体装置を提供する。

【解決手段】半導体チップ2と、半導体チップ2の主面に配置された複数の電極パッドと、複数の電極パッドの上に配置された複数のバンプ5とを有し、半導体チップ2のコーナー部において、第1のバンプと第2のバンプとが、第1のピッチで、隣接して配置され、半導体チップの中心部において、第3のバンプと第4のバンプとが、第2のピッチで、隣接して配置され、第1のピッチは、第2のピッチよりも狭い。

(もっと読む)

半導体集積回路及びそれを備えた半導体装置、並びに電子機器

【課題】半導体集積回路において、ダイシング時の保護膜の剥離を抑制しつつ保護膜の密着性を確保し、チップサイズの小型化を実現する。

【解決手段】半導体集積回路は、スクライブ領域2近傍に形成されたシールリング3と、パッド4と、シールリング3とパッド4との間に形成された配線5と、シールリング3と、ダミーパターン8と、保護膜6と、保護膜7とを備えている。保護膜7の終端縁9は、シールリング3とパッド4との間に位置しており、ダミーパターン8における配線5を挟んで互いに向かい合う部分の端部が、保護膜7の終端縁9を中心に半導体チップ1の周縁部側及び中央部側方向に5μmの間隔以内に位置している。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】電極パッド間におけるデンドライトの発生を抑制する。

【解決手段】半導体装置は、第1電極パッド1a及び第2電極パッド1bと、第1電極パッド1aと第2電極パッド1bとの間に配置されている金属膜パターン3と、を有している。(1)金属膜パターン3は第1電極パッド1aと電気的に接続されているか、又は、金属膜パターン3には第1電極パッド1aと同電位が印加され、且つ、(2)金属膜パターン3は絶縁膜(保護絶縁膜2)により覆われている。

(もっと読む)

半導体装置および半導体装置設計方法

【課題】半導体基板においてダミーパターンの配置密度を高める。

【解決手段】半導体基板104には、配線パターン102とダミーパターン106がレイアウトされる。配線パターン102の周囲にはマージン領域がレイアウトされ、マージン領域の周囲にダミー領域がレイアウトされる。このダミー領域に、複数のダミーパターン106がレイアウトされる。ダミーパターン106は、ダミー領域の延伸方向に配列される。マージン領域とダミー領域は、配線パターン102を基準として交互にレイアウトされる。

(もっと読む)

半導体素子の製造方法

【課題】 製造コストの低減が可能な半導体素子の製造方法を提供する。

【解決手段】 第1再配線層400は、金属バンプ層320の一部分を露出するように形成される。第1再配線層400は、第1拡張パッド部410、第1延長部420及び第1連結部430を備える。第1拡張パッド部410は、金属パッド120と電気的に接続し、外部装置と接続する。第1延長部420は、金属バンプ層320上から第1拡張パッド部410上に延びるように形成される。第1連結部430は、スクライブレーン領域SRに形成され、複数の第1再配線層400を電気的に連結する。第1再配線層400は、銀、ニッケルまたは銅を含むペーストまたはインクを利用したプリンティング方法、または、ロールオフセットプリンティング方法によって形成される。これにより、金属パッドと再配線層との接触抵抗を小さくするとともに、製造コストを低減することができる。

(もっと読む)

駆動装置、表示装置、駆動装置複合物及び集積回路装置

【課題】 小型かつ簡素な構成の駆動装置や、当該駆動装置を備える表示装置、複数の当該駆動装置から成る駆動装置複合物、当該駆動装置に備えられる集積回路装置を提供する。

【解決手段】 駆動装置1は、表示部に出力する出力信号を生成する集積回路部10と、集積回路部10と電気的に接続する配線部20と、を備える。集積回路部10は、出力信号を生成する複数の出力回路を備える。配線部20は、一端部が出力回路に電気的に接続する複数の出力配線24−1〜24−3と、出力配線24−1〜24−3の他端部に電気的に接続するとともに駆動装置1の外部に出力信号を出力する複数の出力部23−1〜23−3と、を備える。出力部23−1〜23−3は、所定方向(X方向)に沿って配置され、複数の出力部23−1〜23−3で出力部群G1〜G3が構成される。

(もっと読む)

半導体装置、表示装置および電子機器

【課題】特性の劣化を抑えつつ省スペース化を図ることが可能な半導体装置等を提供する。

【解決手段】半導体装置は、基板上の第1の方向に沿って延在し、互いに離隔配置された主配線部および分岐配線部を有する1または複数の第1の配線と、基板上の第1の方向とは異なる第2の方向に沿って延在する幹配線部と、主配線部と分岐配線部との間隙領域内で第1の方向に沿って延在する複数の枝配線部とを有する1または複数の第2の配線と、複数の枝配線部が個別にゲート電極として機能すると共に、主配線部内および分岐配線部内に形成されたソース領域と、複数の枝配線部間に形成されたドレイン領域とを有し、各々が第2の方向に沿って複数個に分割形成されてなる1または複数のトランジスタと、第2の方向に沿って延在し、トランジスタのドレイン領域と電気的に接続された1または複数の第3の配線とを備えている。

(もっと読む)

電気ヒューズ及びその製造方法

【課題】発熱体である抵抗から熱容量の大きいアノード領域への放熱を阻止し、ジュール熱を効率的に抵抗で消費するようにして、電気ヒューズの切断電力の低減化を図る。

【解決手段】絶縁膜5上にポリシリコン層6を形成し、該ポリシリコン層6上の一部に絶縁膜マスクを形成する。次に、該絶縁膜マスク層で被覆された以外のポリシリコン層6上にシリサイド層7を形成する。次にフォトエッチング工程を経てシリサイド層7、ポリシリコン層6をエッチングし、アノード領域1、カソード領域2及びアノード領域1とカソード領域2を接続するリンク領域3からなる電気ヒューズを形成する。電気ヒューズは、アノード領域1とリンク領域3の境界を挟んでリンク領域3方向からアノード領域1の一部に延在する非シリサイド領域を具備する。リンク領域3の非シリサイド領域は高抵抗領域11を構成し、アノード領域1の非シリサイド領域は熱伝導阻止層1bを構成する。

(もっと読む)

偏在率算出方法、半導体装置の製造方法及びプログラム

【課題】レイアウトデータからCu残が発生しやすい品種やレイヤであるか否かを判定することのできる偏在率算出方法を提供する。

【解決手段】CPUは、検証レイヤにおいて所定サイズの検証エリア毎にパターン密度を算出するステップS13と、算出されたパターン密度を複数の密度範囲に分別し、各々の密度範囲に属するパターン密度の分布を示す複数の密度マップMAP0〜MAP7を生成するステップS14とを実行する。また、CPUは、各密度マップMAP0〜MAP7に所定量のプラスシフトを加えるステップS15と、パターン密度の密度差が第1基準値以上となる組み合わせの密度マップMAP0〜MAP7を重ね合わせ、両密度マップで重複した領域を抽出するステップS16とを実行する。CPUは、その抽出した領域の総面積を算出するステップS17と、算出した総面積と第2基準値とを比較するステップS18とを実行する。

(もっと読む)

半導体装置

【課題】多層配線構造を有する半導体装置にダミーパタンを配線空隙に効率よく製造容易的に形成する。

【解決手段】多層配線構造の半導体装置において、狭い配線空隙(Area_S1)に、広い配線空隙(Area_S2)に形成されたダミーパタン(22,23)と異なる向きのダミーパタン(21)が形成されている。

(もっと読む)

設計支援プログラム、該プログラムを記録した記録媒体、設計支援方法、および設計支援装置

【課題】半導体集積回路の長寿命化、および設計期間の短縮を同時に実現すること。

【解決手段】設計支援装置700は、検出部701により、レイアウト情報によって表現された設計対象回路から配線間を接続するビアを検出する。つぎに、決定部702により、配線間を接続しないダミービアの接続位置を、検出部701によって検出されたビアに接続された配線のうち、少なくとも一つの配線上の位置に決定する。そして、挿入部704により、決定部702によって決定された接続位置にダミービアを挿入する。

(もっと読む)

発光装置の作製方法

【課題】微細な配線パターンを備えた発光装置の作製方法の提供。

【解決手段】Inと、Gaと、Znとを有する酸化物半導体層を形成し、酸化物半導体層上に第1の導体パターンを形成し、第1の導体パターンより微細な第2の導体パターンを形成し、前記第2の導体パターンと電気的に接続する発光素子を形成する発光装置の作製方法であって、第2の導体パターンは、酸化物半導体層を横断する。

(もっと読む)

電界効果型トランジスタ

【課題】駆動時の発熱温度を低下させる。

【解決手段】基板12の熱伝導率をNsub(W/mK)とし、熱拡散層14の熱伝導率をNkaku(W/mK)とし、熱拡散層14の膜厚をT(mm)とし、熱拡散層14の平面開口率をR(0≦R≦1)とし、S=T×Rとしたとき、例えば、基板12の熱伝導率Nsubが、Nsub<1.8の条件を満たし、熱拡散層14の熱伝導率Nkakuが、Nkaku>3.0×S^(−0.97×e^(−1.2×Nsub))且つNkaku≧Nsubの条件を満たす。

(もっと読む)

半導体装置

【課題】半導体装置におけるSM不良による信頼性や歩留りの低下を抑えることが可能な半導体装置を提供する。

【解決手段】半導体装置においては、第1の配線と、第1の配線と接続され、第1の配線より細幅の第2の配線と、一方の端部が、第1の配線と第2の配線の接続部の近傍で、第1の配線と接続され、他方の端部より局所的に細幅となる中間部を有する犠牲的配線と、を備える。

(もっと読む)

半導体装置

【課題】プロセス数を増大させることなく、応力を緩和できる構造を有する半導体装置を提供する。

【解決手段】一方の面に埋め込み酸化層と半導体層がこの順で積層される半導体基板10を加工して作製され、前記一方の面側で他の基板に接合される半導体装置であって、前記埋め込み酸化層及び前記半導体層を加工して形成される半導体素子20と、前記埋め込み酸化層及び前記半導体層を加工して形成され、前記半導体素子に接続される配線部と、前記配線部の端部に連続する前記半導体層によって構成され、当該半導体層の下側の埋め込み酸化層が除去されて前記半導体基板との間に空隙が形成されるパッド部40と、前記パッド部と前記他の基板を接合する接合部とを含む。

(もっと読む)

配線パターン及びその製造方法並びに半導体装置

【課題】配線パターンを覆う絶縁層をできる限り薄くする。

【解決手段】配線パターン1は、第一の一対の端子3,4及び該第一の一対の端子3,4間を接続する複数の第一の引き回し部5を有する第一の配線2と、第二の一対の端子7,8及び該第二の一対の端子7,8間を接続する少なくとも一つの第二の引き回し部9を有する第二の配線6とを含む。

(もっと読む)

21 - 40 / 292

[ Back to top ]