Fターム[5F033UU05]の内容

半導体集積回路装置の内部配線 (234,551) | レイアウト、シミュレーション (1,514) | 配線の設計、レイアウト (1,445) | 多層に跨がるもの (834) | 3層以上 (227)

Fターム[5F033UU05]に分類される特許

1 - 20 / 227

半導体装置

半導体回路装置およびその製造方法

【課題】ビアヒューズ素子の径を小さくし、ビアヒューズ素子を低電流で溶断することが可能な半導体回路装置およびその製造方法を提供する。

【解決手段】一方向に配置された複数の配線層と、前記複数の配線層のうちの少なくとも2つの前記配線層の間に設けられたビアヒューズ素子と、前記複数の配線層の配置方向に直交する平面内において前記ビアヒューズ素子に隣接する穴と、前記穴内に設けられた貫通ビアとを備えた半導体回路装置。

(もっと読む)

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

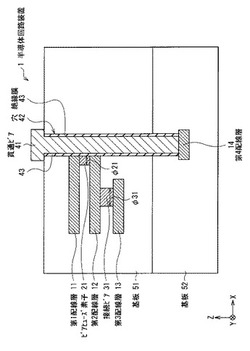

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体装置

【課題】Low−k膜を層間絶縁膜として用いた半導体装置であっても、ダイシング時に発生するクラックがシールリング部へ伝播するのを抑制し、半導体装置の信頼性を向上する技術を提供する。

【解決手段】ダイシング領域側の各層にダミービア125,135,145,155,165を形成する。ダミービア125,135,145,155,165は上面からみて、縦横に等間隔に配置、あるいは千鳥配置されるように形成する。ダイシング時にクラックが発生しても、ダミービア125,135,145,155,165によって、クラックがシールリング部190にまで伝播するのを抑制することができる。その結果、回路形成領域の吸湿耐性を向上させ、信頼性の劣化を防止することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】半導体装置の外部端子に加わる外力により外部端子の下方の絶縁膜にクラックが生じるのを抑制または防止する。

【解決手段】半導体基板1の主面上には複数の配線層が形成されている。この複数の配線層のうちの最上の配線層MHの直下の第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成しない。上記第5配線層M5において、最上の配線層MHのボンディングパッドPDのプローブ接触領域PAの直下以外の領域には、導体パターン(第5配線5F、ダミー配線およびプラグ6C)を形成する。

(もっと読む)

配線レイアウトの設計方法、半導体装置及び配線レイアウトの設計を支援するプログラム

【課題】高集積化を図ることができる配線レイアウトの設計方法、半導体装置及び配線レイアウトの設計を支援するプログラムを提供する。

【解決手段】実施形態に係る配線レイアウトの設計方法は、側壁法によって形成されるレイアウトの設計方法であって、第1の方向に延び、前記第1の方向と交差する第2の方向に第1の周期で配置された複数本の第1のパターン、及び、前記第1の方向に延び、前記第1のパターン間の中央にそれぞれ配置された複数本の第2のパターンが設けられたベースパターンを用意する工程と、1本の前記第2のパターンを挟んで隣り合う2本の前記第1のパターン間に、前記第2の方向に延び、前記2本の第1のパターン同士を接続すると共に、前記1本の第2のパターンを前記2本の第1のパターンと接しない2つのパターンに置き換える工程と、を備える。

(もっと読む)

半導体集積回路、半導体集積回路の設計方法、および半導体集積回路の設計装置

【課題】配線層に形成される信号配線をなるべく迂回させずに配線できるように電源スタックビアが配置された半導体集積回路を提供すること。

【解決手段】半導体集積回路は、第1の方向に延伸された第1,第2の下層電源配線11A,11Bと、第2の方向に延伸された第1,第2の上層電源配線12A,12Bと、上層,下層電源配線を接続させる第1,第2接続部3A,3Bと、を備え、第1,第2接続部は、第1,第2の接続用配線26A,26Bと、第1,第2の位置変換用配線27A,27Bと、第1,第2の上側ビア28A,28Bと、を有して構成され、第1,第2の接続用配線は、第2の方向に沿った同一ライン上に配置され、第1,第2の位置変換用配線は、第1,第2の接続用配線を第2の方向に沿って延長した領域内に形成され、第1,第2の上側ビアは、第1の方向に沿った同一ライン上となる位置に配置される。

(もっと読む)

不揮発性半導体記憶装置及びその製造方法

【課題】メモリセルの制御性を向上した不揮発性半導体記憶装置及びその製造方法を提供する。

【解決手段】実施形態に係る不揮発性半導体記憶装置は、構造体と、複数の半導体層と、メモリ膜と、接続部材と、導電部材と、を備える。前記構造体は、メモリ領域と非メモリ領域とを有する基板の前記メモリ領域の上に設けられる。前記構造体は、前記基板の主面に対して垂直な第1軸に沿って積層され複数の電極膜を含む。前記半導体層は、前記構造体を前記第1軸に沿って貫通する。前記メモリ膜は、前記複数の電極膜と前記半導体層との間に設けられる。前記接続部材は、前記基板と前記半導体層との間に設けられる。前記接続部材は、隣り合う2つの前記半導体層のそれぞれの端部と接続される。前記導電部材は、前記基板と前記接続部材との間で、前記メモリ領域から前記非メモリ領域に延在して設けられる。前記導電部材は、前記非メモリ領域の上に設けられた凹部を有する。前記凹部内には、第1シリサイド部が設けられる。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の素子形成領域へのクラックなどの伝播を確実に防止する。

【解決手段】ウェハ1上の素子形成領域を覆うガード領域4の外側に、n型拡散層15を形成する。n型拡散層15の上には、導電性リング33,48,58を形成する。最上層の導電性リング48の上に、導電層65を形成する。導電層65の端面65Sは、導電性リング58の端面58Sから距離L1だけ内側に形成し、導電性リング58の上面の一部を露出させる。この後、半導体基板をアミン系薬液に浸すと、n型拡散層15と導電層65の間の導電性プラグ33,48,48の導電性材料を溶出し、スリットが形成される。

(もっと読む)

半導体装置

【課題】パッド下のクラックによるショート不良が抑制された半導体装置を提供する。

【解決手段】パッド開口部18aの下の層間絶縁膜16はコンタクト17で囲われているので、ワイヤボンディング時に生じたパッド開口部18aの下の層間絶縁膜16のクラックはコンタクト17の外周縁17aよりも外側に入らない。よって、クラックを通し、パッド開口部18aは、外周縁17aよりも外側のアルミやポリシリコンなどの金属膜や拡散層とショートしない。

(もっと読む)

テスト回路、集積回路、及び、テスト回路のレイアウト方法

【課題】 より簡易な設計手法で作製可能なテスト回路を提供する。

【解決手段】 テスト回路100は、基板と、基板上に形成された配線部及び被試験デバイス部10とを備える構成とする。テスト回路100では、被試験デバイス本体のパターン形成面内における回転中心位置Oと複数の接続電極13a〜13dのそれぞれとを結ぶ直線L1の延在方向が、配線21の延在方向に対して所定の角度で傾いている。さらに、被試験デバイス本体及び複数の接続電極13a〜13dをパターン形成面内で90度回転させた際にも、複数の接続電極13a〜13d及び複数の配線21〜24間の接続が維持されるような位置に複数の接続電極13a〜13dが配置される。

(もっと読む)

半導体装置

【課題】インダクタの下方の層間絶縁膜への水の浸入を抑制し、かつ、インダクタ性能の低下を抑制する。

【解決手段】半導体装置は、半導体基板と、前記半導体基板上に設けられた層間絶縁膜と、前記層間絶縁膜の上部に設けられたインダクタと、前記半導体基板上に設けられ、前記インダクタの下方の前記層間絶縁膜を前記半導体基板の平面方向で囲む第一の金属壁と、前記半導体基板上に設けられ、前記第一の金属壁で囲まれた領域の外側の前記層間絶縁膜を前記半導体基板の平面方向で挟む一対の第二の金属壁と、を備え、前記第一の金属壁は、前記第一の金属壁の両端部を非接触の状態とする開口を有し、前記第二の金属壁は、前記第一の金属壁の両端部にそれぞれの一端を連結するとともに、前記第一の金属壁で囲まれた領域の外側の位置に開口を有する。

(もっと読む)

半導体装置

【課題】インダクタンス値を広範囲に可変可能なインダクタを備える半導体装置を提供する。

【解決手段】半導体装置は、多層配線層と、多層配線層を用いて形成され、巻軸が、多層配線層に対して平行である複数のソレノイド型インダクタと、少なくても1以上のソレノイド型インダクタと接続され、ソレノイド型インダクタの状態を活性化、又は、非活性化する制御回路と、を含んで構成される可変インダクタを備えている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】実際の強誘電体メモリセルについて疲労特性を直接に測定する試験方法を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に形成された強誘電体キャパシタの疲労特性の面内分布を取得する第1の工程と、前記面内分布に基づいて、半導体装置を製造する第2の工程と、を含み、前記第2の工程は、前記半導体装置が形成される基板上に複数の強誘電体キャパシタを形成し、前記第1の工程で取得された疲労特性の面内分布から、前記半導体装置が形成される基板上の特定領域を指定し、前記特定領域に形成された前記強誘電体キャパシタについて疲労特性を測定し、前記特定領域の強誘電体キャパシタについて測定した前記疲労特性に基づき、前記特定領域の強誘電体キャパシタについて良否判定を行い、前記良否判定の結果が良であれば、前記複数の強誘電体キャパシタの全てについて良と判定する。

(もっと読む)

半導体装置および試験方法

【課題】より小さな単位に切り離しも可能なマルチコア半導装置において、前記より小さな単位に切り離した場合に相互接続配線を伝って生じる可能性のある水の侵入を阻止する。

【解決手段】半導体装置は、素子領域を有する半導体基板と、前記素子領域に形成され、第1の開口部を有する内側シールリングと、前記素子領域に形成され、第2の開口部を有する外側シールリングと、前記半導体基板上に形成された、各々配線層を含む複数の層間絶縁膜を積層した積層体よりなる多層配線構造と、前記多層配線構造に含まれる第1の層間絶縁膜とその上の第2の層間絶縁膜の間に形成された耐湿膜と、前記耐湿膜の下側および上側のいずれか一方である第1の側を延在し、前記第1の開口部を通過する第1の部分と、前記耐湿膜の下側および上側の他方である第2の側を延在し、前記第2の開口部を通過する第2の部分と、前記第1の部分と前記第2の部分とを、前記耐湿膜を貫通して接続するビアプラグとを含む配線パターンと、を有する。

(もっと読む)

半導体装置とその製造方法

【課題】クラック伝播を抑制できる新規な構造を有する半導体装置を提供する。

【解決手段】半導体装置は、半導体基板と、半導体基板に形成された半導体素子と、半導体素子を囲む第1金属リングと、半導体素子を覆って形成され、内部に前記第1金属リングが配置された絶縁膜と、絶縁膜に形成された溝とを有し、第1金属リングは、複数の金属層が積層されて形成され、各々の金属層の外側の側面が一致しているか、または、下側に位置する金属層の外側の側面よりも上側に位置する金属層の外側の側面が内側に位置しており、溝の底面は、第1金属リングより内側に配置された第1部分で、第1金属リングの最上層に位置する金属層の上面以下である。

(もっと読む)

半導体装置

【課題】ダイシング時の衝撃を逃がして、半導体装置の歩留まりを向上させる。

【解決手段】半導体装置100は、シリコン層4上に形成された多層配線構造3内で、平面視において素子形成領域50の外周に形成されたシールリング6と、シールリング6のさらに外周に形成されたダミーメタル構造30a〜ダミーメタル構造30iを含む。ダミーメタル配線24は、内周側に形成されたものほど上層に配置される。

(もっと読む)

相互接続構造の珪化物層およびロープロファイルバンプを有するパワーMOSFETを形成する半導体デバイスおよび方法

【課題】相互接続構造の珪化物層と、ロープロファイルバンプを含む、バンプ間ショートを防止したパワーMOSFETからなる半導体デバイスおよび製造方法を提供する。

【解決手段】基板上にソース領域160およびドレイン領域170を有し、珪化物層174が、ソース領域およびドレイン領域の上に配置されている。第1の相互接続層194が、珪化物層上に形成されており、ソース領域に接続される第1のランナー196と、ドレイン領域に接続される第2のランナー198とが配置される。第2の相互接続層214が、第1の相互接続層上に形成されており、第1のランナーに接続される第3のランナー216と、第2のランナーに接続される第4のランナー218とを含む。第3の相互接続層234が形成され、ソースパッド236、ソースバンプ240が電気的に接続される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】高周波配線を含む半導体装置において、エロージョンやディッシングを効果的に防いで半導体装置を安定的に製造するとともに、高周波配線への周囲のダミーメタルからの影響を低減して特性を向上させる。

【解決手段】半導体装置100は、半導体基板上の多層配線層中に設けられた高周波配線102と、多層配線層中の半導体基板と高周波配線102が設けられた層との間の第2の配線層122bに設けられたダミーメタル104とを含む。ダミーメタル104は、平面視で、高周波配線102の外縁で囲まれる第1の領域106とその周囲の第2の領域108とを含む高周波配線近傍領域110と、それ以外の外部領域112とにそれぞれ分散配置され、高周波配線近傍領域110のダミーメタル104間の平均間隔が、外部領域112のダミーメタル104間の平均間隔よりも広い。

(もっと読む)

1 - 20 / 227

[ Back to top ]