半導体装置及びその製造方法

【課題】半導体装置の素子形成領域へのクラックなどの伝播を確実に防止する。

【解決手段】ウェハ1上の素子形成領域を覆うガード領域4の外側に、n型拡散層15を形成する。n型拡散層15の上には、導電性リング33,48,58を形成する。最上層の導電性リング48の上に、導電層65を形成する。導電層65の端面65Sは、導電性リング58の端面58Sから距離L1だけ内側に形成し、導電性リング58の上面の一部を露出させる。この後、半導体基板をアミン系薬液に浸すと、n型拡散層15と導電層65の間の導電性プラグ33,48,48の導電性材料を溶出し、スリットが形成される。

【解決手段】ウェハ1上の素子形成領域を覆うガード領域4の外側に、n型拡散層15を形成する。n型拡散層15の上には、導電性リング33,48,58を形成する。最上層の導電性リング48の上に、導電層65を形成する。導電層65の端面65Sは、導電性リング58の端面58Sから距離L1だけ内側に形成し、導電性リング58の上面の一部を露出させる。この後、半導体基板をアミン系薬液に浸すと、n型拡散層15と導電層65の間の導電性プラグ33,48,48の導電性材料を溶出し、スリットが形成される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体装置は、半導体基板上にマトリックス状に配置されたチップ領域に形成される。半導体回路形成後にチップ領域を切断するときは、チップ領域の間のスクライブライン領域で半導体基板をダイシングする。

【0003】

半導体基板をダイシングするときには、チップ領域の外周部分にクラックや欠けが発生することがある。半導体装置のチップの周辺部にクラックや欠けが生じると、外部から水分が浸入し易くなる。このために、半導体装置では、チップ領域の外周部分に、ガードリング(耐湿リング)を設けて、水分の浸入を防止している。

【0004】

ガードリングは、上下のリング状の金属層をプラグで接続させた構成を有する。このようなガードリングは、半導体装置の多層配線構造と同時に形成される。すなわち、回路の金属配線を形成するときに、同時にリング状の金属層がチップ領域の外周部分に形成される。そして、回路の配線を接続する導電性のプラグを形成するときに、上下のリング状の金属層を接続するプラグが同時に形成される。

【0005】

ところが、層間絶縁膜が低誘電率膜の場合には、ガードリングを形成しても、素子領域へのクラックの伝播を十分に防止できないことがあった。そこで、従来の半導体装置では、半導体基板上のチップ領域に、基板の表面に対して垂直方向に延びる中空溝を形成することが知られている。中空溝を形成するときは、最初に層間絶縁膜にリング状の溝を素子形成領域を覆うように形成する。リング状の溝には、配線材料を埋め込む。最上層の配線層を形成したら、最上層の上にフォトレジスト膜からなるマスクを形成する。マスクは、素子形成領域を覆い、素子形成領域の外側のリング状の溝に埋め込んだ配線材料を露出させる形状にする。この後、マスクを用いてリング状の溝に埋め込まれた配線材料をエッチングして除去する。これによって、リング状の中空溝が形成される。

【0006】

ここで、配線材料が銅の場合には、塩酸と過酸化水素水の混合液を使用して配線材料をエッチングする。バリアメタルにタンタルが用いられていた場合には、CF4ガスを使用したCDE(Chemical Dry Etching)、又はフッ化水素溶液を使用したウエットエッチングをする。リング状の溝には、配線層の数だけ、バリアメタルと配線材料が交互に配置されるので、エッチング工程では、塩酸と過酸化水素水の混合液によるエッチングと、CDEとを交互に行う。また、RIE(Reactive Ion Etching)法によって配線材料とバリアメタルを同時にエッチングすることもある。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特願2005−142262

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、従来の半導体装置では、リング状の溝から配線材料を除去するために、フォトレジスト膜を形成する工程と、フォトレジスト膜をパターニングしてマスクを形成する工程と、リング状の溝内の配線材料をエッチングによって除去する工程とを追加する必要があった。さらに、配線材料をエッチングによって除去する工程では、配線材料を除

去する工程と、バリアメタルを除去する工程とを交互に実施しなければならないことがあった。

【0009】

また、RIE法によって配線材料とバリアメタルを同時にエッチングする場合には、エッチング時間が長くなるので、生産性が低下する。さらに、レジスト膜に加えてハードマスクを形成するなどの追加工程が必要になる。

この発明は、このような事情に鑑みてなされたものであり、半導体装置の素子形成領域へのクラックなどの伝播を確実に防止することを目的とする。

【課題を解決するための手段】

【0010】

実施形態の一観点によれば、半導体基板と、前記半導体基板上の素子領域に形成された半導体素子と、前記半導体基板の上方に形成された絶縁膜と、前記絶縁膜に埋め込まれ、前記素子領域を囲むガードリングと、前記ガードリングを囲み、前記絶縁膜を表面から前記半導体基板に至るまで貫通するスリットと、前記半導体基板上に配置され、前記スリットの一方の端部に接続された第1の導電部と、前記半導体基板の上方に配置され、前記スリットの他方の端部に接続された第2の導電部と、を含むことを特徴とする半導体装置が提供される。

【0011】

また、実施形態の別の観点によれば、半導体基板上の素子領域に半導体素子を形成する工程と、前記半導体基板上に第1の導電部を形成する工程と、前記半導体基板の上方に絶縁膜を形成する工程と、前記絶縁膜中にガードリングを形成し、前記ガードリングで前記素子領域を囲む工程と、前記絶縁膜中に、前記第1の導電部に接続する導電性リングを形成し、前記導電性リングで前記カードリングを囲む工程と、前記導電性リングに接続される第2の導電部を前記導電性リングの上に形成する工程と、前記第1の導電層と前記第2の導電層の間の前記導電性リングを構成する導電性材料をアミン系薬液によって溶出させ、前記導電性リングが埋め込まれていた前記絶縁膜にスリットを形成する工程と、を含むことを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0012】

ウェハのダイシング時に層間絶縁膜にクラックが発生してもスリットによってクラックの伝播が防止される。アミン系薬液を用いて導電性材料を溶出させる場合は、簡単にスリットを形成できる。

【図面の簡単な説明】

【0013】

【図1A】図1Aは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図1B】図1Bは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図1C】図1Cは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図1D】図1Dは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図1E】図1Eは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その5)である。

【図1F】図1Fは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その6)である。

【図1G】図1Gは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その7)である。

【図1H】図1Hは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その8)である。

【図1I】図1Iは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その9)である。

【図2A】図2Aは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図2B】図2Bは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図2C】図2Cは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図2D】図2Dは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図3A】図3Aは、本発明の第3の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図3B】図3Bは、本発明の第3の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図3C】図3Cは、本発明の第3の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図4A】図4Aは、本発明の第4の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図4B】図4Bは、本発明の第4の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図4C】図4Cは、本発明の第4の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図4D】図4Dは、本発明の第4の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図4E】図4Eは、本発明の第4の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その5)である。

【図5A】図5Aは、本発明の第5の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図5B】図5Bは、本発明の第5の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図5C】図5Cは、本発明の第5の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【発明を実施するための形態】

【0014】

発明の目的及び利点は、請求の範囲に具体的に記載された構成要素及び組み合わせによって実現され達成される。

前述の一般的な説明及び以下の詳細な説明は、典型例及び説明のためのものであって、本発明を限定するためのものではない。

【0015】

(第1の実施の形態)

図面を参照して第1の実施の形態について説明する。

まず、図1Aに示す断面構造を得るまでの工程について説明する。

図1Aに示すように、シリコンなどのウェハ(半導体基板)1に、素子分離領域2を複数形成する。素子分離領域2は、シャロートレンチアイソレーション(STI)を使用する。STIは、ウェハ1の素子分離領域に溝を形成し、その中にシリコン酸化等の絶縁膜を埋め込むことにより形成される。なお、素子分離領域2は、STIに限られず、LOCOS(Local Oxidation of Silicon)法で形成した絶縁膜を使用しても良い。素子分離領域2によって、ウェハ1には、半導体素子や配線が形成される素子領域3と、素子領域3を囲むガード領域4と、ガード領域4を囲むスリット領域5と、スリット領域5を囲む格子状のスクライブライン領域6とに区画される。

【0016】

次いで、ウェハ1の表面に不純物をイオン注入し、ウェル11,12を形成する。例えば、素子領域3及びガード領域4には、ドーパント不純物としてn型不純物、例えばリンを導入してnウェル11を形成する。スリット領域5とスクライブライン領域6には、p型不純物、例えばボロンを導入してpウェル12を形成する。

【0017】

この後、ウェハ1上のトランジスタ活性領域の表面を熱酸化させてゲート絶縁膜13を形成する。ゲート絶縁膜13は、熱酸化によるシリコン酸化膜であり、その厚さは例えば1〜10nmである。また、ゲート絶縁膜13は、誘電率の高い材料で形成しても良い。

【0018】

この後、ウェハ1の全面に、非晶質又は多結晶のシリコン膜を形成する。シリコン膜の膜厚は、例えば約100nmとする。シリコン膜をパターニングすることにより、ゲート電極14を形成する。ここで、ゲート電極14は、金属材料から形成しても良い。

【0019】

続いて、ゲート電極14をマスクにしたイオン注入により、ゲート電極14の両側と、ガード領域4のウェハ表層にp型不純物、例えばボロンを導入して、p型拡散層15を形成する。また、スリット領域5とスクライブライン領域6のウェハ表層には、n型不純物、例えばリンを導入してn型拡散層16を形成する。n型拡散層16は、第1の導電部として機能する。

【0020】

この後に、ゲート電極14を含むウェハ1の上側全面に絶縁膜を形成する。絶縁膜としては、例えばCVD法により形成された酸化シリコン膜が用いられる。そして、絶縁膜をエッチバックしてゲート電極14の両側部分のみを残し、絶縁性サイドウォール17を形成。

【0021】

続いて、絶縁性サイドウォール17とゲート電極14をマスクにしてゲート電極14の両側に、不純物を再びイオン注入する。これにより、各ゲート電極14の側方のウェハ1にソース/ドレイン領域18(高濃度不純物拡散領域)が形成される。

さらに、ゲート電極14を含むウェハ1の上側全面に、金属膜をスパッタ法により形成する。金属膜は、例えば、コバルト膜やニッケル膜の高融点金属が好ましいが、比較的に融点が低い金属であっても良い。そして、この金属膜を加熱してシリコンと反応させる。これにより、ゲート電極14の上面と、ソース/ドレイン領域18上のそれぞれに、コバルトシリサイド層やニッケルシリサイド層といった金属シリサイド層19A、19Bが形成される。この熱処理によって、各ソース/ドレイン領域18が活性化されて低抵抗化する。このとき、スリット領域5とスクライブライン領域6のn型拡散層16の表層にも、金属シリサイド層19Cが形成される。

【0022】

その後に、素子分離領域2上などで未反応となっている金属膜をウエットエッチングによって除去する。ここまでの工程で、ウェハ1の活性領域ごとに、ゲート絶縁膜13,ゲート電極14、ソース/ドレイン領域18等によって構成されるトランジスタT1(半導体素子)が形成される。

【0023】

次に、トランジスタT1を含むウェハ1の全面にシリコン窒化膜21を例えば80nmの厚さに形成する。シリコン窒化膜21は、それぞれがプラズマCVD法によって形成する。続いて、シリコン窒化膜21の上に、第1層間絶縁膜22として、例えば、シリコン酸化(SiO2)膜をTEOS(tetra ethoxy silane)ガスを用いたプラズマCVD法によって1300nmの厚さに形成する。第1層間絶縁膜22の表面は、化学的機械研磨(CMP:Chemical Mechanical Polishing)法を用いて研磨し、ウェハ1の表面から第1層間絶縁膜22の表面までの膜厚を所定値、例えば約950nmに調整する。

【0024】

さらに、第1層間絶縁膜22の上にレジスト膜23を塗布した後、レジスト膜23にフォトリソグラフィによって開口部23Aを形成する。開口部23Aは、素子領域2のトランジスタT1のソース/ドレイン領域18の上方に複数形成される。また、開口部23Aは、ガード領域4の上方に2つ、スリット領域5の上方に1つ、それぞれ形成される。

【0025】

続いて、図1Bに示す断面構造を得るまでの工程について説明する。

レジスト膜23をマスクにしたドライエッチングにより、第1層間絶縁膜22、シリコン窒化膜21を順番に加工する。エッチング深さは、ソース/ドレイン領域17の高融点金属シリサイド層19Aに到達するまでとする。これにより、ソース/ドレイン領域18の上にコンタクトホール25が形成される。また、ガード領域4に第1のリング溝26が2重に形成される。第1のリング溝26は、素子領域3の周囲を連続して囲むリング形を有する。さらに、スリット領域5には、第2のリング溝27が1つ形成される。第2のリング溝27は、第1のリング溝26の周囲を連側して囲む連続したリング形を有する。第2のリング溝27の幅は、例えば0.22μmとする。

【0026】

続いて、図1Cに示す断面構造を得るまでの工程について説明する。

まず、コンタクトホール25内に、ソース/ドレイン領域17に電気的に接続される導電性プラグ31を形成する。また、これと同時に、第1のリング溝26内、及び第2のリング溝27内に、それぞれ導電性リング32及び導電性リング33を形成する。

【0027】

具体的には、最初に、コンタクトホール25及び第1、第2のリング溝26,27の内面に、密着層35をスパッタ法によって形成する。密着層は、30nmのチタン膜と、20nmの窒化チタン膜とを積層して形成する。さらに、密着膜35の上に、タングステン膜36をCVD法により成長させる。タングステン膜36は、各ホール25及び溝26,27に埋め込まれると共に、第1層間絶縁膜22の上方に、例えば300nmの厚さに成長させる。

【0028】

この後、第1層間絶縁膜22上に成長した余分なタングステン膜36及び密着膜35をCMP(Chemical Mechanical Polishing)法による研磨で除去する。この結果、コンタクトホール25に導電性プラグ31が形成される。これと同時に、第1及び第2のリング溝26,27のそれぞれに、導電性リング32,33が形成される。なお、導電性リング32,33の形状は、平面視で矩形のリングになる。

【0029】

次に、図1Dに示す断面構造を得るまでの工程について説明する。

導電性プラグ31及び導電性リング32,33を含む第1層間絶縁膜22の上に、下地層37を形成する。下地層37は、例えば、60nmの厚さのチタン膜と、30nmの厚さのチタン窒化膜をスパッタ法によって積層させて形成する。さらに、下地層37の上には、アルミニウム膜38をスパッタ法によって360nmの厚さに形成する。続いて、アルミニウム膜38上には、上地層39として、例えば5nmの厚さのチタン膜と、70nmの厚さのTiN膜をスパッタ法によって積層させて形成する。これによって、下地層37、アルミニウム膜38、上地層39が積層された導電性多層膜が形成される。

【0030】

この後、上地層39の上に不図示のレジスト膜を形成する。レジスト膜には、フォトリソグラフィによって開口部を形成する。レジスト膜をマスクにして、導電性多層膜をエッチングする。導電性プラグ31の上に、導電性多層膜からなる配線(導体パターン)41が形成される。また、導電性リング32の上には、ガード層(導体パターン)42が形成される。導電性リング33の上には、導体パターンは形成しない。これによって、1層目の配線層43が形成される。

【0031】

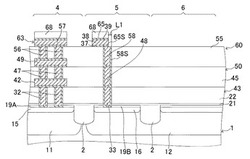

次に、図1Eに示す断面構造を得るまでの工程について説明する。図1E以降は、ガー

ド領域4、スリット領域5、及びスクライブライン領域6を拡大して示す。

まず、第1層間絶縁膜22上に、第2層間絶縁膜45を形成する。第2層間絶縁膜45は、例えば、高密度プラズマ(High Density Plasma;HDP)CVD法、又はTEOSガスを用いたプラズマCVD法によって形成されるシリコン酸化膜が用いられる。ここで、第2層間絶縁膜45は、HDP−CVD法によるシリコン酸化膜と、TEOSガスを用いたプラズマCVD法によるシリコン酸化膜の積層膜でも良い。この場合は、HDP−CVD法によるシリコン酸化膜を例えば720nmの厚さに形成した後、TEOSガスを用いたプラズマCVD法によるシリコン酸化膜を例えば1100nmの厚さに形成する。その後、第2層間絶縁膜45の表面は、CMP法による研磨で平坦化される。第2層間絶縁膜45の膜厚は、例えば、約1100nmとする。

【0032】

第2層間絶縁膜45には、ガード領域4に導電性リング47を2重に埋め込む。ガード領域4の導電性リング47は、下層のガード層42に接続される。同様に、スリット領域5には、導電性リング48を埋め込む。スリット領域5の導電性リング48は、下層の導電性リング33に接続される。導電性リング47,48の形状及び形成方法は、図1C及び図1Dを参照して説明したプロセスと同様である。また、不図示の素子領域3では、第2層間絶縁膜45に導電性プラグを埋め込む。

【0033】

さらに、導電性リング47の上には、ガード層49をリング形に形成する。また、ガード層49と同時に、素子領域3に不図示の配線を形成する。ガード層49及び配線の形状及び形成方法は、図1Eを参照して説明したプロセスと同様である。これによって、2層目の配線層50が形成される。

【0034】

さらに、2層目の配線層50の上に、3層目の配線層60を形成する。3層目の配線層60は、2層目の配線層50と同様のプロセスで形成する。ガード領域4のガード層49の上には、導電性リング56を形成する。導電性リング56上には、ガード層57を形成する。ガード層57の幅は、2つの導電性リング56の幅と、導電性リング56間の距離との和より大きい。このために、2つの導電性リング56は、ガード層57の下に隠れる。各導電性リング32,47,56、ガード層42,49,57によってガードリング63が形成される。

【0035】

また、スリット領域5には、導電性リング58が形成される。導電性リング58は、下方の導電性リング48に接続される。スリット領域5の導電性リング58の上には、導電層65(第2の導電部)を形成する。

【0036】

ここで、ガード層57及び導電層65の形成と同時に、不図示の素子領域3に配線を形成する。ガード層57、導電層65、及び不図示の配線を形成するときは、最初に、下地層37と、アルミニウム膜38と、上地層39とを積層した導電性多層膜を形成し、導電性多層膜上にポジ型のレジスト膜68を塗布する。レジスト膜68に対してフォトリソグラフィによって開口部を形成し、レジスト膜68をマスクにして導電性多層膜をドライエッチングする。

【0037】

導電層65は、導電性リング58の上面の一部を覆っており、さらに導電性リング58に対してガード領域4(素子領域3)側にオフセットして形成される。導電層65は、導電性リング58の一部を露出させ、後述する薬液処理時に薬液が導電性リング58に接触可能な開口部を導電性リング58に形成させている。従って、導電層65の外側の端面65Sと、導電性リング58の外側の端面58Sとの間の距離L1の下限値は、例えば5nmである。一方、距離L1の上限値は、導電層65と導電性リング58が電気的な接触を確保できる距離である。

【0038】

次に、図1Fに示す断面構造を得るまでの工程について説明する。

最初に、ガード層57上や、導電層65上に残ったレジスト膜68をウエットエッチングと、アッシングによって除去する。さらに、レジスト膜除去後のウェハ1をアミン系薬液に浸す。アミン系薬液としては、例えば富士フィルム社製のMS4092B、又はAshland−ACT社のACT−930シリーズが好ましい。アミン系薬液は、70℃に加熱し、ウェハ1は15分浸漬させる。

【0039】

ここで、スリット領域5において、導電層65は導電性リング58の一部を露出させる位置に形成されているので、アミン系薬液が導電性リング58の表面に供給される。これによって、n型拡散層16と導電層65とに挟まれた導電性リング33,48,58のタングステン、窒化チタン、チタンがアミン系薬液によって溶出する。タングステンなどの導電性材料は、導電性リング58の上面から溶出する。

【0040】

導電性リング33,48,58内の全ての導電性材料が、導電層65と層間絶縁膜55とによって形成される上部の開口を通って溶出すると、導電性リング33,48,58が埋め込まれていた空間に、スリットリング(リング状の溝)70が形成される。ここで、タングステン、窒化チタン、チタンが溶出するメカニズムとしては、例えば、電池作用に基づいた電気化学的反応が考えられる。

【0041】

続いて、図1Gに示すように、第3層間絶縁膜55上にカバー膜として、HDP−CVD法によるシリコン酸化膜71を例えば720nmの厚さに形成する。シリコン酸化膜71の上には、プラズマCVD法による窒化シリコン膜72を例えば1000nmの厚さに形成する。この後、窒化シリコン膜72上にレジスト膜73を形成する。レジスト膜73には、フォトリソグラフィによって開口部73Aを形成する。開口部73Aは、スリットリング70の内側の端面と一致する位置に形成される。レジスト膜73をマスクにしてススリット領域5の窒化シリコン膜72、シリコン酸化膜71、第3層間絶縁膜55、第2層間絶縁膜45の上部をエッチングによって除去する。

【0042】

これによって、図1Hに示すように、スリット領域5からスクラブ領域6にかけて開口部75が形成される。導電層65は、エッチングによって除去されない。また、スリットリング70は、側部の一部が開放される。

【0043】

次に、図1Iに示す断面構造を得るまでの工程について説明する。まずダイシングブレードを用いて、ウェハ1を複数のチップに切断する。ダイシングブレードによって、スクライブライン領域6上のウェハ1、各層間絶縁膜22,45が切断される。これによって、複数のチップが個片化され、半導体装置80が形成される。

【0044】

このとき、ダイシングブレードによる切断時に生じる応力で、層間絶縁膜22,34,にクラックが発生することがある。層間絶縁膜22,34で発生したクラックの進行は、スリットリング70によって上方に開放される。このために、クラックがガードリング63や、半導体回路に伝播することはない。

【0045】

以上、説明したように、この実施の形態では、ガードリング63の外側に、連続したリング状のスリットリング70を形成したので、半導体装置80の外側の端部でクラックや欠けが発生しても、スリットによってクラック等がガードリング63に伝播することが防止される。

【0046】

また、この実施の形態では、半導体ウェハ1の表層部分のn型拡散層16を第1の導電部とし、多層配線の最上層に形成した導電層65を第2の導電部とし、これら導電層に挟まれた導電性材料(チタン、チタン窒化膜、タングステン)をアミン系薬液による薬液処

理によって溶出させるようにした。マスクを用いて導電性材料をエッチングする領域を確定する工程が不要になり、製造効率が向上する。さらに、チタンや、チタン窒化膜、タングステンのように複数種類の導電性材料であっても、1回の薬液処理によって除去することができるので、複数種類のウエットエッチング工程を交互に実施する場合に比べて、製造効率が向上する。

【0047】

さらに、図1Eに示すように、導電層65を導電性リング58に対してオフセットして配置し、導電性リング58の上面の一部を露出させたので、薬液処理時に導電性リング58のチタン、チタン窒化膜、タングステンを確実に溶出させられる。これに対して、ガード領域4では、ガード層57が導電性リング56を完全に覆っているので、薬液処理しても導電性リング56のチタン、チタン窒化膜、タングステンが溶出することはない。

【0048】

(第2の実施の形態)

第2の実施の形態について図面を参照して説明する。第1の実施の形態と同じ構成要素には同一の符号を付している。また、第1の実施の形態と重複する説明は省略する。

図2Aに示すように、ガード領域4の第3層間絶縁膜55に、導電性リング56を埋め込み、スリット領域5に導電性リング58を埋め込む。この後、ガード層57と導電層65を形成する。導電層65の外側の端部65Sは、導電性リング58の外側の端部58Sと一致させる。即ち、導電性リング58は、導電層65の下に完全に隠れている。

【0049】

続いて、図2Bに示すように、第3層間絶縁膜55上にカバー膜として、HDP−CVD法によるシリコン酸化膜71と、プラズマCVD法による窒化シリコン膜72を順番に形成する。この後、窒化シリコン膜72上にレジスト膜73を塗布し、開口部73Aを形成する。

【0050】

さらに、図2Cに示すように、レジスト膜73をマスクにして、スリット領域5及びスクライブライン領域6の窒化シリコン膜72、シリコン酸化膜71、第3層間絶縁膜55、及び第2層間絶縁膜45の一部をエッチングによって除去する。エッチング後には、レジスト膜73をウエットエッチングと、アッシングによって除去する。スリット領域5とスクライブライン領域6に開口部75が形成される。

【0051】

ここで、導電層65は、導電性リング58の上面を覆い、かつ導電層65と導電性リング58の各々の端部65S,58Sが一致しているので、導電性リング58,48の外側の層間絶縁膜55,45の一部がエッチングによって除去される。従って、開口部75によって、導電性リング58の外側の側部58Sと、その下の導電性リング48の外側の端部48Sの一部が露出する。

【0052】

次に、図2Dに示すように、ウェハ1をアミン系薬液に浸すと、n型拡散層16と導電層65とに挟まれた導電性リング33,48,58を構成するタングステン、窒化チタン、チタンが、アミン系薬液によって溶出する。導電性材料は、導電性リング48,58の側部48S,58Sの露出部分から溶出する。導電性リング33,48,58内の全ての導電性材料が、開口部75側から溶出すると、導電性リング33,48,58が埋め込まれていた空間に、スリットリング(リング状の溝)70が形成される。この後、スクライブラインに沿ってウェハ1を切断すると、半導体装置が得られる。

【0053】

以上、説明したように、この実施の形態では、導電性リング48,58の外側の端部48S,58Sを露出させた後、アミン系薬液を用いた薬液処理するようにしたので、チタンや、チタン窒化膜、タングステンをより確実に溶出させられる。その他の効果は、第1の実施の形態と同様である。

【0054】

ここで、図1Eに示すように、導電層65は、導電性リング58の外側の端部58Sより内側に形成しても良い。これに対して、導電層65が導電性リング58の外側の端部58Sより外側に配置されると、エッチング時に導電性リング58の側面が露出しなくなるので好ましくない。

【0055】

(第3の実施の形態)

第3の実施の形態について図面を参照して説明する。前記の各実施の形態と同じ構成要素には同一の符号を付している。また、前記の各実施の形態と重複する説明は省略する。

図3Aに示すように、第3層間絶縁膜55上に、ガード層57と、導電層65と、導電層91を形成する。導電層65の外側の端部65Sは、導電性リング58の外側の端部58Sと一致させる。また、外側の導電層91は、導電層65を囲むようにリング状に形成されている。

【0056】

ここで、導電層91は、導電層64の端部65Sから所定距離、例えば最小抜き基準の間隔L2だけ離れた位置に形成されている。最小抜き基準の間隔L2は、それより短い距離で導電層を配置すると、導電層間の第3層間絶縁膜55をエッチングできなくなる距離をいう。最小抜き基準の間隔L2は、エッチング装置の性能等によって決まる値であって、例えば、0.24μmとする。

【0057】

2つの導電層65,91が最小抜き基準の間隔L2で配置されているので、導電層65,91の形状のばらつきを最小限に止めることができる。その結果、導電層65の外側の端部58Sの形状がだれてテーパ状になることを防止できる。即ち、導電層65の端部65Sが導電性リング58の端部58Sを越えて導電層91側に残ることがなくなる。

【0058】

続いて、図3Bに示す断面構造を得るまでの工程について説明する。

第3層間絶縁膜55上にシリコン酸化膜71と、窒化シリコン膜72を積層する。さらに、不図示のレジスト膜をマスクにして、スリット領域5及びスクライブライン領域6の窒化シリコン膜72、シリコン酸化膜71、第3層間絶縁膜55、第2層間絶縁膜45の一部をエッチングによって除去する。これによって、導電層91の外側に開口部93が形成される。さらに、2つの導電層65,91の間に開口する溝92がリング状に形成される。溝92によって、導電性リング58の外側の端面58Sと、その下の導電性リング48の外側の端面48Sの上部が露出する。導電層65の端面と導電性リング58の端面58Sとが一致しているので、溝92によって導電性リング48,58が確実に露出する。エッチング後には、レジスト膜をウエットエッチングと、アッシングによって除去する。

【0059】

続いて、図3Cに示すように、ウェハ1をアミン系薬液に浸し、n型拡散層16と導電層65とに挟まれた導電性リング33,48,58を構成するタングステン、窒化チタン、チタンをアミン系薬液によって溶出させる。導電性材料は、導電性リング48,58の側部48S,58Sの露出部分から溶出する。その結果、導電性リング33,48,58が埋め込まれていた空間に、スリットリング(リング状の溝)70が形成される。この後、スクライブラインに沿ってウェハ1を切断すると、半導体装置が得られる。

【0060】

以上、説明したように、この実施の形態では、導電性リング48,58の外側の端部48S,58Sを露出させた後、アミン系薬液を用いた薬液処理するようにしたので、チタンや、チタン窒化膜、タングステンをより確実に溶出させられる。導電層65の外側に、最小抜き基準の間隔L2だけ離れた位置に導電層91を形成したので、導電層65,91間に配置された第3層間絶縁膜55をエッチングして溝92を形成することができる。溝92を形成することで、導電性リング33,48,58内のチタンや、チタン窒化膜、タングステンをより確実に溶出させられる。その他の効果は、第1の実施の形態と同様である。

【0061】

(第4の実施の形態)

第4の実施の形態について図面を参照して説明する。前記の各実施の形態と同じ構成要素には同一の符号を付している。また、前記の各実施の形態と重複する説明は省略する。

図4Aに示すように、第1層間絶縁膜22に第1のリング溝26と、第2のリング溝27を形成する。第2のリング溝27は、2重に配列されている。各リング溝26,27には、チタン膜と窒化チタン膜を積層させた密着膜35を利用してタングステン膜36を埋め込んで導電性リング33A,33Bを形成する。導電性リング33A,33Bの幅は、例えば、0.22μmとし、導電性リング33A,33Bの間の距離は、例えば、0.26μm以下にする。

【0062】

図4Bに示すように、スリット領域5には、2重の導電性リング33A,33B,48A,48B,58A,58Bが形成される。さらに、第3層間絶縁膜55の上には、導電層95,96,97が形成される。導電層95(第2の導電部)は、2つの導電性リング58A,58Bを跨ぎ、導電層95の両端部のそれぞれから、導電性リング58Aの一部と、導電性リング58Bの一部が露出している。導電層96は、導電層95及び導電性リング58Aより内側に形成される。導電層97は、導電層95及び導電性リング58Bより外側に形成される。導電層95の幅は、例えば0.46μm以下とする。導電層96,97の幅は、0.24μm以下とする。導電性リング58Aは、導電層95の内側の端面95Uから例えば20nm露出している。同様に、導電性リング58Bは、導電層95の外側の端面95Sから例えば20nm露出している。中央の導電層95と、左右の導電層96,97との間は、距離L3だけ離れている。距離L3は、導電層86側と、導電層97側とで、異なる値にしても良いし、同じ値でも良い。距離L3は、例えば、0.24μmとする。

【0063】

続いて、図4Cに示す断面構造を得るまでの工程について説明する。

第3層間絶縁膜55上に、シリコン酸化膜71、窒化シリコン膜72を形成する。さらに、窒化シリコン膜72の上には、レジスト膜73を塗布によって形成する。フォトリソグラフィによってレジスト膜73に開口部73Bを形成する。開口部73Bは、スリット領域5において配線96より内側の位置から、スクライブライン領域6にかけて形成される。

【0064】

さらに、図4Dに示すように、レジスト膜73をマスクにして、スリット領域5及びスクライブライン領域6の窒化シリコン膜72、シリコン酸化膜71、第3層間絶縁膜55、第2層間絶縁膜45の一部をエッチングによって除去する。これによって、2つの配線95,96の間に開口する溝101がリング状に形成される。溝101によって、導電性リング48A,58Aの内側の端面48U,58Uが露出させられる。また、2つの配線95,97の間に開口する溝102がリング状に形成される。溝102によって、導電性リング48B,58Bの外側の端面48S,58Sが露出させられる。配線97の外側には、開口部103が形成される。エッチング後には、レジスト膜73をウエットエッチングと、アッシングによって除去する。

【0065】

続いて、図4Eに示す断面構造を得るまでの工程について説明する。

最初に、ウェハ1をアミン系薬液に浸漬させる。n型拡散層16と導電層65とに挟まれた導電性リング33A,48A,58Aを構成するタングステン、窒化チタン、チタンがアミン系薬液によって溶出する。これら導電性材料は、導電性リング48,58の側部48S,48U,58S,58Uの露出部分から溶出する。その結果、導電性リング33A,48A,58Aが埋め込まれていた空間に、スリットリング(リング状の溝)104が形成される。また、導電性リング33B,48B,58Bを構成するタングステン、窒化チタン、チタンがアミン系薬液によって溶出する。その結果、導電性リング33B,4

8B,58Bが埋め込まれていた空間に、スリットリング(リング状の溝)105が形成される。この後、スクライブラインに沿ってウェハ1を切断すると、半導体装置が得られる。

【0066】

以上、説明したように、この実施の形態では、スリットリング104,105が2重に配列されるので、クラックの伝播をより確実に防止できる。また、導電層95を挟むように一対の導電層96,97を配置したので、導電層95の形状をコントロールでき、溝101,102を確実に形成できる。その他の効果は、第3の実施の形態と同様である。

【0067】

(第5の実施の形態)

第5の実施の形態について図面を参照して説明する。前記の各実施の形態と同じ構成要素には同一の符号を付している。また、前記の各実施の形態と重複する説明は省略する。

図5Aに示すように、スリット領域5の第3層間絶縁膜55上に、導電層110,111を形成する。導電層110は、ガード領域4を囲むリング形状を有する。導電層110は、導電性リング58Aを覆い、その外側の端面110Sが導電性リング58Aの外側の端面58Sと一致する。導電層111は、導電層110を囲むリング形状を有する。導電層111は、導電性リング58Bを覆い、その内側の端面111Uが導電性リング58Bの内側の端面58Uと一致する。

【0068】

ここで、導電層110,111間の距離を最小抜き基準の間隔L2にすると、導電層110,111の端部がテーパ形状になることが防止され、導電層110,111の端面110S,110Uと、対応する導電性リング58A,58Bの端面58S,58Uとが不一致になることが防止される。

【0069】

続いて、図5Bに示す断面構造を得るまでの工程について説明する。

第3層間絶縁膜55上に、シリコン酸化膜71、窒化シリコン膜72を形成する。不図示のレジスト膜をマスクにして、スリット領域5及びスクライブライン領域6の窒化シリコン膜72、シリコン酸化膜71、第3層間絶縁膜55、第2層間絶縁膜45の一部をエッチングによって除去する。これによって、2つの導電層100,101の間に開口する溝115がリング状に形成される。溝115によって、導電性リング48A,58Aの外側の端面48S,58Sと、導電性リング48B,58Bの内側の端面48U,58Uが露出する。導電層111の外側には、開口部116が形成される。エッチング後には、レジスト膜73をウエットエッチングと、アッシングによって除去する。

【0070】

続いて、図5Cに示す断面構造を得るまでの工程について説明する。

最初に、ウェハ1をアミン系薬液に浸漬させる。n型拡散層16と導電層110とに挟まれた導電性リング33A,48A,58Aを構成するタングステン、窒化チタン、チタンがアミン系薬液によって溶出する。その結果、導電性リング33A,48A,58Aが埋め込まれていた空間に、スリットリング(リング状の溝)117が形成される。また、n型拡散層16と導電層111とに挟まれた導電性リング33B,48B,58Bを構成するタングステン、窒化チタン、チタンがアミン系薬液によって溶出する。その結果、その結果、導電性リング33B,48B,58Bが埋め込まれていた空間に、スリットリング(リング状の溝)118が形成される。この後、スクライブラインに沿ってウェハ1を切断すると、半導体装置が得られる。

【0071】

以上、説明したように、この実施の形態では、スリットリング117,118が2重に配列されるので、クラックの伝播をより確実に防止できる。また、一対の導電層110,111を配置したので、導電層1110,111の形状をコントロールでき、導電層110,111をマスクにしたエッチングによって溝115を確実に形成できる。その他の効果は、第3の実施の形態と同様である。

【0072】

前記の各実施の形態において、第1の導電部は、ウェハ1上に形成した導体膜であっても良い。

【0073】

ここで挙げた全ての例及び条件的表現は、発明者が技術促進に貢献した発明及び概念を読者が理解するのを助けるためのものであり、ここで具体的に挙げたそのような例及び条件に限定することなく解釈するものであり、また、明細書におけるそのような例の編成は本発明の優劣を示すこととは関係ない。本発明の実施形態を詳細に説明したが、本発明の精神及び範囲から逸脱することなく、それに対して種々の変更、置換及び変形を施すことができる。

【0074】

以下に、前記の実施の形態の特徴を付記する。

(付記1) 半導体基板と、前記半導体基板上の素子領域に形成された半導体素子と、前記半導体基板の上方に形成された絶縁膜と、前記絶縁膜に埋め込まれ、前記素子領域を囲むガードリングと、前記ガードリングを囲み、前記絶縁膜を表面から前記半導体基板に至るまで貫通するスリットと、前記半導体基板上に配置され、前記スリットの一方の端部に接続された第1の導電部と、前記半導体基板の上方に配置され、前記スリットの他方の端部に接続された第2の導電部と、を含むことを特徴とする半導体装置。

(付記2) 前記第1の導電部は、前記ガードリングから離れて配置されていることを特徴とする付記1に記載の半導体装置。

(付記3) 前記第2の導電部の少なくとも一部が、前記スリットの他方の端部上に配置されていることを特徴とする付記1又は付記2に記載の半導体装置。

(付記4) 前記第2の導電部を囲む第3の導電部を有し、前記第3の導電部と前記第2の導電部の間に、前記スリットが開口していることを特徴とする付記3に記載の半導体装置。

(付記5) 前記スリットは、前記ガードリングを連続して囲むことを特徴とする付記1乃至付記4のいずれか一項に記載の半導体装置。

(付記6) 前記スリットを複数有することを特徴とする付記1乃至付記5のいずれか一項に記載の半導体装置。

(付記7) 前記第1の導電部と、前記第2の導電部は、共に前記素子領域を連続して囲っている付記1に記載の半導体装置。

(付記8) 半導体基板上の素子領域に半導体素子を形成する工程と、前記半導体基板上に第1の導電部を形成する工程と、前記半導体基板の上方に絶縁膜を形成する工程と、前記絶縁膜中にガードリングを形成し、前記ガードリングで前記素子領域を囲む工程と、前記絶縁膜中に、前記第1の導電部に接続する導電性リングを形成し、前記導電性リングで前記カードリングを囲む工程と、前記導電性リングに接続される第2の導電部を前記導電性リングの上に形成する工程と、前記第1の導電部と前記第2の導電部の間の前記導電性リングを構成する導電性材料をアミン系薬液によって溶出させ、前記導電性リングが埋め込まれていた前記絶縁膜にスリットを形成する工程と、を含むことを特徴とする半導体装置の製造方法。

(付記9) 前記第1の導電部は、前記導電性リングを形成する前に、前記半導体基板の表層に形成することを特徴とする付記8に記載の半導体装置の製造方法。

(付記10) 前記第2の導電部を形成した後、前記導電性リングの側面をエッチングによって露出させる工程を含む付記8に記載の半導体装置の製造方法。

(付記11) 前記第2の導電部の形成する工程は、前記第2の導電部で前記導電性リングの上面の一部を覆うことを含む付記8に記載の半導体装置の製造方法。

(付記12) 前記導電性リングを複数形成する工程を含む付記8に記載の半導体装置の製造方法。

(付記13) 前記導電性リングから離れた位置に、前記第2の導電部を囲む第3の導電部を、前記第2の導電部と同時に形成する工程を含む付記8に記載の半導体装置の製造方

法。

(付記14) 前記第2の導電部を形成する工程は、前記第2の導電部の端面を前記導電性リングの端面に一致させることを含む付記8に記載の半導体装置の製造方法。

【符号の説明】

【0075】

1 ウェハ(半導体基板)

3 素子領域

16 n型拡散層(第1の導電部)

22 第1層間絶縁膜

33,48,58 導電性リング

45 第2層間絶縁膜

55 第3層間絶縁膜

63 ガードリング

65 導電層(第2の導電部)

70,117,118 スリットリング(スリット)

91 導電層(第3の導電部)

T1 トランジスタ(半導体素子)

【技術分野】

【0001】

本発明は、半導体装置及びその製造方法に関する。

【背景技術】

【0002】

半導体装置は、半導体基板上にマトリックス状に配置されたチップ領域に形成される。半導体回路形成後にチップ領域を切断するときは、チップ領域の間のスクライブライン領域で半導体基板をダイシングする。

【0003】

半導体基板をダイシングするときには、チップ領域の外周部分にクラックや欠けが発生することがある。半導体装置のチップの周辺部にクラックや欠けが生じると、外部から水分が浸入し易くなる。このために、半導体装置では、チップ領域の外周部分に、ガードリング(耐湿リング)を設けて、水分の浸入を防止している。

【0004】

ガードリングは、上下のリング状の金属層をプラグで接続させた構成を有する。このようなガードリングは、半導体装置の多層配線構造と同時に形成される。すなわち、回路の金属配線を形成するときに、同時にリング状の金属層がチップ領域の外周部分に形成される。そして、回路の配線を接続する導電性のプラグを形成するときに、上下のリング状の金属層を接続するプラグが同時に形成される。

【0005】

ところが、層間絶縁膜が低誘電率膜の場合には、ガードリングを形成しても、素子領域へのクラックの伝播を十分に防止できないことがあった。そこで、従来の半導体装置では、半導体基板上のチップ領域に、基板の表面に対して垂直方向に延びる中空溝を形成することが知られている。中空溝を形成するときは、最初に層間絶縁膜にリング状の溝を素子形成領域を覆うように形成する。リング状の溝には、配線材料を埋め込む。最上層の配線層を形成したら、最上層の上にフォトレジスト膜からなるマスクを形成する。マスクは、素子形成領域を覆い、素子形成領域の外側のリング状の溝に埋め込んだ配線材料を露出させる形状にする。この後、マスクを用いてリング状の溝に埋め込まれた配線材料をエッチングして除去する。これによって、リング状の中空溝が形成される。

【0006】

ここで、配線材料が銅の場合には、塩酸と過酸化水素水の混合液を使用して配線材料をエッチングする。バリアメタルにタンタルが用いられていた場合には、CF4ガスを使用したCDE(Chemical Dry Etching)、又はフッ化水素溶液を使用したウエットエッチングをする。リング状の溝には、配線層の数だけ、バリアメタルと配線材料が交互に配置されるので、エッチング工程では、塩酸と過酸化水素水の混合液によるエッチングと、CDEとを交互に行う。また、RIE(Reactive Ion Etching)法によって配線材料とバリアメタルを同時にエッチングすることもある。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特願2005−142262

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、従来の半導体装置では、リング状の溝から配線材料を除去するために、フォトレジスト膜を形成する工程と、フォトレジスト膜をパターニングしてマスクを形成する工程と、リング状の溝内の配線材料をエッチングによって除去する工程とを追加する必要があった。さらに、配線材料をエッチングによって除去する工程では、配線材料を除

去する工程と、バリアメタルを除去する工程とを交互に実施しなければならないことがあった。

【0009】

また、RIE法によって配線材料とバリアメタルを同時にエッチングする場合には、エッチング時間が長くなるので、生産性が低下する。さらに、レジスト膜に加えてハードマスクを形成するなどの追加工程が必要になる。

この発明は、このような事情に鑑みてなされたものであり、半導体装置の素子形成領域へのクラックなどの伝播を確実に防止することを目的とする。

【課題を解決するための手段】

【0010】

実施形態の一観点によれば、半導体基板と、前記半導体基板上の素子領域に形成された半導体素子と、前記半導体基板の上方に形成された絶縁膜と、前記絶縁膜に埋め込まれ、前記素子領域を囲むガードリングと、前記ガードリングを囲み、前記絶縁膜を表面から前記半導体基板に至るまで貫通するスリットと、前記半導体基板上に配置され、前記スリットの一方の端部に接続された第1の導電部と、前記半導体基板の上方に配置され、前記スリットの他方の端部に接続された第2の導電部と、を含むことを特徴とする半導体装置が提供される。

【0011】

また、実施形態の別の観点によれば、半導体基板上の素子領域に半導体素子を形成する工程と、前記半導体基板上に第1の導電部を形成する工程と、前記半導体基板の上方に絶縁膜を形成する工程と、前記絶縁膜中にガードリングを形成し、前記ガードリングで前記素子領域を囲む工程と、前記絶縁膜中に、前記第1の導電部に接続する導電性リングを形成し、前記導電性リングで前記カードリングを囲む工程と、前記導電性リングに接続される第2の導電部を前記導電性リングの上に形成する工程と、前記第1の導電層と前記第2の導電層の間の前記導電性リングを構成する導電性材料をアミン系薬液によって溶出させ、前記導電性リングが埋め込まれていた前記絶縁膜にスリットを形成する工程と、を含むことを特徴とする半導体装置の製造方法が提供される。

【発明の効果】

【0012】

ウェハのダイシング時に層間絶縁膜にクラックが発生してもスリットによってクラックの伝播が防止される。アミン系薬液を用いて導電性材料を溶出させる場合は、簡単にスリットを形成できる。

【図面の簡単な説明】

【0013】

【図1A】図1Aは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図1B】図1Bは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図1C】図1Cは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図1D】図1Dは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図1E】図1Eは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その5)である。

【図1F】図1Fは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その6)である。

【図1G】図1Gは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その7)である。

【図1H】図1Hは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その8)である。

【図1I】図1Iは、本発明の第1の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その9)である。

【図2A】図2Aは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図2B】図2Bは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図2C】図2Cは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図2D】図2Dは、本発明の第2の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図3A】図3Aは、本発明の第3の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図3B】図3Bは、本発明の第3の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図3C】図3Cは、本発明の第3の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図4A】図4Aは、本発明の第4の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図4B】図4Bは、本発明の第4の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図4C】図4Cは、本発明の第4の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【図4D】図4Dは、本発明の第4の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その4)である。

【図4E】図4Eは、本発明の第4の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その5)である。

【図5A】図5Aは、本発明の第5の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その1)である。

【図5B】図5Bは、本発明の第5の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その2)である。

【図5C】図5Cは、本発明の第5の実施の形態に係る半導体装置の製造工程の一例を示す断面図(その3)である。

【発明を実施するための形態】

【0014】

発明の目的及び利点は、請求の範囲に具体的に記載された構成要素及び組み合わせによって実現され達成される。

前述の一般的な説明及び以下の詳細な説明は、典型例及び説明のためのものであって、本発明を限定するためのものではない。

【0015】

(第1の実施の形態)

図面を参照して第1の実施の形態について説明する。

まず、図1Aに示す断面構造を得るまでの工程について説明する。

図1Aに示すように、シリコンなどのウェハ(半導体基板)1に、素子分離領域2を複数形成する。素子分離領域2は、シャロートレンチアイソレーション(STI)を使用する。STIは、ウェハ1の素子分離領域に溝を形成し、その中にシリコン酸化等の絶縁膜を埋め込むことにより形成される。なお、素子分離領域2は、STIに限られず、LOCOS(Local Oxidation of Silicon)法で形成した絶縁膜を使用しても良い。素子分離領域2によって、ウェハ1には、半導体素子や配線が形成される素子領域3と、素子領域3を囲むガード領域4と、ガード領域4を囲むスリット領域5と、スリット領域5を囲む格子状のスクライブライン領域6とに区画される。

【0016】

次いで、ウェハ1の表面に不純物をイオン注入し、ウェル11,12を形成する。例えば、素子領域3及びガード領域4には、ドーパント不純物としてn型不純物、例えばリンを導入してnウェル11を形成する。スリット領域5とスクライブライン領域6には、p型不純物、例えばボロンを導入してpウェル12を形成する。

【0017】

この後、ウェハ1上のトランジスタ活性領域の表面を熱酸化させてゲート絶縁膜13を形成する。ゲート絶縁膜13は、熱酸化によるシリコン酸化膜であり、その厚さは例えば1〜10nmである。また、ゲート絶縁膜13は、誘電率の高い材料で形成しても良い。

【0018】

この後、ウェハ1の全面に、非晶質又は多結晶のシリコン膜を形成する。シリコン膜の膜厚は、例えば約100nmとする。シリコン膜をパターニングすることにより、ゲート電極14を形成する。ここで、ゲート電極14は、金属材料から形成しても良い。

【0019】

続いて、ゲート電極14をマスクにしたイオン注入により、ゲート電極14の両側と、ガード領域4のウェハ表層にp型不純物、例えばボロンを導入して、p型拡散層15を形成する。また、スリット領域5とスクライブライン領域6のウェハ表層には、n型不純物、例えばリンを導入してn型拡散層16を形成する。n型拡散層16は、第1の導電部として機能する。

【0020】

この後に、ゲート電極14を含むウェハ1の上側全面に絶縁膜を形成する。絶縁膜としては、例えばCVD法により形成された酸化シリコン膜が用いられる。そして、絶縁膜をエッチバックしてゲート電極14の両側部分のみを残し、絶縁性サイドウォール17を形成。

【0021】

続いて、絶縁性サイドウォール17とゲート電極14をマスクにしてゲート電極14の両側に、不純物を再びイオン注入する。これにより、各ゲート電極14の側方のウェハ1にソース/ドレイン領域18(高濃度不純物拡散領域)が形成される。

さらに、ゲート電極14を含むウェハ1の上側全面に、金属膜をスパッタ法により形成する。金属膜は、例えば、コバルト膜やニッケル膜の高融点金属が好ましいが、比較的に融点が低い金属であっても良い。そして、この金属膜を加熱してシリコンと反応させる。これにより、ゲート電極14の上面と、ソース/ドレイン領域18上のそれぞれに、コバルトシリサイド層やニッケルシリサイド層といった金属シリサイド層19A、19Bが形成される。この熱処理によって、各ソース/ドレイン領域18が活性化されて低抵抗化する。このとき、スリット領域5とスクライブライン領域6のn型拡散層16の表層にも、金属シリサイド層19Cが形成される。

【0022】

その後に、素子分離領域2上などで未反応となっている金属膜をウエットエッチングによって除去する。ここまでの工程で、ウェハ1の活性領域ごとに、ゲート絶縁膜13,ゲート電極14、ソース/ドレイン領域18等によって構成されるトランジスタT1(半導体素子)が形成される。

【0023】

次に、トランジスタT1を含むウェハ1の全面にシリコン窒化膜21を例えば80nmの厚さに形成する。シリコン窒化膜21は、それぞれがプラズマCVD法によって形成する。続いて、シリコン窒化膜21の上に、第1層間絶縁膜22として、例えば、シリコン酸化(SiO2)膜をTEOS(tetra ethoxy silane)ガスを用いたプラズマCVD法によって1300nmの厚さに形成する。第1層間絶縁膜22の表面は、化学的機械研磨(CMP:Chemical Mechanical Polishing)法を用いて研磨し、ウェハ1の表面から第1層間絶縁膜22の表面までの膜厚を所定値、例えば約950nmに調整する。

【0024】

さらに、第1層間絶縁膜22の上にレジスト膜23を塗布した後、レジスト膜23にフォトリソグラフィによって開口部23Aを形成する。開口部23Aは、素子領域2のトランジスタT1のソース/ドレイン領域18の上方に複数形成される。また、開口部23Aは、ガード領域4の上方に2つ、スリット領域5の上方に1つ、それぞれ形成される。

【0025】

続いて、図1Bに示す断面構造を得るまでの工程について説明する。

レジスト膜23をマスクにしたドライエッチングにより、第1層間絶縁膜22、シリコン窒化膜21を順番に加工する。エッチング深さは、ソース/ドレイン領域17の高融点金属シリサイド層19Aに到達するまでとする。これにより、ソース/ドレイン領域18の上にコンタクトホール25が形成される。また、ガード領域4に第1のリング溝26が2重に形成される。第1のリング溝26は、素子領域3の周囲を連続して囲むリング形を有する。さらに、スリット領域5には、第2のリング溝27が1つ形成される。第2のリング溝27は、第1のリング溝26の周囲を連側して囲む連続したリング形を有する。第2のリング溝27の幅は、例えば0.22μmとする。

【0026】

続いて、図1Cに示す断面構造を得るまでの工程について説明する。

まず、コンタクトホール25内に、ソース/ドレイン領域17に電気的に接続される導電性プラグ31を形成する。また、これと同時に、第1のリング溝26内、及び第2のリング溝27内に、それぞれ導電性リング32及び導電性リング33を形成する。

【0027】

具体的には、最初に、コンタクトホール25及び第1、第2のリング溝26,27の内面に、密着層35をスパッタ法によって形成する。密着層は、30nmのチタン膜と、20nmの窒化チタン膜とを積層して形成する。さらに、密着膜35の上に、タングステン膜36をCVD法により成長させる。タングステン膜36は、各ホール25及び溝26,27に埋め込まれると共に、第1層間絶縁膜22の上方に、例えば300nmの厚さに成長させる。

【0028】

この後、第1層間絶縁膜22上に成長した余分なタングステン膜36及び密着膜35をCMP(Chemical Mechanical Polishing)法による研磨で除去する。この結果、コンタクトホール25に導電性プラグ31が形成される。これと同時に、第1及び第2のリング溝26,27のそれぞれに、導電性リング32,33が形成される。なお、導電性リング32,33の形状は、平面視で矩形のリングになる。

【0029】

次に、図1Dに示す断面構造を得るまでの工程について説明する。

導電性プラグ31及び導電性リング32,33を含む第1層間絶縁膜22の上に、下地層37を形成する。下地層37は、例えば、60nmの厚さのチタン膜と、30nmの厚さのチタン窒化膜をスパッタ法によって積層させて形成する。さらに、下地層37の上には、アルミニウム膜38をスパッタ法によって360nmの厚さに形成する。続いて、アルミニウム膜38上には、上地層39として、例えば5nmの厚さのチタン膜と、70nmの厚さのTiN膜をスパッタ法によって積層させて形成する。これによって、下地層37、アルミニウム膜38、上地層39が積層された導電性多層膜が形成される。

【0030】

この後、上地層39の上に不図示のレジスト膜を形成する。レジスト膜には、フォトリソグラフィによって開口部を形成する。レジスト膜をマスクにして、導電性多層膜をエッチングする。導電性プラグ31の上に、導電性多層膜からなる配線(導体パターン)41が形成される。また、導電性リング32の上には、ガード層(導体パターン)42が形成される。導電性リング33の上には、導体パターンは形成しない。これによって、1層目の配線層43が形成される。

【0031】

次に、図1Eに示す断面構造を得るまでの工程について説明する。図1E以降は、ガー

ド領域4、スリット領域5、及びスクライブライン領域6を拡大して示す。

まず、第1層間絶縁膜22上に、第2層間絶縁膜45を形成する。第2層間絶縁膜45は、例えば、高密度プラズマ(High Density Plasma;HDP)CVD法、又はTEOSガスを用いたプラズマCVD法によって形成されるシリコン酸化膜が用いられる。ここで、第2層間絶縁膜45は、HDP−CVD法によるシリコン酸化膜と、TEOSガスを用いたプラズマCVD法によるシリコン酸化膜の積層膜でも良い。この場合は、HDP−CVD法によるシリコン酸化膜を例えば720nmの厚さに形成した後、TEOSガスを用いたプラズマCVD法によるシリコン酸化膜を例えば1100nmの厚さに形成する。その後、第2層間絶縁膜45の表面は、CMP法による研磨で平坦化される。第2層間絶縁膜45の膜厚は、例えば、約1100nmとする。

【0032】

第2層間絶縁膜45には、ガード領域4に導電性リング47を2重に埋め込む。ガード領域4の導電性リング47は、下層のガード層42に接続される。同様に、スリット領域5には、導電性リング48を埋め込む。スリット領域5の導電性リング48は、下層の導電性リング33に接続される。導電性リング47,48の形状及び形成方法は、図1C及び図1Dを参照して説明したプロセスと同様である。また、不図示の素子領域3では、第2層間絶縁膜45に導電性プラグを埋め込む。

【0033】

さらに、導電性リング47の上には、ガード層49をリング形に形成する。また、ガード層49と同時に、素子領域3に不図示の配線を形成する。ガード層49及び配線の形状及び形成方法は、図1Eを参照して説明したプロセスと同様である。これによって、2層目の配線層50が形成される。

【0034】

さらに、2層目の配線層50の上に、3層目の配線層60を形成する。3層目の配線層60は、2層目の配線層50と同様のプロセスで形成する。ガード領域4のガード層49の上には、導電性リング56を形成する。導電性リング56上には、ガード層57を形成する。ガード層57の幅は、2つの導電性リング56の幅と、導電性リング56間の距離との和より大きい。このために、2つの導電性リング56は、ガード層57の下に隠れる。各導電性リング32,47,56、ガード層42,49,57によってガードリング63が形成される。

【0035】

また、スリット領域5には、導電性リング58が形成される。導電性リング58は、下方の導電性リング48に接続される。スリット領域5の導電性リング58の上には、導電層65(第2の導電部)を形成する。

【0036】

ここで、ガード層57及び導電層65の形成と同時に、不図示の素子領域3に配線を形成する。ガード層57、導電層65、及び不図示の配線を形成するときは、最初に、下地層37と、アルミニウム膜38と、上地層39とを積層した導電性多層膜を形成し、導電性多層膜上にポジ型のレジスト膜68を塗布する。レジスト膜68に対してフォトリソグラフィによって開口部を形成し、レジスト膜68をマスクにして導電性多層膜をドライエッチングする。

【0037】

導電層65は、導電性リング58の上面の一部を覆っており、さらに導電性リング58に対してガード領域4(素子領域3)側にオフセットして形成される。導電層65は、導電性リング58の一部を露出させ、後述する薬液処理時に薬液が導電性リング58に接触可能な開口部を導電性リング58に形成させている。従って、導電層65の外側の端面65Sと、導電性リング58の外側の端面58Sとの間の距離L1の下限値は、例えば5nmである。一方、距離L1の上限値は、導電層65と導電性リング58が電気的な接触を確保できる距離である。

【0038】

次に、図1Fに示す断面構造を得るまでの工程について説明する。

最初に、ガード層57上や、導電層65上に残ったレジスト膜68をウエットエッチングと、アッシングによって除去する。さらに、レジスト膜除去後のウェハ1をアミン系薬液に浸す。アミン系薬液としては、例えば富士フィルム社製のMS4092B、又はAshland−ACT社のACT−930シリーズが好ましい。アミン系薬液は、70℃に加熱し、ウェハ1は15分浸漬させる。

【0039】

ここで、スリット領域5において、導電層65は導電性リング58の一部を露出させる位置に形成されているので、アミン系薬液が導電性リング58の表面に供給される。これによって、n型拡散層16と導電層65とに挟まれた導電性リング33,48,58のタングステン、窒化チタン、チタンがアミン系薬液によって溶出する。タングステンなどの導電性材料は、導電性リング58の上面から溶出する。

【0040】

導電性リング33,48,58内の全ての導電性材料が、導電層65と層間絶縁膜55とによって形成される上部の開口を通って溶出すると、導電性リング33,48,58が埋め込まれていた空間に、スリットリング(リング状の溝)70が形成される。ここで、タングステン、窒化チタン、チタンが溶出するメカニズムとしては、例えば、電池作用に基づいた電気化学的反応が考えられる。

【0041】

続いて、図1Gに示すように、第3層間絶縁膜55上にカバー膜として、HDP−CVD法によるシリコン酸化膜71を例えば720nmの厚さに形成する。シリコン酸化膜71の上には、プラズマCVD法による窒化シリコン膜72を例えば1000nmの厚さに形成する。この後、窒化シリコン膜72上にレジスト膜73を形成する。レジスト膜73には、フォトリソグラフィによって開口部73Aを形成する。開口部73Aは、スリットリング70の内側の端面と一致する位置に形成される。レジスト膜73をマスクにしてススリット領域5の窒化シリコン膜72、シリコン酸化膜71、第3層間絶縁膜55、第2層間絶縁膜45の上部をエッチングによって除去する。

【0042】

これによって、図1Hに示すように、スリット領域5からスクラブ領域6にかけて開口部75が形成される。導電層65は、エッチングによって除去されない。また、スリットリング70は、側部の一部が開放される。

【0043】

次に、図1Iに示す断面構造を得るまでの工程について説明する。まずダイシングブレードを用いて、ウェハ1を複数のチップに切断する。ダイシングブレードによって、スクライブライン領域6上のウェハ1、各層間絶縁膜22,45が切断される。これによって、複数のチップが個片化され、半導体装置80が形成される。

【0044】

このとき、ダイシングブレードによる切断時に生じる応力で、層間絶縁膜22,34,にクラックが発生することがある。層間絶縁膜22,34で発生したクラックの進行は、スリットリング70によって上方に開放される。このために、クラックがガードリング63や、半導体回路に伝播することはない。

【0045】

以上、説明したように、この実施の形態では、ガードリング63の外側に、連続したリング状のスリットリング70を形成したので、半導体装置80の外側の端部でクラックや欠けが発生しても、スリットによってクラック等がガードリング63に伝播することが防止される。

【0046】

また、この実施の形態では、半導体ウェハ1の表層部分のn型拡散層16を第1の導電部とし、多層配線の最上層に形成した導電層65を第2の導電部とし、これら導電層に挟まれた導電性材料(チタン、チタン窒化膜、タングステン)をアミン系薬液による薬液処

理によって溶出させるようにした。マスクを用いて導電性材料をエッチングする領域を確定する工程が不要になり、製造効率が向上する。さらに、チタンや、チタン窒化膜、タングステンのように複数種類の導電性材料であっても、1回の薬液処理によって除去することができるので、複数種類のウエットエッチング工程を交互に実施する場合に比べて、製造効率が向上する。

【0047】

さらに、図1Eに示すように、導電層65を導電性リング58に対してオフセットして配置し、導電性リング58の上面の一部を露出させたので、薬液処理時に導電性リング58のチタン、チタン窒化膜、タングステンを確実に溶出させられる。これに対して、ガード領域4では、ガード層57が導電性リング56を完全に覆っているので、薬液処理しても導電性リング56のチタン、チタン窒化膜、タングステンが溶出することはない。

【0048】

(第2の実施の形態)

第2の実施の形態について図面を参照して説明する。第1の実施の形態と同じ構成要素には同一の符号を付している。また、第1の実施の形態と重複する説明は省略する。

図2Aに示すように、ガード領域4の第3層間絶縁膜55に、導電性リング56を埋め込み、スリット領域5に導電性リング58を埋め込む。この後、ガード層57と導電層65を形成する。導電層65の外側の端部65Sは、導電性リング58の外側の端部58Sと一致させる。即ち、導電性リング58は、導電層65の下に完全に隠れている。

【0049】

続いて、図2Bに示すように、第3層間絶縁膜55上にカバー膜として、HDP−CVD法によるシリコン酸化膜71と、プラズマCVD法による窒化シリコン膜72を順番に形成する。この後、窒化シリコン膜72上にレジスト膜73を塗布し、開口部73Aを形成する。

【0050】

さらに、図2Cに示すように、レジスト膜73をマスクにして、スリット領域5及びスクライブライン領域6の窒化シリコン膜72、シリコン酸化膜71、第3層間絶縁膜55、及び第2層間絶縁膜45の一部をエッチングによって除去する。エッチング後には、レジスト膜73をウエットエッチングと、アッシングによって除去する。スリット領域5とスクライブライン領域6に開口部75が形成される。

【0051】

ここで、導電層65は、導電性リング58の上面を覆い、かつ導電層65と導電性リング58の各々の端部65S,58Sが一致しているので、導電性リング58,48の外側の層間絶縁膜55,45の一部がエッチングによって除去される。従って、開口部75によって、導電性リング58の外側の側部58Sと、その下の導電性リング48の外側の端部48Sの一部が露出する。

【0052】

次に、図2Dに示すように、ウェハ1をアミン系薬液に浸すと、n型拡散層16と導電層65とに挟まれた導電性リング33,48,58を構成するタングステン、窒化チタン、チタンが、アミン系薬液によって溶出する。導電性材料は、導電性リング48,58の側部48S,58Sの露出部分から溶出する。導電性リング33,48,58内の全ての導電性材料が、開口部75側から溶出すると、導電性リング33,48,58が埋め込まれていた空間に、スリットリング(リング状の溝)70が形成される。この後、スクライブラインに沿ってウェハ1を切断すると、半導体装置が得られる。

【0053】

以上、説明したように、この実施の形態では、導電性リング48,58の外側の端部48S,58Sを露出させた後、アミン系薬液を用いた薬液処理するようにしたので、チタンや、チタン窒化膜、タングステンをより確実に溶出させられる。その他の効果は、第1の実施の形態と同様である。

【0054】

ここで、図1Eに示すように、導電層65は、導電性リング58の外側の端部58Sより内側に形成しても良い。これに対して、導電層65が導電性リング58の外側の端部58Sより外側に配置されると、エッチング時に導電性リング58の側面が露出しなくなるので好ましくない。

【0055】

(第3の実施の形態)

第3の実施の形態について図面を参照して説明する。前記の各実施の形態と同じ構成要素には同一の符号を付している。また、前記の各実施の形態と重複する説明は省略する。

図3Aに示すように、第3層間絶縁膜55上に、ガード層57と、導電層65と、導電層91を形成する。導電層65の外側の端部65Sは、導電性リング58の外側の端部58Sと一致させる。また、外側の導電層91は、導電層65を囲むようにリング状に形成されている。

【0056】

ここで、導電層91は、導電層64の端部65Sから所定距離、例えば最小抜き基準の間隔L2だけ離れた位置に形成されている。最小抜き基準の間隔L2は、それより短い距離で導電層を配置すると、導電層間の第3層間絶縁膜55をエッチングできなくなる距離をいう。最小抜き基準の間隔L2は、エッチング装置の性能等によって決まる値であって、例えば、0.24μmとする。

【0057】

2つの導電層65,91が最小抜き基準の間隔L2で配置されているので、導電層65,91の形状のばらつきを最小限に止めることができる。その結果、導電層65の外側の端部58Sの形状がだれてテーパ状になることを防止できる。即ち、導電層65の端部65Sが導電性リング58の端部58Sを越えて導電層91側に残ることがなくなる。

【0058】

続いて、図3Bに示す断面構造を得るまでの工程について説明する。

第3層間絶縁膜55上にシリコン酸化膜71と、窒化シリコン膜72を積層する。さらに、不図示のレジスト膜をマスクにして、スリット領域5及びスクライブライン領域6の窒化シリコン膜72、シリコン酸化膜71、第3層間絶縁膜55、第2層間絶縁膜45の一部をエッチングによって除去する。これによって、導電層91の外側に開口部93が形成される。さらに、2つの導電層65,91の間に開口する溝92がリング状に形成される。溝92によって、導電性リング58の外側の端面58Sと、その下の導電性リング48の外側の端面48Sの上部が露出する。導電層65の端面と導電性リング58の端面58Sとが一致しているので、溝92によって導電性リング48,58が確実に露出する。エッチング後には、レジスト膜をウエットエッチングと、アッシングによって除去する。

【0059】

続いて、図3Cに示すように、ウェハ1をアミン系薬液に浸し、n型拡散層16と導電層65とに挟まれた導電性リング33,48,58を構成するタングステン、窒化チタン、チタンをアミン系薬液によって溶出させる。導電性材料は、導電性リング48,58の側部48S,58Sの露出部分から溶出する。その結果、導電性リング33,48,58が埋め込まれていた空間に、スリットリング(リング状の溝)70が形成される。この後、スクライブラインに沿ってウェハ1を切断すると、半導体装置が得られる。

【0060】

以上、説明したように、この実施の形態では、導電性リング48,58の外側の端部48S,58Sを露出させた後、アミン系薬液を用いた薬液処理するようにしたので、チタンや、チタン窒化膜、タングステンをより確実に溶出させられる。導電層65の外側に、最小抜き基準の間隔L2だけ離れた位置に導電層91を形成したので、導電層65,91間に配置された第3層間絶縁膜55をエッチングして溝92を形成することができる。溝92を形成することで、導電性リング33,48,58内のチタンや、チタン窒化膜、タングステンをより確実に溶出させられる。その他の効果は、第1の実施の形態と同様である。

【0061】

(第4の実施の形態)

第4の実施の形態について図面を参照して説明する。前記の各実施の形態と同じ構成要素には同一の符号を付している。また、前記の各実施の形態と重複する説明は省略する。

図4Aに示すように、第1層間絶縁膜22に第1のリング溝26と、第2のリング溝27を形成する。第2のリング溝27は、2重に配列されている。各リング溝26,27には、チタン膜と窒化チタン膜を積層させた密着膜35を利用してタングステン膜36を埋め込んで導電性リング33A,33Bを形成する。導電性リング33A,33Bの幅は、例えば、0.22μmとし、導電性リング33A,33Bの間の距離は、例えば、0.26μm以下にする。

【0062】

図4Bに示すように、スリット領域5には、2重の導電性リング33A,33B,48A,48B,58A,58Bが形成される。さらに、第3層間絶縁膜55の上には、導電層95,96,97が形成される。導電層95(第2の導電部)は、2つの導電性リング58A,58Bを跨ぎ、導電層95の両端部のそれぞれから、導電性リング58Aの一部と、導電性リング58Bの一部が露出している。導電層96は、導電層95及び導電性リング58Aより内側に形成される。導電層97は、導電層95及び導電性リング58Bより外側に形成される。導電層95の幅は、例えば0.46μm以下とする。導電層96,97の幅は、0.24μm以下とする。導電性リング58Aは、導電層95の内側の端面95Uから例えば20nm露出している。同様に、導電性リング58Bは、導電層95の外側の端面95Sから例えば20nm露出している。中央の導電層95と、左右の導電層96,97との間は、距離L3だけ離れている。距離L3は、導電層86側と、導電層97側とで、異なる値にしても良いし、同じ値でも良い。距離L3は、例えば、0.24μmとする。

【0063】

続いて、図4Cに示す断面構造を得るまでの工程について説明する。

第3層間絶縁膜55上に、シリコン酸化膜71、窒化シリコン膜72を形成する。さらに、窒化シリコン膜72の上には、レジスト膜73を塗布によって形成する。フォトリソグラフィによってレジスト膜73に開口部73Bを形成する。開口部73Bは、スリット領域5において配線96より内側の位置から、スクライブライン領域6にかけて形成される。

【0064】

さらに、図4Dに示すように、レジスト膜73をマスクにして、スリット領域5及びスクライブライン領域6の窒化シリコン膜72、シリコン酸化膜71、第3層間絶縁膜55、第2層間絶縁膜45の一部をエッチングによって除去する。これによって、2つの配線95,96の間に開口する溝101がリング状に形成される。溝101によって、導電性リング48A,58Aの内側の端面48U,58Uが露出させられる。また、2つの配線95,97の間に開口する溝102がリング状に形成される。溝102によって、導電性リング48B,58Bの外側の端面48S,58Sが露出させられる。配線97の外側には、開口部103が形成される。エッチング後には、レジスト膜73をウエットエッチングと、アッシングによって除去する。

【0065】

続いて、図4Eに示す断面構造を得るまでの工程について説明する。

最初に、ウェハ1をアミン系薬液に浸漬させる。n型拡散層16と導電層65とに挟まれた導電性リング33A,48A,58Aを構成するタングステン、窒化チタン、チタンがアミン系薬液によって溶出する。これら導電性材料は、導電性リング48,58の側部48S,48U,58S,58Uの露出部分から溶出する。その結果、導電性リング33A,48A,58Aが埋め込まれていた空間に、スリットリング(リング状の溝)104が形成される。また、導電性リング33B,48B,58Bを構成するタングステン、窒化チタン、チタンがアミン系薬液によって溶出する。その結果、導電性リング33B,4

8B,58Bが埋め込まれていた空間に、スリットリング(リング状の溝)105が形成される。この後、スクライブラインに沿ってウェハ1を切断すると、半導体装置が得られる。

【0066】

以上、説明したように、この実施の形態では、スリットリング104,105が2重に配列されるので、クラックの伝播をより確実に防止できる。また、導電層95を挟むように一対の導電層96,97を配置したので、導電層95の形状をコントロールでき、溝101,102を確実に形成できる。その他の効果は、第3の実施の形態と同様である。

【0067】

(第5の実施の形態)

第5の実施の形態について図面を参照して説明する。前記の各実施の形態と同じ構成要素には同一の符号を付している。また、前記の各実施の形態と重複する説明は省略する。

図5Aに示すように、スリット領域5の第3層間絶縁膜55上に、導電層110,111を形成する。導電層110は、ガード領域4を囲むリング形状を有する。導電層110は、導電性リング58Aを覆い、その外側の端面110Sが導電性リング58Aの外側の端面58Sと一致する。導電層111は、導電層110を囲むリング形状を有する。導電層111は、導電性リング58Bを覆い、その内側の端面111Uが導電性リング58Bの内側の端面58Uと一致する。

【0068】

ここで、導電層110,111間の距離を最小抜き基準の間隔L2にすると、導電層110,111の端部がテーパ形状になることが防止され、導電層110,111の端面110S,110Uと、対応する導電性リング58A,58Bの端面58S,58Uとが不一致になることが防止される。

【0069】

続いて、図5Bに示す断面構造を得るまでの工程について説明する。

第3層間絶縁膜55上に、シリコン酸化膜71、窒化シリコン膜72を形成する。不図示のレジスト膜をマスクにして、スリット領域5及びスクライブライン領域6の窒化シリコン膜72、シリコン酸化膜71、第3層間絶縁膜55、第2層間絶縁膜45の一部をエッチングによって除去する。これによって、2つの導電層100,101の間に開口する溝115がリング状に形成される。溝115によって、導電性リング48A,58Aの外側の端面48S,58Sと、導電性リング48B,58Bの内側の端面48U,58Uが露出する。導電層111の外側には、開口部116が形成される。エッチング後には、レジスト膜73をウエットエッチングと、アッシングによって除去する。

【0070】

続いて、図5Cに示す断面構造を得るまでの工程について説明する。

最初に、ウェハ1をアミン系薬液に浸漬させる。n型拡散層16と導電層110とに挟まれた導電性リング33A,48A,58Aを構成するタングステン、窒化チタン、チタンがアミン系薬液によって溶出する。その結果、導電性リング33A,48A,58Aが埋め込まれていた空間に、スリットリング(リング状の溝)117が形成される。また、n型拡散層16と導電層111とに挟まれた導電性リング33B,48B,58Bを構成するタングステン、窒化チタン、チタンがアミン系薬液によって溶出する。その結果、その結果、導電性リング33B,48B,58Bが埋め込まれていた空間に、スリットリング(リング状の溝)118が形成される。この後、スクライブラインに沿ってウェハ1を切断すると、半導体装置が得られる。

【0071】

以上、説明したように、この実施の形態では、スリットリング117,118が2重に配列されるので、クラックの伝播をより確実に防止できる。また、一対の導電層110,111を配置したので、導電層1110,111の形状をコントロールでき、導電層110,111をマスクにしたエッチングによって溝115を確実に形成できる。その他の効果は、第3の実施の形態と同様である。

【0072】

前記の各実施の形態において、第1の導電部は、ウェハ1上に形成した導体膜であっても良い。

【0073】

ここで挙げた全ての例及び条件的表現は、発明者が技術促進に貢献した発明及び概念を読者が理解するのを助けるためのものであり、ここで具体的に挙げたそのような例及び条件に限定することなく解釈するものであり、また、明細書におけるそのような例の編成は本発明の優劣を示すこととは関係ない。本発明の実施形態を詳細に説明したが、本発明の精神及び範囲から逸脱することなく、それに対して種々の変更、置換及び変形を施すことができる。

【0074】

以下に、前記の実施の形態の特徴を付記する。

(付記1) 半導体基板と、前記半導体基板上の素子領域に形成された半導体素子と、前記半導体基板の上方に形成された絶縁膜と、前記絶縁膜に埋め込まれ、前記素子領域を囲むガードリングと、前記ガードリングを囲み、前記絶縁膜を表面から前記半導体基板に至るまで貫通するスリットと、前記半導体基板上に配置され、前記スリットの一方の端部に接続された第1の導電部と、前記半導体基板の上方に配置され、前記スリットの他方の端部に接続された第2の導電部と、を含むことを特徴とする半導体装置。

(付記2) 前記第1の導電部は、前記ガードリングから離れて配置されていることを特徴とする付記1に記載の半導体装置。

(付記3) 前記第2の導電部の少なくとも一部が、前記スリットの他方の端部上に配置されていることを特徴とする付記1又は付記2に記載の半導体装置。

(付記4) 前記第2の導電部を囲む第3の導電部を有し、前記第3の導電部と前記第2の導電部の間に、前記スリットが開口していることを特徴とする付記3に記載の半導体装置。

(付記5) 前記スリットは、前記ガードリングを連続して囲むことを特徴とする付記1乃至付記4のいずれか一項に記載の半導体装置。

(付記6) 前記スリットを複数有することを特徴とする付記1乃至付記5のいずれか一項に記載の半導体装置。

(付記7) 前記第1の導電部と、前記第2の導電部は、共に前記素子領域を連続して囲っている付記1に記載の半導体装置。

(付記8) 半導体基板上の素子領域に半導体素子を形成する工程と、前記半導体基板上に第1の導電部を形成する工程と、前記半導体基板の上方に絶縁膜を形成する工程と、前記絶縁膜中にガードリングを形成し、前記ガードリングで前記素子領域を囲む工程と、前記絶縁膜中に、前記第1の導電部に接続する導電性リングを形成し、前記導電性リングで前記カードリングを囲む工程と、前記導電性リングに接続される第2の導電部を前記導電性リングの上に形成する工程と、前記第1の導電部と前記第2の導電部の間の前記導電性リングを構成する導電性材料をアミン系薬液によって溶出させ、前記導電性リングが埋め込まれていた前記絶縁膜にスリットを形成する工程と、を含むことを特徴とする半導体装置の製造方法。

(付記9) 前記第1の導電部は、前記導電性リングを形成する前に、前記半導体基板の表層に形成することを特徴とする付記8に記載の半導体装置の製造方法。

(付記10) 前記第2の導電部を形成した後、前記導電性リングの側面をエッチングによって露出させる工程を含む付記8に記載の半導体装置の製造方法。

(付記11) 前記第2の導電部の形成する工程は、前記第2の導電部で前記導電性リングの上面の一部を覆うことを含む付記8に記載の半導体装置の製造方法。

(付記12) 前記導電性リングを複数形成する工程を含む付記8に記載の半導体装置の製造方法。

(付記13) 前記導電性リングから離れた位置に、前記第2の導電部を囲む第3の導電部を、前記第2の導電部と同時に形成する工程を含む付記8に記載の半導体装置の製造方

法。

(付記14) 前記第2の導電部を形成する工程は、前記第2の導電部の端面を前記導電性リングの端面に一致させることを含む付記8に記載の半導体装置の製造方法。

【符号の説明】

【0075】

1 ウェハ(半導体基板)

3 素子領域

16 n型拡散層(第1の導電部)

22 第1層間絶縁膜

33,48,58 導電性リング

45 第2層間絶縁膜

55 第3層間絶縁膜

63 ガードリング

65 導電層(第2の導電部)

70,117,118 スリットリング(スリット)

91 導電層(第3の導電部)

T1 トランジスタ(半導体素子)

【特許請求の範囲】

【請求項1】

半導体基板と、

前記半導体基板上の素子領域に形成された半導体素子と、

前記半導体基板の上方に形成された絶縁膜と、

前記絶縁膜に埋め込まれ、前記素子領域を囲むガードリングと、

前記ガードリングを囲み、前記絶縁膜を表面から前記半導体基板に至るまで貫通するスリットと、

前記半導体基板上に配置され、前記スリットの一方の端部に接続された第1の導電部と、

前記半導体基板の上方に配置され、前記スリットの他方の端部に接続された第2の導電部と、

を含むことを特徴とする半導体装置。

【請求項2】

前記第1の導電部は、前記ガードリングから離れて配置されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第2の導電部の少なくとも一部が、前記スリットの他方の端部上に配置されていることを特徴とする請求項1又は請求項2に記載の半導体装置。

【請求項4】

半導体基板上の素子領域に半導体素子を形成する工程と、

前記半導体基板上に第1の導電部を形成する工程と、

前記半導体基板の上方に絶縁膜を形成する工程と、

前記絶縁膜中にガードリングを形成し、前記ガードリングで前記素子領域を囲む工程と、

前記絶縁膜中に、前記第1の導電部に接続する導電性リングを形成し、前記導電性リングで前記カードリングを囲む工程と、

前記導電性リングに接続される第2の導電部を前記導電性リングの上に形成する工程と、

前記第1の導電層と前記第2の導電層の間の前記導電性リングを構成する導電性材料をアミン系薬液によって溶出させ、前記導電性リングが埋め込まれていた前記絶縁膜にスリットを形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項5】

前記第2の導電部を形成した後、前記導電性リングの側面をエッチングによって露出させる工程を含む請求項4に記載の半導体装置の製造方法。

【請求項6】

前記第2の導電部の形成する工程は、前記第2の導電部で前記導電性リングの上面の一部を覆うことを含む請求項4に記載の半導体装置の製造方法。

【請求項7】

前記導電性リングから離れた位置に、前記第2の導電部を囲む第3の導電部を、前記第2の導電部と同時に形成する工程を含む請求項4に記載の半導体装置の製造方法。

【請求項8】

前記第2の導電部を形成する工程は、前記第2の導電部の端面を前記導電性リングの端面に一致させることを含む請求項4に記載の半導体装置の製造方法。

【請求項1】

半導体基板と、

前記半導体基板上の素子領域に形成された半導体素子と、

前記半導体基板の上方に形成された絶縁膜と、

前記絶縁膜に埋め込まれ、前記素子領域を囲むガードリングと、

前記ガードリングを囲み、前記絶縁膜を表面から前記半導体基板に至るまで貫通するスリットと、

前記半導体基板上に配置され、前記スリットの一方の端部に接続された第1の導電部と、

前記半導体基板の上方に配置され、前記スリットの他方の端部に接続された第2の導電部と、

を含むことを特徴とする半導体装置。

【請求項2】

前記第1の導電部は、前記ガードリングから離れて配置されていることを特徴とする請求項1に記載の半導体装置。

【請求項3】

前記第2の導電部の少なくとも一部が、前記スリットの他方の端部上に配置されていることを特徴とする請求項1又は請求項2に記載の半導体装置。

【請求項4】

半導体基板上の素子領域に半導体素子を形成する工程と、

前記半導体基板上に第1の導電部を形成する工程と、

前記半導体基板の上方に絶縁膜を形成する工程と、

前記絶縁膜中にガードリングを形成し、前記ガードリングで前記素子領域を囲む工程と、

前記絶縁膜中に、前記第1の導電部に接続する導電性リングを形成し、前記導電性リングで前記カードリングを囲む工程と、

前記導電性リングに接続される第2の導電部を前記導電性リングの上に形成する工程と、

前記第1の導電層と前記第2の導電層の間の前記導電性リングを構成する導電性材料をアミン系薬液によって溶出させ、前記導電性リングが埋め込まれていた前記絶縁膜にスリットを形成する工程と、

を含むことを特徴とする半導体装置の製造方法。

【請求項5】

前記第2の導電部を形成した後、前記導電性リングの側面をエッチングによって露出させる工程を含む請求項4に記載の半導体装置の製造方法。

【請求項6】

前記第2の導電部の形成する工程は、前記第2の導電部で前記導電性リングの上面の一部を覆うことを含む請求項4に記載の半導体装置の製造方法。

【請求項7】

前記導電性リングから離れた位置に、前記第2の導電部を囲む第3の導電部を、前記第2の導電部と同時に形成する工程を含む請求項4に記載の半導体装置の製造方法。

【請求項8】

前記第2の導電部を形成する工程は、前記第2の導電部の端面を前記導電性リングの端面に一致させることを含む請求項4に記載の半導体装置の製造方法。

【図1A】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図1I】

【図2A】

【図2B】

【図2C】

【図2D】

【図3A】

【図3B】

【図3C】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図5A】

【図5B】

【図5C】

【図1B】

【図1C】

【図1D】

【図1E】

【図1F】

【図1G】

【図1H】

【図1I】

【図2A】

【図2B】

【図2C】

【図2D】

【図3A】

【図3B】

【図3C】

【図4A】

【図4B】

【図4C】

【図4D】

【図4E】

【図5A】

【図5B】

【図5C】

【公開番号】特開2013−55183(P2013−55183A)

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願番号】特願2011−191525(P2011−191525)

【出願日】平成23年9月2日(2011.9.2)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

【公開日】平成25年3月21日(2013.3.21)

【国際特許分類】

【出願日】平成23年9月2日(2011.9.2)

【出願人】(308014341)富士通セミコンダクター株式会社 (2,507)

【Fターム(参考)】

[ Back to top ]