Fターム[5F038AC02]の内容

Fターム[5F038AC02]の下位に属するFターム

半導体領域、拡散領域、不純物など (467)

平面形状、分割電極など (266)

多結晶電極、金属電極 (1,364)

Fターム[5F038AC02]に分類される特許

1 - 20 / 109

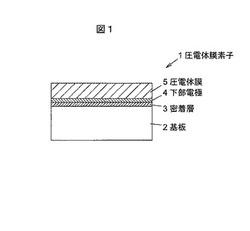

圧電体膜素子の製造方法、圧電体膜素子及び圧電体デバイス

【課題】ドライエッチングにより微細加工を行った場合に、エッチング残渣が少なく、後工程における信頼性が高い非鉛の圧電体膜素子の製造方法、圧電体膜素子及び圧電体デバイスを提供する。

【解決手段】圧電体膜素子1の製造方法は、基板2上に、組成式(K1−xNax)NbO3で表されるペロブスカイト構造を有する非鉛のアルカリニオブ酸化物系化合物からなる圧電体膜5を形成する工程と、圧電体膜5を、フッ素系反応ガスを含む雰囲気中で低圧プラズマを用いてエッチングを行う工程とを含む。

(もっと読む)

容量素子および半導体装置

【課題】容量素子のQ値(Quality Factor)特性を向上する。

【解決手段】容量素子は、互いに対向する一対の電極EL10、EL20と、一対の電極の一方の電極に設けられ、一方の電極の両端部から間隔を置いて配置された第1端子部とTE10、一対の電極の他方の電極に設けられ、他方の電極の両端部から間隔を置いて配置された第2端子部とTE20を有している。

(もっと読む)

容量素子及びその製造方法並びに半導体集積回路

【課題】高い周波数帯での導体損失の増加を抑え、幅広い周波数範囲で低損失な動作を実現することが可能な容量素子及びその製造方法並びに半導体集積回路を提供すること。

【解決手段】本発明の容量素子10は、第1電極11と、第1電極11上に設けられた誘電体層12と、誘電体層12上に設けられた第2電極13とから構成されている。容量素子10は、誘電体層12を第1電極11と第2電極13とにより挟むようにしたサンドイッチ構造になっており、第2電極13の外表面に凹凸が設けられている。

(もっと読む)

光電変換装置

【課題】電圧降下が小さい整流素子を得ること、及び、コンバータ回路の作製コストを抑制することを課題とする。

【解決手段】光電変換素子と、当該光電変換素子の出力を昇圧又は降圧し、スイッチング素子及び整流素子を有するコンバータ回路と、を有する光電変換装置において、当該スイッチング素子として、ノーマリオフの第1の酸化物半導体トランジスタと、当該整流素子として、ダイオード接続されたノーマリオンの第2の酸化物半導体トランジスタとを有する光電変換装置に関する。

(もっと読む)

半導体装置およびその製造方法

【課題】経年劣化および分極反転の繰り返しによる劣化の少ない強誘電体キャパシタまたは高誘電率を有する誘電体キャパシタを提供する。比抵抗の増大なしに信頼性の高い配線を有する半導体装置を提供する。

【解決手段】半導体基板表面上に形成された電極を含み、前記電極が、配向性を有する導電体層からなり、前記電極に加え、

下式

M1xM21-x

M1:Au、Pt、Ir、Pd、Os、Re、Rh、Tu、Cu、Co、Fe、Ni、V、Cr

M2:Ta、Ti、Zr、Hf、W、Y、Mo、Nb

で表されるアモルファスまたは微結晶からなるバリア層を含むことを特徴とする。

(もっと読む)

キャパシタ素子とキャパシタ素子の製造方法および半導体装置

【課題】リーク電流の低減と静電容量の増加の両立を実現するキャパシタ素子とキャパシタ素子の製造方法および半導体装置を提供する。

【解決手段】本発明のキャパシタ素子は、少なくとも上面が第一の窒化金属からなる第一電極と、酸化ジルコニウム膜からなる容量絶縁膜と、ボロン、アルミニウム、ガリウムのいずれかが不純物としてドープされた酸化亜鉛膜からなる第一のバリア膜と、少なくとも下面が第二の窒化金属からなる第二電極と、がこの順で積層されてなることを特徴とする。

(もっと読む)

半導体装置およびその製造方法

【課題】MIM容量素子形成時に生じる異常放電による容量絶縁膜の絶縁破壊を抑えることができて、高容量密度のMIM容量素子を得る。

【解決手段】半導体基板2上に、下部電極4−容量絶縁膜5−上部電極6からなるMIM容量素子1を有する半導体装置であって、上部電極4を構成する上部電極用金属膜は容量絶縁膜5との界面が、有機金属気相成長法(MOCVD)によりプラズマを用いないで堆積したアモルファス状のTiN膜などの金属窒化膜で構成されている。

(もっと読む)

強誘電体層を有する層構造体、および、層構造体の製造方法

【課題】基板と白金層と強誘電体層とを有する層構造体において、白金層と基板の間の接着性を改善する層構造体を提供する。

【解決手段】基板Sと、白金層PSと、白金層PS上に形成された強誘電体層FSとを有しており、基板Sの表面OSは二酸化ケイ素を含み、基板Sと白金層PSとの間にアモルファス酸化アルミニウムから成る中間層ZSが設けられる。この中間層ZSにより強誘電体層FSのモルフォロジーが改善され、層構造体の均一性が保証される。

(もっと読む)

半導体装置、半導体装置の製造方法および基板処理装置

【課題】低コストで必要な仕事関数及び耐酸化性を有する金属膜を備えた半導体装置を提供する。

【解決手段】基板上に形成された絶縁膜と、絶縁膜に隣接して設けられた金属膜と、を有し、金属膜は、第1の金属膜と第2の金属膜との積層構造を有しており、第1の金属膜は第2の金属膜よりも耐酸化性が高い物質で構成され、第2の金属膜は4.8eVよりも高い仕事関数を有する第1の金属膜とは異なる物質で構成され、第1の金属膜は第2の金属膜と絶縁膜との間に設けられている。

(もっと読む)

半導体装置

【課題】MIM構造の容量素子を有する半導体装置において、容量素子の信頼性を向上させることのできる技術を提供する。

【解決手段】下部電極DEと、容量絶縁膜CELと、上部電極UEとからなる容量素子において、下部電極DEを、半導体基板1の主面上の絶縁膜に形成された電極溝17aの内部に埋め込まれた金属膜によって構成し、上部電極UEを、TiN膜(下層金属膜)22と、TiN膜(下層金属膜)22上に形成されたTi膜(キャップ金属膜)23との積層膜によって構成する。

(もっと読む)

有機発光表示装置及びその製造方法

【課題】効果的に不純物がドーピングされた多結晶シリコン膜をキャパシタの電極として使用した有機発光表示装置を提供する。

【解決手段】本発明の実施例による有機発光表示装置は、基板本体、前記基板本体上の同一層に形成された半導体層及び第1キャパシタ電極、前記半導体層及び前記第1キャパシタ電極上に形成されたゲート絶縁膜、前記ゲート絶縁膜を間において前記半導体層上に形成されたゲート電極、そして前記ゲート絶縁膜を間において前記第1キャパシタ電極上に形成されて、前記ゲート電極と同一層に形成された第2キャパシタ電極を含む。そして、前記第1キャパシタ電極及び前記半導体層は、各々不純物がドーピングされた多結晶シリコン膜を含み、前記第2キャパシタ電極は前記ゲート電極より相対的に厚さが薄い。

(もっと読む)

スタック型MIMキャパシタおよびその製造方法

【課題】多くのマスク数を必要とせずに、電極材料やMIMスタック層数の制限が少なくすることのできるスタック型MIMキャパシタおよびその製造方法を提供する。

【解決手段】

スタック型MIMキャパシタ10のMIM電極13A,13Bには、MIM電極13Aの層の表面に小空孔15と大空孔16の2種類の空孔が、表面上において2次元に形成される。さらに、半導体基板11上に形成された保護膜12上に、異なる形状を持つMIM電極13A,13Bを交互に重ね、誘電体膜14を挟んでスタック型MIM構造を形成する。

(もっと読む)

半導体装置

【課題】一定の静電容量を確保すると同時に、小型化を図ることが可能なキャパシタを備える半導体装置を提供する。

【解決手段】半導体装置は、金属膜を含むキャパシタ下部電極3aと、キャパシタ下部電極3aの上部表面上に配置され、キャパシタ下部電極3aの厚みより薄い厚みを有する誘電体膜4aと、誘電体膜4a上に配置され、金属膜を含むキャパシタ上部電極6aと、キャパシタ上部電極6aと同一レベルの層により構成される下部配線部分6bと、下部配線部分6b上に配置される層間絶縁膜8と、層間絶縁膜8上に配置される上部配線部分12bとを備える。

(もっと読む)

半導体装置およびその製造方法

【課題】新たな工程を追加することなく信頼性の高い半導体装置およびその製造方法を提供すること。

【解決手段】半導体素子を表面側に有する基板11と、半導体素子を覆うように基板11に積層された第1絶縁膜12と、第1絶縁膜12を厚さ方向に貫通する貫通孔の内面に積層されたバリア導電層13を介して貫通孔内に埋め込まれたコンタクトプラグ14と、第1絶縁膜12の表面に形成されてコンタクトプラグ14を介して半導体素子と電気的に接続された1種類以上の機能層とを備え、前記機能層は、バリア導電層13の材料と同じ材料からなり第1絶縁膜12の表面の所定領域に積層された第1バリア導電層13と、第1バリア導電層13上に、直接積層されるか、または第2絶縁膜15を介して積層されるか、またはそれらの両方の形態で積層された第2バリア導電層16と、第2バリア導電層16に積層された導電層17とを有してなることを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】容量素子を構成する第1電極及び第2電極を形成するためのリソグラフィ工程で重ね合わせズレが生じた場合にも容量ばらつきを抑制できる半導体装置を提供する。

【解決手段】複数の配線層L1〜L5のそれぞれは、絶縁膜103〜106と、当該絶縁膜中に相互に離隔し且つ向かい合うように埋め込まれた第1電極101及び第2電極102とを有する。一の配線層の第1電極101と、その上方又は下方に設けられた他の配線層の第2電極102とは相互に向かい合うように配置されている。一の配線層の第1電極101の幅と、他の配線層の第2電極102の幅とは異なっている。

(もっと読む)

容量素子、容量素子の設計方法および容量素子を含む集積回路装置

【課題】容量値としての変動(ばらつき)が細密構造に比べて小さいデバイス構造を設計する。

【解決手段】多層配線の各配線に関するパラメータを統計的処理で変化させた複数のデバイス構造に対する総容量値、線間容量値および層間容量値を算出する。次いで、複数のデバイス構造の中から、デバイス構造間における総容量値の差分が例えば0.1以下でかつ総容量値に対する線間容量値の比と総容量値に対する層間容量値の比の差分が例えば0.01以内のデバイス構造を特定する。そして、この特定したデバイス構造についてのパラメータを、容量素子を形成する多層配線の各配線のパラメータとする。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】下部電極の表面に絶縁性の酸化膜が形成されることを抑制することができる半導体装置を提供する。

【解決手段】この半導体装置は、基板100、基板100上に形成された絶縁膜210、及び容量素子300を備える。容量素子300は、絶縁膜210上に形成されたシリンダ型の下部電極310、誘電体膜320、及び上部電極330を備える。誘電体膜320は、下部電極310の底面上、内側面上、及び外側面上それぞれに形成されている。すなわち下部電極310の底面、内側面、及び外側面それぞれが容量の増大に寄与する。そして下部電極310の底面、内側面、及び外側面それぞれにおいて、内部から表面に向かって窒素濃度が上昇している。

(もっと読む)

IC内蔵コンデンサ容量補正装置

【課題】本発明は、IC内蔵コンデンサ容量補正装置に関し、簡易な回路構造でIC内蔵コンデンサの容量を精度良いものに補正することにある。

【解決手段】集積回路外に設けられ、該集積回路の外部端子に接続される外付けコンデンサと、その外付けコンデンサに電荷を注入する電流源と、集積回路内に設けられた内蔵コンデンサ及び抵抗からなり、電流源により外付けコンデンサに電荷が注入される際の該外付けコンデンサの電位の変化傾きを検出する微分回路と、を設ける。そして、その微分回路により検出される変化傾きと基準値との差を増幅することにより、所定回路の有する内蔵コンデンサの容量バラツキを検出し、その検出される容量バラツキに基づいて、該所定回路の有する内蔵コンデンサの容量を補正する。

(もっと読む)

ルテニウム膜の成膜方法

【課題】Ru膜を誘電体膜上に成膜する際に、インキュベーション時間を短縮し、高い密度で核生成を生じさせることにより、高品質のルテニウム膜の成膜を可能とする。

【解決手段】ルテニウム膜の成膜方法は、誘電体膜を担持する被処理基板表面近傍にプラズマを発生させ、前記誘電体膜表面を前記プラズマで改質する工程と、前記改質された誘電体膜表面に、ルテニウムの有機金属錯体を不活性キャリアガスとともに供給し、前記有機金属錯体を分解させることにより、前記誘電体膜上にルテニウム膜を成膜する工程と、を含むことを特徴とする。

(もっと読む)

半導体装置及びその製造方法

【課題】電気的特性に優れ、配線レイアウトへの影響が小さい容量素子を備える半導体装置を提供する。

【解決手段】半導体基体11上に第1の導電層21、第1の誘電層22、第2の導電層23、第2の誘電層24、及び、第3の導電層25から構成される容量素子を構成する。また、容量素子に、第1の開孔部33と、第2の開孔部34が形成され、第1の開孔部33の側壁には第1の絶縁層16が設けられ、第1の絶縁層16の内側に第1の導電層21と電気的に接続する第1の導電プラグ26が設けられる。また、第2の開孔部34の側壁に第2の絶縁層17が設けられ、第2の絶縁層17の内側に第2の導電層23と電気的に接続する第2の導電プラグ27が設けられる。また、第3の導電層25に電気的に接続する第3の導電プラグ28が設けられる。

(もっと読む)

1 - 20 / 109

[ Back to top ]