Fターム[5F038AC04]の内容

半導体集積回路 (75,215) | キャパシタ (4,915) | 構造 (2,824) | 電極領域又は電極部分 (2,206) | 平面形状、分割電極など (266)

Fターム[5F038AC04]に分類される特許

1 - 20 / 266

三次元配置部品を有する化合物半導体集積回路

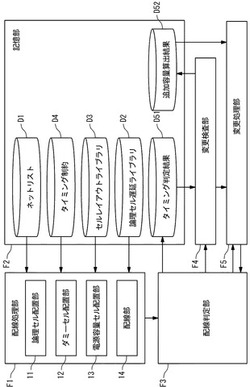

半導体集積回路のレイアウト設計方法

【課題】SETUP時間とHOLD時間のどちらも満足させるタイミングの調整が可能な技術を提供する。

【解決手段】半導体集積回路の配置配線レイアウトを決定した後に、所定の信号線を伝搬するデータのタイミング情報に基づいて、タイミング違反を有する違反データの遅延情報を抽出する。その抽出された遅延情報に基づいて、タイミング違反を解消するための追加すべき容量値を算出する。また、違反データを伝搬する配線のレイアウト配置情報に基づいて、違反データを伝搬する配線の近傍の電源容量セルを検出する。また、算出された容量値に基づいて、検出された電源容量セルを、電源容量セルとレイアウト外形・電源/GND配線配置位置が同じ調整容量セルに置き換える。そして、置き換えた調整用容量セルのゲートと違反データを伝搬する配線とを接続して再配線を実行する。

(もっと読む)

集積電子構成要素を有する半導体発光装置

【課題】集積電子構成要素を含む半導体発光装置を提供する。

【解決手段】シリコンダイオード、抵抗体162、コンデンサ164、及び誘導子のような1つ又はそれよりも多くの回路要素が、半導体発光装置の半導体構造110と装置を外部構造に接続するのに使用される接続層との間に配置される。半導体構造に対するn接点114は、複数のバイアにわたって分散され、これは、1つ又はそれよりも多くの誘電体層によってp接点112から隔離されている。回路要素は、接点−誘電体層−接続層のスタックに形成される。

(もっと読む)

不揮発性半導体記憶装置

【課題】容量素子が占有する回路面積の増大を抑制する。

【解決手段】不揮発性半導体記憶装置は、メモリセル領域、第1電極、及び第2電極を有する。メモリセル領域は、基板上に形成され、複数のメモリセルが積層される。第1電極は、基板上に複数の導電層が積層されて、容量素子の一方の電極として機能する。第2電極は、基板上に複数の導電層が積層されて、第1電極と基板に水平な方向において分離され、容量素子の他方の電極として機能する。

(もっと読む)

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

安定化回路を備える半導体装置

【課題】ガン発振に伴う負性抵抗を抑制し、安定的かつ高効率の電力増幅を得るための安定化回路を備える半導体装置を提供する。

【解決手段】基板10と、基板上に配置され、ガン発振である高周波負性抵抗発振の発振周波数において負性抵抗を生ずる能動素子140と、基板上に配置され、能動素子のドレイン端子電極と出力端子との間に接続され、負性抵抗の絶対値に等しい抵抗値を有する抵抗Rと、抵抗Rに並列に接続され、高周波負性抵抗発振の発振周波数に同調するインダクタンスLとキャパシタンスCからなるタンク回路とからなる安定化回路120とを備え、安定化回路120は、発振周波数に、インダクタンスLとキャパシタンスCからなる共振周波数を同調することによって、発振周波数において、抵抗Rによって負性抵抗をキャンセルする半導体装置。

(もっと読む)

半導体装置

【課題】半導体基板上においてキャパシタが占める面積の増大を抑えつつ、キャパシタ全体の容量を増やすことを可能とした半導体装置を提供する。

【解決手段】P型のシリコン基板1と、シリコン基板1に設けられたN−領域11と、N−領域11上に設けられた第1の誘電体膜15と、第1の誘電体膜15上に設けられた第1の電極17と、第1の電極17の上面に設けられた第2の誘電体膜19と、第1の電極17の側面に設けられた第3の誘電体膜21と、P型のシリコン基板1のうちのN−領域11に隣接する隣接領域5上に設けられた第4の誘電体膜23と、第2の誘電体膜19と第3の誘電体膜21及び第4の誘電体膜23を覆うようにシリコン基板1の上方に設けられた第2の電極24と、を有する。

(もっと読む)

多層膜キャパシタ構造及び方法

【課題】多くの電極あるいは電極の組合せのいずれにも簡単に接近できる改良された膜キャパシタ構造の提供。

【解決手段】多層膜キャパシタ構造が、モノリシック基板上の下部電極層、下部電極上に敷かれている膜電極及び誘電体材料の対からなる中間層、及び中間層対の上に敷かれている膜電極及び膜誘電体の対からなる上部層を有する。この構造は、デバイスの全周縁にわたって、それぞれの電極層がその上の層の周縁の外側まで側方に広がる、

メサ形状を有することが望ましい。電極をいかなる組合せでも接続でき、いかなる所望の回路接続もできるように、各電極層はその突き出している縁にビアを通して接続できる上部表面を有する。望ましければ、単層キャパシタ構造をフィルタに最適化し得るように、誘電体材料に異なる周波数特性をもたせることができる。

(もっと読む)

電磁波干渉フィルタ

【課題】小型化が可能な電磁波干渉フィルタを提供すること。

【解決手段】実施形態に係る電磁波干渉フィルタ10は、半導体基板11の表面上に形成された抵抗R、およびこの抵抗Rの両端にそれぞれ電気的に接続された一対のキャパシタC、をそれぞれ具備する複数の電磁波干渉フィルタ回路12と、これらの電磁波干渉フィルタ回路12間の半導体基板11に埋め込み形成された素子分離層13と、を具備する。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】実際の強誘電体メモリセルについて疲労特性を直接に測定する試験方法を含む半導体装置の製造方法を提供する。

【解決手段】半導体装置の製造方法は、基板上に形成された強誘電体キャパシタの疲労特性の面内分布を取得する第1の工程と、前記面内分布に基づいて、半導体装置を製造する第2の工程と、を含み、前記第2の工程は、前記半導体装置が形成される基板上に複数の強誘電体キャパシタを形成し、前記第1の工程で取得された疲労特性の面内分布から、前記半導体装置が形成される基板上の特定領域を指定し、前記特定領域に形成された前記強誘電体キャパシタについて疲労特性を測定し、前記特定領域の強誘電体キャパシタについて測定した前記疲労特性に基づき、前記特定領域の強誘電体キャパシタについて良否判定を行い、前記良否判定の結果が良であれば、前記複数の強誘電体キャパシタの全てについて良と判定する。

(もっと読む)

半導体装置及びその製造方法

【課題】容量値及びその変化量が大きく且つQ値の高い可変容量素子を備える半導体装置及びその製造方法を実現する。

【解決手段】半導体装置は、可変容量素子を備え、当該可変容量素子は、半導体基板11上に形成された下部電極13と、下部電極13上に形成された容量絶縁膜14と、容量絶縁膜14上に形成された上部電極15とを備える。上部電極15は、容量絶縁膜14上に位置する低濃度不純物層15aと、低濃度不純物層15a上に位置し且つ低濃度不純物層15aよりも不純物濃度が高い高濃度不純物層15bとを有する。

(もっと読む)

MIMキャパシタとその製造方法、並びに半導体装置

【課題】堆積界面のない誘電体膜を有するMIMキャパシタとその製造方法、並びにそのようなMIMキャパシタを備えた半導体装置を提供する。

【解決手段】MIMキャパシタは、半導体基板と、該半導体基板の上方に形成された下部電極16と、該下部電極の上に形成された誘電体膜18と、該誘電体膜の上に該下部電極と重なるように形成された上部電極20と、を備える。そして、該下部電極の上面と側面は、該下部電極の中央部分の厚さよりも大きい曲率半径を持つ第1曲面で、角部が形成されないように接続され、該下部電極は、該下部電極の側面に該下部電極の中央部分の厚さよりも大きい曲率半径を持つ第2曲面を形成することにより、該下部電極の外周に向かうほど薄く形成されている。

(もっと読む)

可変容量装置

【課題】 回路の小型化と消費電力の低減が可能な可変容量装置を提供する。

【解決手段】 容量検出回路31は、可変容量素子2の駆動容量C1のキャパシタンス値に応じた検出信号Sxと、基準となる基準信号Syとを出力する。駆動電圧制御回路21は、検出信号Sxと基準信号Syとを比較し、この比較結果に応じて駆動電圧Vcontを制御し、駆動容量C1を増加または減少させる。駆動容量C1の一端側には駆動電圧Vcontが印加され、他端側には容量検出回路31の検出用電流回路33から検出用電流Icontが周期的に入力される。このため、駆動容量C1が検出用電流回路33に接続されると、駆動容量C1のキャパシタンス値と検出用電流Icontの大きさとに応じて、駆動容量C1の他端側の電圧が上昇し、この電圧に応じた検出信号Sxが出力される。

(もっと読む)

縦構造キャパシタを備える半導体装置

【課題】縦構造キャパシタの剥離を防止し、チップサイズの増加を抑制した半導体装置を提供する。

【解決手段】半導体装置には、第1の回路の機能素子として使用される第1の縦構造キャパシタと、第2の回路の機能素子として使用され、第1の縦構造キャパシタよりも容量値の大きい第2の縦構造キャパシタと、が含まれている。半導体装置では、第1の縦構造キャパシタを、第2の縦構造キャパシタに隣接、又は、包含させるようにレイアウトする。

(もっと読む)

半導体構造

【課題】多くの半導体装置に必要な低温処理と両立しない高温操作を必要とするような欠点がない、半導体構造を提供することを目的とする。

【解決手段】下部誘電層(151)へ接合された基板(103)、および、下部電極(121)を通じて前記下部誘電層(151)と接合される垂直方向半導体装置(111)を含む半導体構造であって、前記垂直方向半導体装置(111)は、n+−p−n+層(124)を有する隔離構造(135)を含む。

(もっと読む)

静電容量素子

【課題】 生産性に優れる温度補償型の静電容量素子を提供する。

【解決手段】 静電容量素子10は、基板20と、該基板20の上に位置する第1コンデンサ30と、基板20の上に位置し且つ第1コンデンサ30と電気的に並列接続されている第2コンデンサ40とを有する。第1コンデンサ30は、第1下部電極31と、第1誘電体32と、第1上部電極33とで構成される。第2コンデンサ40は、第1下部電極31と組成の異なる第2下部電極41と、第1誘電体32と同組成である第2誘電体42と、第2上部電極43とで構成される。第1コンデンサ30の温度が上昇する際に変化する静電容量と、第2コンデンサ40の温度が上昇する際に変化する静電容量とで正負が異なっている。

(もっと読む)

半導体装置及びその製造方法

【課題】半導体装置の製造後におけるチャージ蓄積用素子からのチャージの放電を防止してデバイス機能素子のチャージダメージを低減する半導体装置及びその製造方法を提供する。

【解決手段】 半導体基板上に形成されたデバイス機能素子と、半導体基板上に形成されたチャージ蓄積用素子と、半導体基板上に形成され、デバイス機能素子とチャージ蓄積用素子との間に接続され、電気的に書き換え可能な不揮発性メモリトランジスタにより形成された分離用素子とを有する。

(もっと読む)

静電容量素子

【課題】 生産性に優れる温度補償型の静電容量素子を提供する。

【解決手段】 静電容量素子10は、基板20と、基板20の上に位置する第1コンデンサ30と、基板20の上に位置して第1コンデンサ30と電気的に並列接続されている第2コンデンサ40とを有し、第1コンデンサ30は、第1下部電極31と第1誘電体32と第1上部電極33とで構成され、第2コンデンサ40は、基板20側から順に第1下部電極31と異なる材料からなる第1層41xと、第1下部電極31と同じ材料からなる第2層41yとが積層されてなる第2下部電極41と、第1誘電体32と同じ組成の材料からなる第2誘電体42と、第2上部電極43とで構成され、温度が上昇する際の第1コンデンサ30の静電容量の変化量と第2コンデンサ40の静電容量の変化量とで変化の正負が異なっている。

(もっと読む)

容量素子および半導体装置

【課題】容量素子のQ値(Quality Factor)特性を向上する。

【解決手段】容量素子は、互いに対向する一対の電極EL10、EL20と、一対の電極の一方の電極に設けられ、一方の電極の両端部から間隔を置いて配置された第1端子部とTE10、一対の電極の他方の電極に設けられ、他方の電極の両端部から間隔を置いて配置された第2端子部とTE20を有している。

(もっと読む)

キャパシタおよび半導体装置

【課題】キャパシタの電極として機能する配線の延伸方向への電流供給を容易とすること。

【解決手段】第1金属層12と、前記第1金属層の膜厚方向に離間して設けられ、第1方向および前記第1方向に交差する第2方向に配列された複数の孔36を備えた第2金属層14と、前記第2金属層の膜厚方向で前記第1金属層とは反対側に離間して設けられ、前記第1方向および前記第2方向とは異なる方向に延伸し、第1配線と第2配線とが交互に設けられた複数の第1配線16aおよび複数の第2配線16bと、前記複数の第1配線と前記複数の第2配線との間に設けられた誘電体膜26と、前記複数の第1配線を、それぞれ前記複数の孔を通過し前記第1金属層に電気的に接続する複数の第1ビア配線32と、前記複数の第2配線を、それぞれ前記第2金属層に電気的に接続する複数の第2ビア配線34と、を具備するキャパシタ。

(もっと読む)

1 - 20 / 266

[ Back to top ]