Fターム[5F038AC16]の内容

Fターム[5F038AC16]に分類される特許

1 - 20 / 179

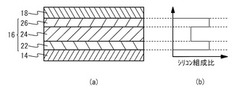

容量素子

【課題】電極と誘電体部との密着性を良好なものとすること。

【解決手段】本発明は、上部電極18と、下部電極14と、上部電極18と下部電極14との間に配置され、窒化シリコン又は酸化アルミニウムからなる第1の膜22、第2の膜24及び第3の膜26を下部電極14側から順に有し、第1の膜22及び第3の膜26は、第2の膜24よりもシリコン組成比又はアルミニウム組成比が大きい誘電体部16と、を備える容量素子である。

(もっと読む)

積層構造体、強誘電体ゲート薄膜トランジスター及び強誘電体薄膜キャパシター

【課題】強誘電体ゲート薄膜トランジスターの伝達特性が劣化し易い(例えばメモリウインドウの幅が狭くなり易い)という問題をはじめとして、PZT層から酸化物導電体層にPb原子が拡散することに起因して生ずることがある種々の問題が解決された強誘電体ゲート薄膜トランジスターを提供する。

【解決手段】強誘電体ゲート薄膜トランジスター20は、チャネル層28と、チャネル層28の導通状態を制御するゲート電極層22と、チャネル層28とゲート電極層22との間に配置された強誘電体層からなるゲート絶縁層25とを備え、ゲート絶縁層(強誘電体層)25は、PZT層23と、BLT層24(Pb拡散防止層)とが積層された構造を有し、チャネル層28(酸化物導電体層)は、ゲート絶縁層(強誘電体層)25におけるBLT層(Pb拡散防止層)24側の面に配置されている。

(もっと読む)

コンデンサ

【課題】小型でかつ高い静電容量を得られ、さらに絶縁性能の高い薄膜誘電体を用いたコンデンサを提供する。

【解決手段】薄膜コンデンサは無機物層と、自己組織化によって形成した有機物層とを積層した厚み10nm以下の誘電体膜と、前記誘電体膜の表面に形成された電極膜とを有する。電極膜はアルミを蒸着法によって、誘電体膜はアルミ蒸着膜を酸素プラズマ処理によって酸化膜を形成した表面に有機膜を付与して、形成することができる。これらを繰り返し積層、さらに巻回することが望ましい。

(もっと読む)

誘電体材料を含む個別要素又は半導体デバイスを含む集積回路デバイス

【課題】 本発明は、ドープされた金属酸化物誘電体材料を有する電子部品及びドープされた金属酸化物誘電体材料を有する電子部品の作製プロセスを提供する。

【解決手段】 ドープされた金属酸化物誘電体材料及びこの材料で作られた電子部品が明らかにされている。金属酸化物はIII族又はV族金属酸化物(たとえば、Al2O3、Y2O3、Ta2O5またはV2O5)で、金属ドーパントはIV族元素(Zr、Si、TiおよびHf)である。金属酸化物は約0.1重量パーセントないし約30重量パーセントのドーパントを含む。本発明のドープされた金属酸化物誘電体は、多くの異なる電子部品及びデバイス中で用いられる。たとえば、ドープされた金属酸化物誘電体は、MOSデバイスのゲート誘電体として用いられる。ドープされた金属酸化物誘電体はまた、フラッシュメモリデバイスのポリ間誘電体材料としても用いられる。

(もっと読む)

半導体装置及びそれを用いたSiPデバイス

【課題】高耐圧の能動素子を含む回路と低電圧で動作するロジック回路とが同一基板上に混載された半導体装置を低コストで実現する。

【解決手段】半導体装置が、ロジック回路50と、能動素子回路とを具備している。ロジック回路50は、半導体基板1に形成された半導体素子2を備えている。該能動素子回路は、半導体基板1の上方に形成された拡散絶縁膜7−1の上に形成された半導体層8−1、8−2を用いて形成されたトランジスタ21−1、21−2を備えている。この能動素子回路がロジック回路50により制御される。

(もっと読む)

半導体装置の製造方法及び基板処理システム

【課題】EOTの低減及びリーク電流の低減を両立できる半導体装置の製造方法を提供すること。

【解決手段】被処理体上に第1の高誘電率絶縁膜を成膜する第1の成膜工程と、前記第1の高誘電率絶縁膜を、650℃以上で60秒未満の間熱処理する結晶化熱処理工程と、前記第1の高誘電率絶縁膜上に、前記第1の高誘電率絶縁膜の金属元素のイオン半径よりも小さいイオン半径を有する金属元素を有し、前記第1の高誘電率絶縁膜よりも比誘電率が大きい、第2の高誘電率絶縁膜を成膜する第2の成膜工程と、を含む、半導体装置の製造方法。

(もっと読む)

多層膜キャパシタ構造及び方法

【課題】多くの電極あるいは電極の組合せのいずれにも簡単に接近できる改良された膜キャパシタ構造の提供。

【解決手段】多層膜キャパシタ構造が、モノリシック基板上の下部電極層、下部電極上に敷かれている膜電極及び誘電体材料の対からなる中間層、及び中間層対の上に敷かれている膜電極及び膜誘電体の対からなる上部層を有する。この構造は、デバイスの全周縁にわたって、それぞれの電極層がその上の層の周縁の外側まで側方に広がる、

メサ形状を有することが望ましい。電極をいかなる組合せでも接続でき、いかなる所望の回路接続もできるように、各電極層はその突き出している縁にビアを通して接続できる上部表面を有する。望ましければ、単層キャパシタ構造をフィルタに最適化し得るように、誘電体材料に異なる周波数特性をもたせることができる。

(もっと読む)

半導体装置の製造方法

【課題】スループットを低下させずに異なるメモリセルの誘電体膜とキャパシタの誘電体膜を同時に形成するための半導体装置の製造方法を提供する。

【解決手段】第1酸化膜18、窒化膜19、第2酸化膜20を順に形成した第1の誘電体膜を第1の半導体膜16上に形成する工程と、第1領域I内の第1の誘電体膜21をエッチングする工程と、第1領域Iの半導体基板1の表面に第3酸化膜25を形成する工程と、第1領域VI及び第2領域IIIに開口部28a、28bを有し、さらに第3領域II内の第1の誘電体膜21を覆う形状を有するマスク28を半導体基板1の上方に形成する工程と、マスク28の開口部28a、28bを通して、第1領域VI内の前記第3酸化膜25と前記第2領域III内の第1の誘電体膜21の第2酸化膜20を同時にエッチングする工程を含む。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】配線層中の配線をゲート電極として使用し、かつ拡散防止膜と同一層にゲート絶縁膜を有している半導体素子を有する半導体装置において、拡散防止膜の機能を損なうことなく、半導体素子のオン抵抗を低くする。

【解決手段】第1配線層150を構成する絶縁層の表層には、第1配線154及びゲート電極210が埋め込まれている。第1配線層150と第2配線層170の間には、拡散防止膜160が形成されている。ゲート絶縁膜230は、拡散防止膜160のうちゲート電極210と重なる領域及びその周囲の上面に凹部を形成し、この部分を薄くすることにより、形成されている。

(もっと読む)

高誘電性ナノシート積層体、高誘電性ナノシート積層体、高誘電体素子、および高誘電体薄膜素子の製造方法

【課題】コンデンサなどに好適な、非常に薄くしても高い誘電率と良好な絶縁特性を同時に実現する高誘電体薄膜を提供する。

【解決手段】上記課題は、ペロブスカイト構造を有する酸化物ナノシートなどの高誘電体により構成される薄膜により達成される。

(もっと読む)

キャパシタの形成とともに不揮発性メモリのゲートスタックをパターニングするための方法

【課題】キャパシタのエッチングはNVMセルのエッチングの終点検出に有用になるようにキャパシタおよびNVMセルを集積するように形成する。

【解決手段】NVM領域およびキャパシタ領域上に2つの導電体層を用いるように達成される。第1導電体層は後のパターニングステップの準備にパターニングされ、これが、NVM領域およびキャパシタ領域の両方に第1導電体層および第2導電体層の両方をパターニングするステップを含む。後のエッチングが、同一マスクを用いて両方の導電体層をエッチングされることによって制御ゲート上に浮遊ゲートの重要な配列を提供する。この後のエッチングの間、キャパシタ領域に第1導電体材料をエッチングされることが、NVM領域における第1導電体層のエッチングの終点検出を補助する。

(もっと読む)

コンデンサ及びその製造方法

【課題】金属−絶縁体−金属コンデンサや、内部接続構造の金属間誘電体として使用して、その素子や構造の平均故障寿命を改善できる誘電体構造を提供すること。

【解決手段】酸化膜層、誘電体材料層及び誘電体材料層の上に第2酸化膜層を有する、炭化ケイ素用のコンデンサ及び内部接続構造が提供される。酸化膜層の厚みは、酸化膜層と誘電体材料層の約0.5から約33パーセントであってよい。誘電体構造として酸窒化ケイ素層を有する炭化ケイ素用のコンデンサおよび内部接続構造もまた提供される。こうしたコンデンサ及び構造を作製する方法もまた提供される。

(もっと読む)

半導体装置および半導体装置の駆動方法

【課題】記憶保持期間において、電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供すること。

【解決手段】トランジスタと、容量素子と、を有し、トランジスタは、第1の酸化物半導体層と、第1の酸化物半導体層と接するソース電極およびドレイン電極と、第1の酸化物半導体層と重なるゲート電極と、第1の酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、を有し、容量素子は、ソース電極またはドレイン電極と、ソース電極またはドレイン電極と接する第2の酸化物半導体層と、第2の酸化物半導体層と接する容量素子電極と、を有する半導体装置である。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】実用上限温度をより向上させた炭化珪素半導体装置の製造方法を提供する。

【解決手段】ゲート窓6が形成された炭化珪素基板1の表面に、前駆酸化シリコン膜を成膜する工程と、前駆酸化シリコン膜を酸化窒素ガス雰囲気で熱処理して第1の酸化シリコン膜(O)とする工程と、窒化シリコン膜(N)を積層する工程と、窒化シリコン膜を酸化させて、表面から所定の深さまで第2の酸化シリコン膜(O)を形成して、ONO絶縁膜を形成する工程と、ONO絶縁膜の上にゲート電極を形成する工程とを備える。ゲート電極を形成する工程は、ONO絶縁膜の上に多結晶シリコン膜を成膜する工程と、所望のマスクを用いて、多結晶シリコン膜、第2の酸化シリコン膜、窒化シリコン膜、を連続的にエッチングして、ゲート電極と第2の酸化シリコン膜と窒化シリコン膜の外縁を定義する工程と、ゲート電極の側面及び上部と窒化シリコン膜の外縁を酸化する工程を備える。

(もっと読む)

可変容量素子、及び液晶表示装置

【課題】制御性が良く、安定して動作する可変容量素子を提供する。消費電力が少なく、表示品位の良い液晶表示装置を提供する。

【解決手段】印加される電界により、n型またはi型となる半導体、もしくは、p型またはi型となる半導体を用いて可変容量素子を構成する。容量素子を構成する第1の電極と第2の電極の間に、誘電体層として絶縁層と上記半導体層の積層を設ける。第1の電極を誘電体層側に設け、第2の電極を半導体層側に設けた時に、第1の電極と半導体層が重畳する面積C1よりも、第1の電極と半導体層と第2の電極が重畳する面積C2の方を小さくなるようにする。動画像表示と静止画像表示で駆動方法を切り替える液晶表示装置に可変容量素子を適用することで、消費電力が少なく、表示品位の良い液晶表示装置を実現できる。

(もっと読む)

半導体装置の製造方法および基板処理装置

【課題】半導体装置に用いられるキャパシタを効率よく、しかも少ない占有床面積で行うことができる半導体装置の製造方法および基板処理装置を提供する。

【解決手段】基板200上に下電極を形成する工程(S104)と、下電極の上に、それぞれ異なる金属元素を含む3種の金属酸化膜を積層して誘電膜を形成する工程(S106、S108、S110)と、誘電膜の上に、上電極を形成する工程(S112)と、を有し、各工程は同一の装置で行う。

(もっと読む)

半導体装置およびその製造方法

【課題】下部電極、上部電極およびそれらの間の絶縁膜により構成される容量素子の下部電極および上部電極間の耐圧を向上させる。

【解決手段】上部電極TEならびに上部電極TEのそれぞれの側壁の側壁酸化膜9およびサイドウォール10と下部電極BEとの間にONO膜IFを連続的に形成し、また、上部電極TEの側壁に、側壁酸化膜9を介して真性半導体膜からなるサイドウォール10を形成することにより、下部電極BEおよび上部電極TE間にリーク電流が発生することを防ぐ。

(もっと読む)

半導体装置

【課題】プロセスを簡素化し低コスト化を実現するとともに、さらに、システムを簡素化しノイズ対策を可能にするMEMSレゾネータ及びMEMSレゾネータの製造方法を提供する。

【解決手段】MEMSレゾネータの製造方法は、基板10上に形成された半導体デバイスとMEMS構造体部4とを有するMEMSレゾネータ2の製造方法であって、半導体デバイスは、上部電極30と下部電極26とを有するONOキャパシタ部6と、CMOS回路部8と、を含み、ONOキャパシタ部6の下部電極26を、第1シリコン層26を用いて、形成する。MEMS構造体部4の下部構造体16とONOキャパシタ部6の上部電極30とを、第2シリコン層52を用いて、形成する。及び、MEMS構造体部4の上部構造体18とCMOS回路部8のゲート電極34とを、第3シリコン層54を用いて、形成する。

(もっと読む)

半導体装置

【課題】プロセスを簡素化し低コスト化を実現するとともに、さらに、システムを簡素化しノイズ対策を可能にするMEMSレゾネータ及びMEMSレゾネータの製造方法を提供する。

【解決手段】MEMSレゾネータの製造方法は、基板10上に形成された半導体デバイスとMEMS構造体部4とを有するMEMSレゾネータ2の製造方法であって、半導体デバイスは、上部電極30と下部電極26とを有するONOキャパシタ部6と、CMOS回路部8と、を含み、ONOキャパシタ部6の下部電極26を、第1シリコン層26を用いて、形成する。MEMS構造体部4の下部構造体16とONOキャパシタ部6の上部電極30とを、第2シリコン層52を用いて、形成する。及び、MEMS構造体部4の上部構造体18とCMOS回路部8のゲート電極34とを、第3シリコン層54を用いて、形成する。

(もっと読む)

キャパシタ装置及びその製造方法

【課題】キャパシタ装置及びその製造方法を提供する。

【解決手段】本発明に係るキャパシタ装置10は、第1導電型を有して第1電圧が印加される第1ウェル105及び第2導電型を有して第2電圧が印加される第2ウェル110を有する基板100、及び第1または第2ウェル105,110と絶縁されるように第1または第2ウェル105,110の上部に配されたゲート電極126を含み、キャパシタ装置10のキャパシタンスは、第1ウェル105と第2ウェル110との間の第1キャパシタンス及び第1または第2ウェル105,110とゲート電極126との間の第2キャパシタンスを含む。

(もっと読む)

1 - 20 / 179

[ Back to top ]