Fターム[5F038AR08]の内容

Fターム[5F038AR08]に分類される特許

1 - 20 / 70

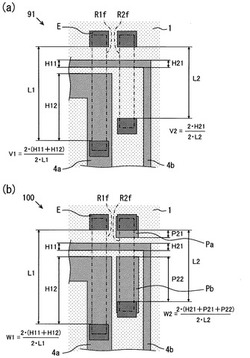

半導体装置

【課題】任意の配線設計に適用でき、高精度な抵抗比を有する2個の抵抗体を備えた小型の半導体装置を提供する。

【解決手段】抵抗体R1f,R2fの長さをL、配線4a,4bの直上にある抵抗体R1f,R2fの外辺の長さを配線上長さH、外辺配線被覆率Vを、V=H/2Lで定義したとき、2個の抵抗体R1f,R2fのうち少なくとも外辺配線被覆率Vの小さい抵抗体R2fの下方において、配線4a,4bと同じ配線層から形成された反射補正パッドPa,Pbが、外辺の直下に配置されてなり、反射補正パッドPa,Pbの直上にある抵抗体R2fの外辺の長さを補正パッド上長さPとし、抵抗体R1f,R2fの外辺配線層被覆率Wを、W=(H+P)/2Lで定義したとき、2個の抵抗体R1f,R2fについて、外辺配線層被覆率Wの差が、記外辺配線被覆率Vの差より小さく設定されてなる半導体装置100とする。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

ヒューズ、半導体装置、半導体装置の製造方法

【課題】高電圧が不要で安定した状態を得ること。

【解決手段】半導体装置10に形成されたヒューズ素子11は、概略的に、拡散領域22と、拡散領域22と一部重なるように拡散領域22より上方に形成された導電体25を含む。半導体装置10の半導体基板21には、拡散領域22が形成されている。半導体基板21には素子分離領域23が形成されている。拡散領域22を含む半導体基板21上には絶縁膜24が形成されている。絶縁膜24上には、導電体25が形成されている。導電体25上には、カバー膜26が形成されている。カバー膜26は、導電体25の上面及び側面を覆うように形成されている。カバー膜26は、絶縁膜24より高い引っ張り応力を持つ。

(もっと読む)

半導体装置の製造方法

【課題】信頼性を低下することなく、高集積化が可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置の製造方法は、薄膜抵抗体と配線層とが、接続層とビアホールに埋設されたタングステンプラグとを介して電気的に接続されてなる半導体装置の製造方法である。従来、接続層は、バリアメタル層を介して薄膜抵抗体と接続された構成である。この接続層としてアルミニウムを用いたものでは、接続層とタングステンプラグとの線膨張係数の差異に起因してストレスマイグレーションにより、接続層にボイドが発生する懸念があった。本発明では、接続層を除去する工程を実施し、タングステンプラグをバリアメタル層と直接接続する。これにより、タングステンプラグは、アルミニウムよりなる接続層を介することなく、薄膜抵抗体と電気的に接続される。したがって、接続層におけるボイドの発生を抑制し、半導体装置の接続信頼性を向上することができる。

(もっと読む)

半導体装置およびその製造方法

【課題】チップ面積の増加を抑えつつ、金属等からなるゲート電極を有するMISトランジスタと、抵抗体とを同一基板上に不具合なく形成する。

【解決手段】半導体装置は、半導体基板1上にそれぞれ設けられたMISトランジスタと抵抗素子とを備える。MISトランジスタは、活性領域1aと、活性領域1a上に設けられたゲート絶縁膜18と、ゲート絶縁膜18上に設けられたゲート電極19とを有する。抵抗素子40は、素子分離領域2上に設けられた抵抗体10を有しており、ゲート電極19の少なくとも一部は、抵抗体10よりも小さな抵抗率を有しており、活性領域1a上においてはゲート電極19の上面を覆っておらず、抵抗体10の上面を覆っている層間絶縁膜16がさらに設けられる。

(もっと読む)

半導体装置

【課題】半導体装置において、高電圧の配線層とその下方を横切るように配置された抵抗層との間の絶縁膜の耐圧を確保し、この配線層と抵抗層との間で破壊が起きるのを抑制することを目的とする。

【解決手段】第1半導体領域10に接続され第2半導体領域11上を通過するように第3配線層22が配置されている。第3配線層22と第2半導体領域11との間に配置される絶縁膜14内には、一端が第3配線層22に接続されると共に、他端が第1半導体領域11よりも電位の低い制御端子12に接続され、且つ第3配線層22とSOI層2との間において第3配線層22を少なくとも1回以上横切る構成で抵抗層25が配置されている。この抵抗層25は、第3配線層22を横切る部位の上面が他の部位よりも下方位置となるように段差状に形成されている。

(もっと読む)

半導体装置の製造方法

【課題】製造工程を簡略化することができる半導体装置の製造方法を提供する。

【解決手段】半導体基板1上に薄膜抵抗体15を構成する金属薄膜およびバリアメタル16を構成するバリアメタル薄膜を形成する。そして、金属薄膜およびバリアメタル薄膜をパターニングし、薄膜抵抗体15と当該薄膜抵抗体15上にバリアメタル膜16aを形成する。その後、バリアメタル膜16a上に絶縁膜17を形成し、絶縁膜17にバリアメタルエッチング部16bを露出させる開口部17aと、コンタクト部を露出させるコンタクトホール17bを形成する。続いて、コンタクトホール17bを介してバリアメタル膜16aと電気的に接続される導電性薄膜18cを形成する。その後、導電性薄膜18cのうちバリアメタルエッチング部16b上に位置する部分をウェットエッチングによってパターニングし、バリアメタル膜16aのうちバリアメタルエッチング部16bをパターニングする。

(もっと読む)

抵抗回路を有する半導体装置

【課題】高抵抗・高精度の抵抗素子からなる抵抗回路を提供する。

【解決手段】500Å以下に薄膜化した薄膜材料からなる抵抗素子の上にシリコン窒化膜などの絶縁膜を形成する。この窒化膜により抵抗素子に対するコンタクトホールの突き抜けを防止する。

(もっと読む)

半導体装置及びその製造方法

【課題】占有面積の小さい抵抗体を有する半導体装置を提供する。

【解決手段】半導体基板上のフィールド酸化膜の上に導電性多結晶シリコンを形成し、その上を覆う絶縁膜に多結晶シリコン5に達するコンタクトホールを形成する。コンタクトホールの中にはタングステンサイドウォール9、シリコン酸化膜サイドウォール10、抵抗体11があり、抵抗体の上には電極12を配置することで上下方向に縦長の抵抗体11とする。

(もっと読む)

半導体装置およびその製造方法

【課題】ゲート絶縁膜をHigh−k材料で構成し、ゲート電極をメタル材料で構成するHK/MGトランジスタと、抵抗素子とを同一基板に有する半導体装置において、安定したHK/MGトランジスタの動作特性を得ることのできる技術を提供する。

【解決手段】TiN膜と多結晶Si膜との積層膜からなるHK/MGトランジスタのゲート電極を形成し、同様に、TiN膜と多結晶Si膜との積層膜からなる抵抗素子を形成した後、抵抗素子の側壁に形成したオフセットサイドウォール9aおよびサイドウォール9の一部を除去し、そのオフセットサイドウォール9aおよびサイドウォール9が除去された箇所から薬液を浸入させることによりTiN膜を除去して空洞18を形成し、多結晶Si膜のみからなる抵抗部RESを形成する。

(もっと読む)

ポリシリコン抵抗の設計方法及び半導体装置の製造方法

【課題】半導体装置のサイズの大型化を抑制しつつ、ポリシリコン抵抗の抵抗値が設計値からずれた場合に補正できるようにする。

【解決手段】ポリシリコン抵抗の設計方法は、シリサイド領域1bが両端にそれぞれ形成されたポリシリコンにより構成され、シリサイド領域1bがコンタクト3へ接続されるポリシリコン抵抗1の、抵抗値を判定する工程を有する。抵抗値が設計値よりも大きい場合には、コンタクト3の位置とポリシリコン抵抗1の形成範囲とを変更せずに、シリサイドブロック膜の形成範囲を狭める補正を行うことによって、ポリシリコン抵抗1の抵抗値を減少させる工程を行う。抵抗値が設計値よりも小さい場合には、コンタクト3の位置を変更せずに、ポリシリコン(シリサイドブロック領域1a)の幅を狭める補正を行うことによって、ポリシリコン抵抗1の抵抗値を増大させる工程を行う。

(もっと読む)

薄膜抵抗を備えた半導体装置の製造方法

【課題】薄膜抵抗と配線部との接触抵抗が高抵抗化することを抑制できる薄膜抵抗を備えた半導体装置の製造方法を提供する。

【解決手段】スパッタ装置内において事前にチタンの表面を窒化させておくことで窒化チタンを形成しておき、その後、窒素の導入を停止した状態で窒化チタンをターゲットとしたスパッタにより、窒化チタン膜によって構成される第1金属層5を形成する。これにより、薄膜抵抗Rと接触する第1金属層5を形成する際に、スパッタ装置内に窒化ラジカルが基本的には存在していない条件で第1金属層5の成膜を行うことができるため、薄膜抵抗Rの露出部分に窒化物が形成されないようにできる。したがって、薄膜抵抗Rと配線部の一部を構成する第1金属層5との接触抵抗が高抵抗化することを抑制することが可能となる。

(もっと読む)

半導体装置および配線用マスク判別方法

【課題】使用した配線用マスクを簡単かつ確実に判別でき、確認工数を削減する。

【解決手段】所定の配線パターンと共に両端に端子を備えた抵抗素子の複数41、42、43、を含む抵抗素子領域を形成するための所定配線用マスクを用いたリソグラフィステップと、半導体ウエハ特有の配線パターンと共に特有の配線パターンに応じて抵抗素子の端子間にて直列およびまたは並列接続された接続配線を含む識別領域50を形成するための識別配線51用マスクを用いたリソグラフィステップと、接続配線に接続され露出したパッド19を形成するためのパッド配線用マスクを用いたリソグラフィステップと、を含む。第1配線層および第2配線層の抵抗素子領域および識別領域の組がTEGチップまたはスクライブラインに形成されている。露出したパッドを介して抵抗素子の直列およびまたは並列接続された接続配線の抵抗値を測定するステップを更に含む。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】複数に分割された接続部とこれらの接続部の間に形成された抵抗体とが、電極パッドにより良好に接続される半導体装置の製造方法を提供すること。

【解決手段】複数のFET12が化合物半導体基板11上に並列に形成され、ゲートパッド27が複数に分割された半導体装置の製造方法であって、化合物半導体基板11上に抵抗体22を形成する工程と、抵抗体22上にこの抵抗体22を保護する保護パターン23を形成する工程と、複数のFET12、抵抗体22および保護パターン23を含む化合物半導体基板11上に保護膜24を形成する工程と、複数のFET12の各電極13、14、15をそれぞれ接続する電極接続部17、18、21上および保護パターン23上の保護膜24をエッチングにより除去する工程と、エッチングにより除去した位置に電極パッド25、26、27を形成する工程と、を具備する。

(もっと読む)

半導体集積装置

【課題】ダイオードと電流制限抵抗の配置関係を最適化することにより、半導体集積装置の短辺方向の縮小し、占有面積が狭く製造単価の安い半導体集積装置を実現する。

【解決手段】ダイオードを分割して個々のサイズを小さくし、横方向配置の分割ダイオード1,2間で、かつ横方向配置の分割ダイオード3,4間に電流制限抵抗6を横方向に配置することにより、半導体集積装置の短辺方向の寸法縮小が可能となる静電気保護回路10のレイアウトを得ることができる。

(もっと読む)

電気化学キャパシタ

【課題】容量を高めることが可能な電気化学キャパシタを提案する。

【解決手段】基板の一平面上に正極と負極が形成される電気化学キャパシタである。また、電解質と、電解質の同一平面に接する正極及び負極とを有する。即ち、電解質の一平面上に接する正極活物質及び負極活物質と、正極活物質に接する正極集電体と、負極活物質に接する負極集電体とを有する電気化学キャパシタである。当該構成により、電気化学キャパシタの容量を増大させることができる。

(もっと読む)

抵抗素子を有する半導体装置及びその製造方法

【課題】基準電圧を調整する回路を構成する抵抗素子を有するフラッシュ記憶素子である半導体装置及びその製造方法を提供する。

【解決手段】フラッシュ記憶素子である半導体装置の製造方法は、半導体基板上にトレンチを定義する鋳型パターンMLDPを形成し、鋳型パターンMLDP上にトレンチを横切る抵抗パターンRPを形成し、抵抗パターンRP上に互いに離隔された第1及び第2導電パターン210、220を形成し、第1及び第2導電パターン210、220に各々接続する第1及び第2配線UL1,UL2を形成する段階を有し、第1及び第2導電パターンUL1,UL2は鋳型パターンMLDPの上部に各々形成される。

(もっと読む)

回路シミュレーション方法

【課題】半導体抵抗素子の端子部寄生抵抗を正確に見積もることができる回路シミュレーション方法。

【解決手段】半導体抵抗素子102と、半導体抵抗素子102の端子部上に、半導体抵抗素子102の幅方向と長手方向とにそれぞれ等間隔に配置された複数のコンタクトCTと、複数のコンタクトCT上に形成された配線101と、を備えた半導体回路のシミュレーション方法。1つのコンタクトCTの抵抗値と、長手方向において隣接するコンタクトCT間の半導体抵抗素子102による寄生抵抗値との比を、定数kとして定義し、半導体抵抗素子102の端子部と、複数のコンタクトCTと、を含む寄生抵抗ネットを、定数kを用いることによりモデル化する。

(もっと読む)

半導体装置の製造方法

【課題】金属薄膜抵抗体を備えた半導体装置において、金属薄膜抵抗体の抵抗値及び配線パターンとの接触抵抗の安定化を実現する。

【解決手段】下地絶縁膜5上に、金属薄膜抵抗体23の両端部の形成予定領域に対応して配線パターン11を形成する。配線パターン11上を含む下地絶縁膜5上に平坦化された絶縁膜19を形成する。平坦化された絶縁膜19に、金属薄膜抵抗体23の両端部の形成予定領域及び配線パターン11に対応して接続孔21を形成する。接続孔21内を含み絶縁膜19に対してArスパッタエッチング技術によりエッチング処理を施して、接続孔21の内壁にサイドウォール22を形成するとともに、接続孔21の上端部21aをテーパー形状にする。接続孔21内及び絶縁膜19上に金属薄膜抵抗体23を形成するための金属薄膜を形成する。接続孔21にも金属薄膜を残存させるように金属薄膜をパターニングして金属薄膜抵抗体23を形成する。

(もっと読む)

半導体装置

【課題】ヒューズ素子の切断不良率を低減する。

【解決手段】本発明による半導体装置100は、金属によって形成され、電気的に溶断可能なヒューズ素子10と、切断電圧に応じた電流をヒューズ素子10に供給するトランジスタ30と、トランジスタ30の電流駆動を開始する動作点を設定する電流調整抵抗20とを具備する。

(もっと読む)

1 - 20 / 70

[ Back to top ]