Fターム[5F038AR25]の内容

Fターム[5F038AR25]に分類される特許

1 - 20 / 62

半導体装置

【課題】抵抗体とヒューズ素子が並列に接続された半導体装置において、ヒューズ素子切断時に抵抗体への損傷がなく、抵抗体とヒューズ素子とを積層すること。

【解決手段】半導体基板上に第1の絶縁膜を介して形成された抵抗体を設け、抵抗体の上に第2の絶縁膜を介して形成された遮光層を設け、遮光層の上に第3の絶縁膜を介して形成されたヒューズ素子のヒューズ部を有し、抵抗体と遮光層とヒューズ部を重畳した半導体装置とする。

(もっと読む)

半導体装置及びその製造方法

【課題】トランジスタの集積度が高い半導体装置及びその製造方法を提供する。

【解決手段】実施形態に係る半導体装置は、第1領域において上面に第1方向に延びる複数本のフィンが形成された半導体基板と、前記第1方向に対して交差した第2方向に延び、前記フィンを跨ぐ第1ゲート電極と、前記フィンと前記第1ゲート電極との間に設けられた第1ゲート絶縁膜と、前記第2領域において前記半導体基板上に設けられた第2ゲート電極と、前記半導体基板と前記第2ゲート電極との間に設けられた第2ゲート絶縁膜と、を備える。そして、前記第1ゲート電極の層構造は、前記第2ゲート電極の層構造とは異なる。

(もっと読む)

トリミング回路、トリミング回路の駆動方法

【課題】信頼性の高いトリミング回路を提供する。書き換え可能なトリミング回路を提供する。信頼性の高いトリミング回路の駆動方法を提供する。書き換え可能なトリミング回路の駆動方法を提供する。

【解決手段】オフリーク電流が極めて小さいトランジスタのソース電極またはドレイン電極に接続された記憶ノードと、該記憶ノードにゲート電極が接続されたトランジスタを用いてトリミング回路を構成する。また、該オフリーク電流が極めて小さいトランジスタを用いて、該記憶ノードにゲート電極が接続されたトランジスタのソース電極とドレイン電極に対して並列に接続された素子または回路のトリミング状態を制御する。

(もっと読む)

半導体装置の製造方法

【課題】ヒューズ(FUSE)を備えた半導体装置の信頼性を向上する。

【解決手段】半導体基板11の主面上に形成にされた多層配線を構成する層M1〜M6のうちの層M4に設けられた電気溶断型の救済用のヒューズ4aおよび試験用のヒューズ4bと、ヒューズ4aの近傍であって層M2および層M6に設けられた一対の導電板10aと、ヒューズ4bの近傍であって層M3および層M5に設けられた一対の導電板10bとから構成する。ヒューズ4bと導電板10bとの間が、ヒューズ4aと導電板10aとの間より近いものとする。

(もっと読む)

半導体装置

【課題】広範囲、光分解能に周波数を可変することのできるクロック信号を生成する。

【解決手段】オペアンプAMP1は、正入力部と負入力部が等しい電圧となるようフィードバックがかかり、回路ノードfbckは、参照電圧VREFIに等しい電圧となる。デコーダDECは、制御信号CNT7,CNT6をデコードし、トランジスタT2〜T5のいずれか1つをオンさせる。この構成によって、回路ノードfbckが、参照電圧VREFIと同電位となるようフィードバック制御がかかるため、トランジスタT2〜T5のON抵抗を大幅に低減することができ、周波数精度の悪化を防止することができる。

(もっと読む)

半導体装置

【課題】抵抗値の温度依存性の小さい抵抗素子を有する半導体装置を提供する。

【解決手段】半導体装置は、金属抵抗素子層Rm1,Rm2を有する。金属抵抗素子層Rm1は、金属抵抗膜層Rm11を含む。金属抵抗素子層Rm2は、金属抵抗膜層Rm12を含む。金属抵抗膜層Rm11は、窒化チタン抵抗および窒化タンタル抵抗のうちの一方であり、金属抵抗膜層Rm12は、窒化チタン抵抗および窒化タンタル抵抗のうちの他方である。窒化チタン抵抗の抵抗値は正の温度係数を有する一方、窒化タンタル抵抗の抵抗値は負の温度係数を有する。コンタクトプラグCP2によって、金属抵抗膜層Rm11と金属抵抗膜層Rm12とが電気的に接続されるので、窒化チタン抵抗の温度係数と窒化タンタル抵抗との温度係数が相殺される。これにより温度係数を小さくすることができる。

(もっと読む)

半導体装置およびその製造方法

【課題】周辺回路の抵抗素子の抵抗部の厚さに依らずにメモリセルトランジスタの浮遊ゲートの厚さを自由に設定することのできる半導体装置、およびその製造方法を提供すること。

【解決手段】基板上の抵抗素子およびスタックド・ゲート型のメモリセルトランジスタを含む半導体装置を提供する。前記抵抗素子は、抵抗として機能しない非導通層、および前記非導通層上に第1の絶縁膜を介して形成された抵抗として機能する導通層を含む。前記メモリセルトランジスタは、第1の浮遊ゲートを含む浮遊ゲートを有する。前記非導通層と前記第1の浮遊ゲートは、同じ材料からなる。

(もっと読む)

半導体装置の製造方法

【課題】トランジスタの特性を劣化させることなくポリシリコン抵抗素子を製造できる半導体装置の製造方法を提供する。

【解決手段】半導体基板30の抵抗素子形成領域に抵抗素子となるポリシリコン膜35aを形成するとともに、トランジスタ形成領域にポリシリコンゲート35b及び高濃度不純物領域40を形成する。その後、全面に絶縁膜41を形成した後、トランジスタ形成領域をフォトレジスト膜42で覆い、ポリシリコン膜35aに導電性不純物をイオン注入する。次いで、フォトレジスト膜42をアッシングにより除去する。このとき、トランジスタは絶縁膜41に覆われているため、アッシングによるダメージが回避される。また、抵抗素子領域に導入された導電性不純物が大気中のO及びHと反応して酸が発生しても、ポリシリコンゲート及び高濃度不純物領域40が酸により溶解することが回避される。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】チップサイズを増大させずに、より少ない製造工程数で製造された、抵抗値の異なる複数の抵抗素子を備えた半導体装置及び半導体装置の製造方法を提供する。

【解決手段】レジストマスク36をマスクとしてゲート電極23とマスク層22とを同一部材及び同一工程で形成し、形成されたマスク層22により高抵抗素子40となるポリシリコン高抵抗層16及びポリシリコン低抵抗層18の積層体と、低抵抗素子42となるポリシリコン高抵抗層16及びポリシリコン低抵抗層18の積層体と、をエッチングすることにより高抵抗素子40と、抵抗値が高抵抗素子40よりも低い低抵抗素子42と、を形成する。

(もっと読む)

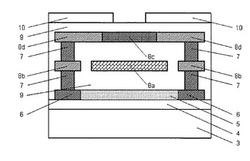

スタック型抵抗素子およびその製造方法

【課題】小型でありながら、単位面積あたりの抵抗密度を高めることのできるスタック型抵抗素子およびその製造方法を提供する。

【解決手段】

スタック型抵抗素子10の抵抗素子13には、小空孔15および大空孔16の2種類の空孔が形成される。その抵抗素子13が複数縦に重ねられ、小空孔15のみがスルーホール17A〜17Dと接続されることで、抵抗素子13同士が直列に接続される。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】ゲート電極間の間隔が狭い場合においても、ゲート電極間のシリサイドブロック膜の抜け性を向上させる。

【解決手段】ゲート電極14と抵抗素子24とが同一半導体基板1上に混載された半導体装置において、シリサイドブロック膜25を介して抵抗素子24の側面にサイドウォール17を形成する。

(もっと読む)

高音質抵抗膜及びその製造方法

【課題】オーディオ信号処理回路に最適なTaN膜とTa膜との積層膜を使用して、TCR値が小さく、シート抵抗が大きく、実用上必要な膜厚を確保できる高抵抗の高音質抵抗膜及びその製造方法を提供する。

【解決手段】高音質抵抗膜は、窒化タンタル膜2aとタンタル膜2bとの積層膜2からなり、この積層膜全体として、抵抗値温度係数TCRが−50乃至+50ppm/℃であると共に、シート抵抗が100Ω/□以上であり、前記窒化タンタル膜は、半導体装置の製造工程で常温から400℃までの温度で、窒素分圧比を3乃至15%として、2.5kW以下の低パワーで、スパッタリングにより成膜されたものである。前記TaN膜のスパッタリング時の基板温度をTとし、窒素ガス分圧比をmとしたとき、前記基板温度T及び窒素ガス分圧比mは、(2/165)T+(91/33)≦m≦(1/66)T+(155/33)を満たすことが好ましい。

(もっと読む)

集積回路

【課題】従来のものに比べて音質を向上させた、アナログ音声信号処理用の回路を内蔵する集積回路を提供する。

【解決手段】集積回路10において、入力端子12,14から入力されたアナログ音声信号は、抵抗素子R1,R2で構成される抵抗回路網20で分圧されてオペアンプ22の非反転入力端に入力される。オペアンプ22の出力信号は抵抗素子R3,R4で構成される抵抗回路網24で分圧されてオペアンプ22の反転入力端に帰還される。抵抗素子R3,R4の両端の信号が出力端子16,18から出力される。抵抗回路網20,24を構成する抵抗素子R1〜R4はそれぞれ窒化タンタル層30とタンタル層28の二層積層構造で構成されている。

(もっと読む)

半導体集積装置

【課題】ダイオードと電流制限抵抗の配置関係を最適化することにより、半導体集積装置の短辺方向の縮小し、占有面積が狭く製造単価の安い半導体集積装置を実現する。

【解決手段】ダイオードを分割して個々のサイズを小さくし、横方向配置の分割ダイオード1,2間で、かつ横方向配置の分割ダイオード3,4間に電流制限抵抗6を横方向に配置することにより、半導体集積装置の短辺方向の寸法縮小が可能となる静電気保護回路10のレイアウトを得ることができる。

(もっと読む)

半導体装置の製造方法及び半導体装置

【課題】抵抗特性のばらつきが少ない抵抗素子を低コストで形成することを可能とした半導体装置の製造方法及び半導体装置を提供する。

【解決手段】SOI領域のSi基板1上にSiGe層を形成する工程と、SiGe層上にSi層13を形成する工程と、Si層13及びSiGe層を平面視で抵抗素子の形状に形成する工程と、Si層13及びSiGe層の各側面にサイドウォール17を形成する工程と、SiGe層を露出する溝部19を形成する工程と、サイドウォール17によりSi層13の側面が支えられた状態で、溝部19を介してSiGe層をエッチングすることにより、Si層13とSi基板1との間に空洞部21を形成する工程と、を含む。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に接続されたユニポーラ型の還流ダイオード150と、還流ダイオード100に並列接続され、少なくともキャパシタ210と抵抗220とを有する半導体スナバ200、及び、還流ダイオード150に並列接続され、少なくともキャパシタ260と抵抗270とを有する半導体スナバ250が形成された基板領域11を有する半導体チップ1000とを備えている。

(もっと読む)

半導体装置

【課題】環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に並列接続され、かつ、キャパシタ210および抵抗220を有する半導体スナバ200とを備えている。半導体スナバ200と還流ダイオード100とが積層されている。

(もっと読む)

半導体装置及び電力変換装置

【課題】還流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮する。

【解決手段】半導体装置は、還流ダイオードDと、還流ダイオードDに対し並列に接続され、且つ、キャパシタと抵抗を有する半導体スナバ回路200と、から構成され、半導体スナバ回路中200のキャパシタが、還流ダイオードDの遮断状態において、還流ダイオードDにより空乏層が形成される前記半導体基体中の領域とは異なる位置に形成されるので、還流ダイオードDの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮することができる。

(もっと読む)

半導体装置

【課題】、環流ダイオードの逆回復動作時に発生する電流及び電圧の振動現象の収束時間を短縮可能な半導体装置を提供する。

【解決手段】半導体装置10は、ユニポーラ型の還流ダイオード100と、還流ダイオード100に並列接続され、かつ、キャパシタ210および抵抗220を有する半導体スナバ200とを備えている。半導体スナバ200は、キャパシタ210または抵抗220と接続される第1電極13と、第1電極13と絶縁されつつ、第1電極13と同一主面上に形成されて、キャパシタ210または抵抗220と接続される第2電極14とを有する。

(もっと読む)

抵抗素子の製造方法

【課題】本発明は、プラズマ原子層堆積法(プラズマALD法)の下地の絶縁膜の絶縁性能を低下させず、プラズマALD法での膜形成により高精度の抵抗素子の形成を可能にする。

【解決手段】表面が絶縁性(例えば絶縁層12)を有する基板10に、熱的原子層堆積法によって第1抵抗層21を形成する第1工程と、プラズマ原子層堆積法によって前記第1抵抗層21上に前記第1抵抗層21と同種の第2抵抗層22を形成する第2工程を有する。

(もっと読む)

1 - 20 / 62

[ Back to top ]