Fターム[5F038BE09]の内容

Fターム[5F038BE09]に分類される特許

1 - 20 / 525

半導体装置

【課題】異なる配線を介して異なる電源端子から内部回路を構成する第1の回路および第2の回路にそれぞれ給電する際に、第1の回路に給電する配線と第2の回路に給電する配線との間に発生するノイズを抑制する。

【解決手段】半導体装置は、第1の回路に給電を行う第1の電源配線と、第2の回路に給電を行う第2の電源配線と、第1の電源配線と第2の電源配線との間に容量素子を設けることにより、両端子間のインピーダンスを、大幅に低減させることにより異種電源間のノイズを低減する。

(もっと読む)

半導体集積回路

【課題】本発明の目的は,論理回路に電源電圧を供給するレギュレータを有する半導体集積回路において,C端子の数を削減する。

【解決手段】

半導体集積回路30は,第1,第2の出力端OTa,OTbと,外部容量C4に接続する外部接続端子CT4との間に設けられたスイッチ回路35を有し,

スイッチ回路35の一端は第1の出力端OTaに接続され,スイッチ回路35の他端は外部接続端子CT4および第2の出力端OTbに接続され,

スイッチ回路35は,第1のレギュレータA31が第1の電源電圧Vaを第1の論理回路A32に対して供給する期間はオンし,第1のレギュレータA31が第1の論理回路A32に対する電源電圧供給を停止する期間はオフする。

(もっと読む)

半導体集積回路

【課題】半導体集積回路に含まれる終端抵抗の抵抗値を4端子法によって測定をするためには、必要となる端子が増加し、半導体集積回路のチップサイズが増加するという問題がある。そのため、半導体集積回路のチップサイズ増加を抑制しつつ、終端抵抗の抵抗値を高精度で測定可能な半導体集積回路が、望まれる。

【解決手段】半導体集積回路は、第1乃至第4のパッドと、第2のパッドと第4のパッドの間に接続される第1の抵抗と、第3のパッドと第4のパッドの間に接続される第2の抵抗と、第1のパッドと第2のパッドの間に接続される第1のスイッチと、第1のパッド及び第3のパッドを4端子法における電圧測定端子として、第2のパッド及び第4のパッドを4端子法における電流供給端子として、それぞれ使用し第1の抵抗の抵抗値を測定するテストモードへの遷移指示を含む制御信号に基づき、第1のスイッチをオンする制御回路と、を備える。

(もっと読む)

給電電圧の変動を吸収する電源構造を持つ集積回路

【課題】給電ユニット(エナジーハーベスティングデバイス)に改変を加えること無く、不安定な給電電圧、特に、低い給電電圧ででも正常に動作する、回路ユニットを含む集積回路を提供する。

【解決手段】本発明に係る集積回路は、外部電源に接続された第1の電源リングで囲まれた第1の回路ブロックと、第1の電源リングを介して前記外部電源に接続された第2の電源リングで囲まれた第2の回路ブロックとを含み、第1の回路ブロック内の半分以上が同期回路で構成され、第2の回路ブロック内の半分以上が非同期回路で構成されている。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

集積回路への電力供給方法、システム及びそれに使用される集積回路

【課題】半導体チップに供給する電圧を、公称最大動作電圧を超えて増加可能にする電力供給方法の提供。

【解決手段】組立てパッケージ内に所定の最大動作電圧を超えない電源電圧で動作するようにされた少なくとも一つの電力入力を有する複数の論理回路16を有するチップ4を有する集積回路2への電力供給方法は、論理回路の選択された1つの論理回路の電力入力において、論理回路の1つにおける電力入力においてチップ内に位置する計測点61で第2の電源電圧を直接測定すること、および計測点と選択された1つの論理回路の電源入力間の電圧降下に基づいて第1の電源電圧を決定するステップと、第1の電源電圧を、論理回路の選択された1つにおける所定の最大動作電圧に調節されるような値を有する基準電圧に調節するステップ、を備える。

(もっと読む)

半導体装置

【課題】半導体素子を、より小型化することができる半導体装置、当該半導体素子、及び基板を得る。

【解決手段】半導体素子12は、階調電圧を出力する半導体素子内部出力部30C,30D(第1及び第2の階調電圧出力部)と、半導体素子内部出力部30Cの周辺に配置され、半導体素子内部出力部30Cに電源を供給する第1の電源端子電極52aと、半導体素子内部出力部30Dの周辺に配置され、半導体素子内部出力部30Dに電源を供給する第2の電源端子電極52aと、を備え、基板18は、半導体素子内部出力部30C,30Dの両方に共通して接続され、半導体素子12の下側に設けられた共通接続部94(第1の配線パターン)と、共通接続部94と外部入力端子(22)とを電気的に接続するインピーダンス調整部96(第2の配線パターン)と、を備える。

(もっと読む)

半導体集積回路装置

【課題】過電圧がLSIの電源端子に印加されたことを確認できるようにする。

【解決手段】半導体集積回路装置(10)は、内部回路(11)と、上記内部回路に電源電圧を供給するための電源端子(15,16)とを含む。このとき、上記内部回路の電源電圧として想定されるレベルを越える電圧(過電圧)が上記電源端子に印加された事実を記録するための過電圧印加情報記録回路(12)を設ける。過電圧印加情報記録回路には、過電圧が上記電源端子に印加された事実が記録されているため、それに基づいて、過電圧がLSIの電源端子に印加されたことを確認することができる。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体層を用いた素子を配線層間に形成し、かつ、ゲート電極の材料を、配線の材料以外の導電体にする。

【解決手段】第1配線層150の表層には、第1配線210が埋め込まれている。第1配線210上には、ゲート電極218が形成されている。ゲート電極218は、第1配線210に接続している。ゲート電極218は、第1配線210とは別工程で形成されている。このため、ゲート電極218を第1配線210とは別の材料で形成することができる。そしてゲート電極218上には、ゲート絶縁膜219及び半導体層220が形成されている。

(もっと読む)

半導体装置

【課題】チップサイズの増大を抑えつつ、多数の配線間の時定数を一致させる。

【解決手段】半導体装置は、第1のサイズを持つ第1の外部端子と、第1のサイズよりも小さな第2のサイズを持つ複数の第2の外部端子と、第1の外部端子及び複数の第2の外部端子が、前記第1のサイズを基準として配列される外部端子領域と、外部端子領域に隣接して形成され、複数の第2の外部端子にそれぞれ対応付けられる複数の回路と、複数の第2の外部端子とそれら対応付けられた複数の回路との間をそれぞれ接続する複数の配線とを備える第1のチップを含む。複数の第2の外部端子及びそれらに接続された複数の配線は複数のインタフェースを構成し、複数のインタフェースの夫々は、互いに実質的に等しい時定数を持つように、時定数を調整する調整部を少なくとも一つ含む。調整部の少なくとも一部は、外部端子領域内の第1のサイズと第2のサイズとの差により生じるマージン領域に配置される。

(もっと読む)

半導体装置及び半導体装置の試験方法

【課題】不良電流パスの選別に要する時間を短縮する。

【解決手段】半導体装置は、それぞれ少なくとも1つの貫通電極を含み、インターフェイスチップ内に第1のノードn1を有する複数の電流パス101Xと、互いに異なる複数の電圧値からなる比較電圧DACOUTを生成する比較電圧生成部102と、複数の電流パス101Xそれぞれの第1のノードn1の電圧TSVCXと、比較電圧DACOUTの上記複数の電圧値それぞれとを比較し、比較の結果を示す比較結果信号CMPXを電流パス101Xごとに出力する比較部103と、比較結果信号CMPXに応じて、複数の電流パス101Xのそれぞれが高抵抗化しているか否かを示す結果信号RESLTXを生成する結果信号生成部104とを備える。

(もっと読む)

半導体集積回路装置

【課題】高周波回路に於いては、トランジスタ等の能動素子間および能動素子と外部端子の間を直流的に遮断する必要がありため、MIMキャパシタ等が多用される。これらのMIMキャパシタのうち、外部端子に接続されたものは、外部からの静電気の影響を受けやすく、静電破壊等の問題を発生しやすい。

【解決手段】本願発明は、半絶縁性化合物半導体基板上に形成された半導体集積回路装置であって、外部パッドに電気的に接続されたMIMキャパシタの第1の電極は前記半絶縁性化合物半導体基板に電気的に接続されており、一方、前記MIMキャパシタの第2の電極は前記半絶縁性化合物半導体基板に電気的に接続されている。

(もっと読む)

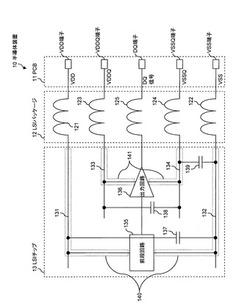

半導体集積回路装置

【課題】電源遮断領域の信号配線の自由度を低下させないで、電源遮断用スイッチから電源遮断領域に至る電圧伝達経路における電圧降下を抑える。

【解決手段】半導体集積回路装置(80)は、電源遮断用スイッチ(90)と電源遮断領域(763)とが形成された半導体チップ(22)とを含む。半導体チップは基板(21)に結合される。上記電源遮断領域の外側に上記電源遮断用スイッチを配置することで、電源遮断領域内の配線チャネル数の低減を回避する。そして上記基板には、上記半導体チップ内から上記電源遮断用スイッチを介して上記半導体チップの外に伝達された電源電圧を再び上記半導体チップ内に伝達して上記電源遮断領域へ給電するための基板側給電路(30)を形成することで、上記電源遮断用スイッチと上記電源遮断領域との間の電圧降下を抑える。

(もっと読む)

半導体装置、DC−DCコンバータ及び受像器

【課題】配線抵抗を低減し導通損失による効率低下を改善した半導体装置、DC−DCコンバータ及び受像器を提供する。

【解決手段】第1の導電体と、半導体素子搭載部と、半導体素子と、第1の接続部と、第2の接続部とを備えた半導体装置が提供される。前記第1の導電体は、前記半導体素子搭載部の周囲に設けられている。前記半導体素子は、前記半導体素子搭載部に設けられ、第1のスイッチ素子と、前記第1のスイッチ素子と並列的に設けられた第2のスイッチ素子とを有する。前記第1の接続部と前記第2の接続部とは、前記第1のスイッチ素子と前記第2のスイッチ素子との境界を延長した仮想的な境界線よりも前記第1のスイッチ素子の側に設けられ、前記第1のスイッチ素子と前記第2のスイッチ素子とに電気的に接続され、前記第1の導電体と電気的に接続される。

(もっと読む)

半導体集積回路および半導体集積回路の設計方法

【課題】半導体集積回路の面積を増大させることなく、配線性のよいテスト専用回路の電源遮断を実現する半導体集積回路を提供する。

【解決手段】テスト実行時のみ動作するテスト専用回路を有する半導体集積回路1であって、当該半導体集積回路1の内部回路領域(内部制御回路部100)に電源を供給する通常電源(通常動作用電源)104と、当該内部回路領域の全面にメッシュ状に配線され、テスト専用回路に電源供給するテスト用電源103と、テスト用電源103と通常電源104とを接続及び遮断して、通常電源104からテスト用電源103への電源供給を制御する電源遮断スイッチ109と、を備える。

(もっと読む)

半導体装置、システム装置、及び信号制御方法

【課題】処理装置の入出力パッドの端子数を低減することができる半導体装置を提供する。

【解決手段】処理装置21のバス制御回路34に含まれる入出力回路は、外部I/F22と接続されるパッドに接続される。入力部は、パッドから入力される信号に応じた入力信号を出力する。この入力信号は、処理回路31に供給される。パッドは、入力部の入力端子に接続され、出力端子は電源電圧VDDを伝達する電源配線に接続されている。入力部は、外部I/F22のバス制御回路44から入力されるHレベルの信号の電圧を出力端子から出力する。従って、電源配線には、外部I/F22から入力されるHレベルの信号による電圧が供給される。

(もっと読む)

半導体装置、電子機器、および半導体装置の検査方法

【課題】電源端子または接地端子の接続不良を容易に検出する。

【解決手段】半導体装置の電源端子TCと第1の入出力端子T1との間には、電源端子TCがカソード側となり、第1の入出力端子T1がアノード側となるようにダイオードD11が設けられる。判定部10Aは、電源電圧Vccに等しいハイレベルの信号が第1の入出力端子T1に入力されたとき、電源端子TCの電圧が第1の入出力端子T1の電圧よりも低いか否かを判定する。

(もっと読む)

半導体装置

【課題】ウエハーテストにおいて、キャリブレーション動作の評価を、容易、かつ高精度に行うことができる半導体装置を提供する。

【解決手段】キャリブレーション端子ZQを駆動するレプリカバッファ(131)と、レプリカバッファの出力インピーダンスを変化させる際に目標となるインピーダンスが設定され、キャリブレーション端子ZQに接続される可変インピーダンス回路(170)と、を備える。

(もっと読む)

半導体チップ、半導体ウェハおよび半導体チップの検査方法

【課題】配線抵抗に起因した電圧降下を抑制し、検査工程での誤判定を受けにくい半導体チップおよび半導体ウェハを提供する。更に、配線抵抗に起因した電圧降下を抑制し、検査工程で誤判定を受けにくい半導体チップの検査方法を提供する。

【解決手段】電極パッド領域は、絶縁膜(7)上で一列に配列されたn個(n≧3)の電極パッド(4m−4から4m+4)を備える。内部セル領域は、電極パッド領域側に配列されている半導体回路(3l−3から3l+3)にそれぞれ接続された配線(VDDL)をn個の電極パッドの配列方向に備える。n個の電極パッドの内、第1の電極パッド(4m−1)と、第1の電極パッドから1個の電極パッドを隔てた第2の電極パッド(4m+1)とが、絶縁膜中で互いに接続され、かつ、配線Lm−1およびLm+1によって、配線(VDDL)にそれぞれ接続されている。

(もっと読む)

半導体装置

【課題】従来の入出力セルよりも回路面積の大きな入出力セルを面積効率良く配置する。

【解決手段】半導体装置において、複数の第1バッファセル31〜34は、基板の一辺に沿って1列に設けられる。複数の第2バッファセル21,22は、複数の第1バッファセルよりも基板の中央寄りの位置に、複数の第1バッファセルの配列方向に沿って1列に設けられる。複数の第1パッド81〜88は、複数の第1バッファセルの上部に上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、複数の第1パッドよりも基板の中央寄りの位置に、上記配列方向に沿って1列に設けられる。複数の第2パッド61〜66は、各々が、複数の第1バッファセルのいずれか1つと個別に接続される複数の第3のパッド61,63,65,66と、各々が、複数の第2バッファセルのいずれか1つと個別に接続される複数の第4パッド62,64とを含む。

(もっと読む)

1 - 20 / 525

[ Back to top ]