Fターム[5F038BH02]の内容

Fターム[5F038BH02]に分類される特許

1 - 20 / 916

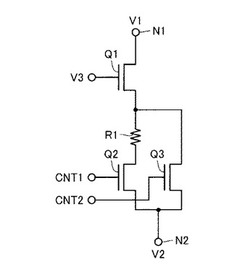

ESD保護回路およびこれを備えた半導体装置

ESD保護回路

半導体装置と、それを用いたインバータ、コンバータおよび電力変換装置

【課題】性能のばらつきが小さな半導体装置を提供する。

【解決手段】この半導体装置は、ノードN1,N2間に直列接続された第1のスイッチング素子(高耐圧のトランジスタQ1)および第2のスイッチング素子(抵抗素子R1および低耐圧のトランジスタQ2)と、第2のスイッチング素子に並列接続された第3のスイッチング素子(低耐圧のトランジスタQ3)とを含む。トランジスタQ2をオンさせるとトランジスタQ1がオンし、さらにトランジスタQ3をオンさせるとノードN1,N2間が導通状態になる。したがって、オン抵抗値の高い第1のスイッチング素子をオンさせて高耐圧のトランジスタQ1をオンさせるので、ターンオン時間のばらつきが小さくなる。

(もっと読む)

トリミング回路及び調整回路

【課題】ヒューズ素子の仮想切断を可能にすると共に、高電圧又は大電流によるヒューズ溶断の際に、周辺回路を破損する確率も低減できる信頼性の高いトリミング回路を提供する。

【解決手段】ヒューズトリミングを行うための回路であって、トリミングヒューズと、

前記トリミングヒューズに接続されるトリミング用のパッド端子と、仮想切断時に制御信号を入力するテスト端子と、入力端子の一方が前記テスト端子に接続され他方が前記トリミングヒューズに接続され、入力された制御信号に応じた制御信号を出力する制御回路と、を有し、前記トリミングヒューズの切断により、前記制御回路の他方の入力端子がGNDレベルへプルダウンする手段を備えたことを特徴とする。

(もっと読む)

半導体装置

【課題】本発明は、電圧測定回路における電流損失を抑え、異常動作の場合であっても電圧測定回路が破壊されない半導体装置を提供する。

【解決手段】

本発明は、第1導通電極と、第2導通電極とを有する半導体スイッチ素子10と、半導体スイッチ素子10の第1導通電極および第2導通電極間の電圧を測定するための電圧測定回路31とを備える半導体装置101である。電圧測定回路31は、半導体スイッチ素子10と並列に接続され、半導体スイッチ素子10の導通方向に印加される電圧を所定値に制限するダイオード素子11と、ダイオード素子11に直列に接続された制御用スイッチ7と、半導体スイッチ素子10がオフ状態のときに制御用スイッチ7をオフ状態にし、半導体スイッチ素子10がオン状態のときに制御用スイッチ7をオン状態にするスイッチ制御部15とを含む。

(もっと読む)

半導体装置

【課題】バラスト抵抗の幅を広げることなく、バラスト抵抗の許容電流量を大きくする

【解決手段】バラスト抵抗200を構成する抵抗210の少なくとも一つは、第1抵抗212及び第2抵抗214を有している。第1抵抗212は、保護素子100内で電流が流れる方向である第1の方向(図1ではX方向)に延伸している。第2抵抗214は、第1抵抗212に並列に接続され、第1の方向に延伸している。そして第2抵抗214は、第1抵抗212と同一直線上に位置している。

(もっと読む)

半導体装置

【課題】本発明は、半導体装置に負電流が流れた場合でも、回路素子を構成する深い半導体層の電位に対して、半導体基板の電位が低くなるのを抑制して寄生素子を作動させず、半導体装置の誤動作を防止する。

【解決手段】本発明は、n型の半導体基板3と、半導体基板3の一面に形成し、接続する負荷に電力を供給する電力素子1と、n型のソース・ドレイン領域を有するMOSトランジスタ2cを少なくとも1つ含む回路素子2と、電力素子1および回路素子2に対し独立して配置したp型の半導体層4と、半導体基板3および半導体層4と接続する外部回路とを備えている。外部回路は、電源と、電源に一端を接続する抵抗素子と、抵抗素子の他端にアノード電極を接続し、カソード電極をGND接地するダイオードとを有し、抵抗素子の他端に半導体層4を接続する。

(もっと読む)

半導体装置の製造方法

【課題】エピ抵抗や抵抗チップを用いることなく、奇モードのループ発振を抑えること。

【解決手段】本発明は、金属層60を形成する工程と、複数のFETそれぞれのゲートフィンガー14を共通に接続するゲートバスライン26のパターンのうち一部分を除いたパターンを有するめっき層64と、一部分の領域を被覆する第2マスク層66と、をマスクにして金属層60をパターニングすることで、ゲートバスライン26を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

半導体集積回路

【課題】不具合の発生が抑制された半導体集積回路を提供する。

【解決手段】電圧レベルの高いHi信号、及び、該Hi信号よりも電圧レベルの低いLo信号が異なるタイミングで入力される第1入力端子と、Hi信号が常時入力される第2入力端子と、第1入力端子のHi信号によって第1動作状態、第1入力端子のLo信号によって第2動作状態に制御される素子と、を有する半導体集積回路であって、第2入力端子とグランドとの間にスイッチング素子が設けられており、該スイッチング素子は、第1入力端子にHi信号が入力されている時にOFF状態、第1入力端子にLo信号が入力されている時にON状態となる。

(もっと読む)

半導体装置

【課題】オン抵抗を増大させることなく、ゲート−ソース間のESD耐量を向上させることのできる半導体装置を提供すること。

【解決手段】ポリシリコンゲート層を利用して形成したツェナーダイオードをESD耐量を向上させるために、並列接続させる構造を有する半導体装置とするものであって、ストライプ状または矩形状のツェナーダイオードを並列接続させて、それぞれ活性部内部に形成する半導体装置とする。

【選択図】 図3  (もっと読む)

(もっと読む)

静電気検出回路

【課題】本発明は、静電気検出回路を提供することを目的とする。

【解決手段】本発明の静電気検出回路は、電源線と接地線との間に直列に接続されているレジスター及びスイッチユニットを備え、前記電源線に静電気が存在する場合、前記スイッチユニットはオンされて、前記レジスターの両端に検出電圧が生じ、前記検出電圧は、静電気保護回路を動作させて静電気を除去するか、又は制御回路を動作させてデータを保存する。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧が確保でき、大きな放電電流を流すことが可能なESD保護特性のすぐれたESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3でPN接合ダイオード35を形成する。P+型埋め込み層3はP+型引き出し層5と一体となりN−型エピタキシャル層4を貫通させアノード電極10と接続される。P+型埋め込み層3等で囲まれたN−型エピタキシャル層4にN+型拡散層7と該N+型拡散層7と接続され、これを取り囲むP+型拡散層6を形成する。N+型拡散層7、P+型拡散層6はカソード電極9に接続される。P+型拡散層6をエミッタ、N−型エピタキシャル層4をベース、P+型引き出し層5等をコレクタとする寄生PNPバイポーラトランジスタ38とPN接合ダイオード35でESD保護素子を構成する。

(もっと読む)

半導体装置

【課題】所望のブレークダウン電圧を確保し、大きな放電電流を流せるESD保護特性の良好なESD保護素子を実現する。

【解決手段】適切な不純物濃度のN+型埋め込み層2とP+型埋め込み層3で形成するPN接合ダイオード35と、P型拡散層6と接続するP+型埋め込み層3aをエミッタ、N−型エピタキシャル層4をベース、P+型埋め込み層3をコレクタとする寄生PNPバイポーラトランジスタ38とでESD保護素子を構築する。P+型埋め込み層3はアノード電極10に接続され、P+型拡散層6と、それを取り囲むN+型拡散層7はカソード電極9に接続される。カソード電極9に正の大きな静電気が印加されるとPN接合ダイオード35がブレークダウンし、その放電電流I1によりP+型埋め込み層3よりN−型エピタキシャル層4の電位が下がり寄生PNPバイポーラトランジスタ38がオンし大きな放電電流I2が流れる。

(もっと読む)

半導体装置

【課題】高品質な半導体装置を提供する。

【解決手段】第1の絶縁膜111、第1の電極112、第2の絶縁膜113、及び第2の電極114を含むゲート構造を有するメモリセルMCが複数設けられた記憶部11と、少なくとも外部100からのデータを受信し、記憶部にデータを供給する端子15と、第1の絶縁膜、第1及び第2の電極とを含むゲート構造を有し、電流経路の一端に第1の電圧が印加される第1導電型の第1のトランジスタ16a、一端が第1のトランジスタの電流経路の他端に接続され、他端が端子に接続される第1の抵抗素子16b、一端が端子及び第1の抵抗素子の他端に接続される第2の抵抗素子16c及び、ゲート構造を有し、電流経路の一端が第2の抵抗素子の他端に接続され、電流経路の他端に第2の電圧が印加される第2導電型の第2のトランジスタ16dを含む第1の回路16と、を備える。

(もっと読む)

安定化回路を備える半導体装置

【課題】ガン発振に伴う負性抵抗を抑制し、安定的かつ高効率の電力増幅を得るための安定化回路を備える半導体装置を提供する。

【解決手段】基板10と、基板上に配置され、ガン発振である高周波負性抵抗発振の発振周波数において負性抵抗を生ずる能動素子140と、基板上に配置され、能動素子のドレイン端子電極と出力端子との間に接続され、負性抵抗の絶対値に等しい抵抗値を有する抵抗Rと、抵抗Rに並列に接続され、高周波負性抵抗発振の発振周波数に同調するインダクタンスLとキャパシタンスCからなるタンク回路とからなる安定化回路120とを備え、安定化回路120は、発振周波数に、インダクタンスLとキャパシタンスCからなる共振周波数を同調することによって、発振周波数において、抵抗Rによって負性抵抗をキャンセルする半導体装置。

(もっと読む)

シミュレーション装置およびシミュレーション方法

【課題】ESD保護素子を有する半導体回路の回路シミュレーションを高速かつ精度よく行うことができるシミュレーション装置を提供する。

【解決手段】ESD保護素子を有する半導体回路の動作検証を行うシミュレーション装置は、ESD保護素子の等価回路のパラメータファイルを作成する第1のパラメータファイル作成部と、半導体回路内のESD保護素子以外の内部回路のパラメータファイルを作成する第2のパラメータファイル作成部と、作成したパラメータファイルを記憶するパラメータファイル記憶部と、記憶したパラメータファイルを選択するパラメータファイル選択部と、選択したパラメータファイルを利用して半導体回路のネットリストを作成するネットリスト作成部と、ネットリストに基づいて半導体回路の動作検証を行うシミュレーション実行部とを備える。

(もっと読む)

半導体装置

【課題】ゲート絶縁膜の漏れ電流試験に影響を与えることなく、ゲート・ソース間に抵抗を挿入した半導体装置を提供すること。

【解決手段】実施形態に係る半導体装置は、ゲート電極及びソース電極間に抵抗が挿入されたトランジスタを内蔵する半導体装置であって、ゲート電極及びソース電極間に、抵抗に対して直列に挿入されたダイオードを備えることを特徴とする。

(もっと読む)

EMIフィルタ

【課題】EMIフィルタが形成された半導体素子の小型化を図る。

【解決手段】本発明の実施形態のEMIフィルタは、第1のダイオードD1、第1のキャパシタC1、及び抵抗体Rを備える。第1のダイオードは、第1の半導体層中に設けられ、上記第1の電極、上記第1の半導体層、その表面に形成されたn形の第2の半導体層2A、及びその表面上に形成された第2の電極11を有する。第1のキャパシタは、上記第1の半導体層1表面に形成され、上記第1の電極、上記第1の半導体層、その表面上に形成された第1の誘電体膜10A、及びその上に形成され第2の電極と電気的に接続された第3の電極12を有する。抵抗体は、第1の半導体層上に形成され、第1のダイオードの第2の電極と電気的に接続された第4の電極14を有する。

(もっと読む)

半導体装置の作製方法

【課題】電気特性の制御された酸化物半導体層を用いて作製された抵抗素子及び薄膜トランジスタを利用した論理回路、並びに該論理回路を利用した半導体装置を提供する。

【解決手段】抵抗素子354に適用される酸化物半導体層905上にシラン(SiH4)及びアンモニア(NH3)などの水素化合物を含むガスを用いたプラズマCVD法によって形成された窒化シリコン層910が直接接するように設けられ、且つ薄膜トランジスタ355に適用される酸化物半導体層906には、バリア層として機能する酸化シリコン層909を介して、窒化シリコン層910が設けられる。そのため、酸化物半導体層905には、酸化物半導体層906よりも高濃度に水素が導入される。結果として、抵抗素子354に適用される酸化物半導体層905の抵抗値が、薄膜トランジスタ355に適用される酸化物半導体層906の抵抗値よりも低くなる。

(もっと読む)

半導体集積回路及び保護回路

【課題】 より効率的にESDサージ電流を流すことができるESD保護回路を備える半導体集積回路を提供する。

【解決手段】 半導体集積回路100は、クランプMOSトランジスタ30と、第1トリガー回路部10と、第2トリガー回路部20と、内部回路2とを備える。第1トリガー回路部10は、出力端がクランプMOS30のゲートに接続され、クランプMOSトランジスタ30内のサージ電流のチャネル経路を開閉制御する。そして、第2トリガー回路部20は、出力端がクランプMOS30のウエルに接続され、クランプMOSトランジスタ30内のサージ電流のバイポーラ経路を開閉制御する。

(もっと読む)

1 - 20 / 916

[ Back to top ]