Fターム[5F038CA01]の内容

Fターム[5F038CA01]の下位に属するFターム

素子配置 (1,574)

回路ブロック配置 (981)

領域設定 (1,104)

対称配置 (380)

分散配置 (308)

熱的結合に関するもの (208)

寄生防止 (242)

電極パッド配置 (1,058)

Fターム[5F038CA01]に分類される特許

61 - 66 / 66

半導体パッケージ

【課題】大容量の半導体メモリにおいても、高速動作を維持可能な半導体パッケージを提供する。

【解決手段】外部接続用配線体は、パッド2と、接続配線3と、バンプ電極4とで構成されている。半導体集積回路は、パッド2に直接接続される入力/出力バッファ回路を有している。パッド2を介在して入力/出力バッファ回路に電気的に接続されるバンプ電極4は、入力/出力バッファ回路の近傍上に設けられている。

(もっと読む)

変調器を有する電子コンポーネント

本発明は、電子コンポーネント、特にRFIDトランスポンダに関し、またその種の電子コンポーネントを有するセキュリティ・ドキュメントに関する。この電子コンポーネントは、キャリア信号を変調するための変調器を有し、当該変調器は、少なくとも二つの有機電界効果トランジスタ(72,73)から構成される。 (もっと読む)

半導体集積回路およびその設計方法

【課題】 半導体プロセスのうち金属配線形成時のプラズマ工程において発生するアンテナダメージを防止する事が可能な半導体集積回路を提供する。

【解決手段】 第2導電型ウェル11上に第1導電型拡散層21を設け、MOS型トランジスタのゲート電極13と第1導電型拡散層21をコンタクトホール31、32とCuからなる金属配線41を介して接続する。さらに、第1導電型ウェル12上に第2導電型拡散層22を設け、MOS型トランジスタのゲート電極13と第2導電型拡散層22をコンタクトホール33、34とCuからなる金属配線42を介して接続し、ゲート電極13と第2導電型ウェル11との間のダイオード1を、ゲート電極13と第1導電型ウェル12との間にダイオード2をそれぞれ設置する。これにより、MOS型トランジスタのゲート電極に発生するアンテナダメージを防止する。

(もっと読む)

静電破壊に対する防止装置を備える回路装置

【課題】 静電破壊に対する防止装置を備える回路装置を提供する。

【解決手段】区域(A、B)のそれぞれが、接地電位と電源電圧をもつそれぞれ固有の作動電圧系を有し、かつ、第1の区域(A)の情報端子点(SA)と第2の区域(B)の情報端子点(SB)との間の少なくとも1つの接続(SC)が第1の区域(A)と第2の区域(B)の間の情報の伝送のために備えられている回路装置に関し、前記接続(SC)は、第1の区域(A)の少なくとも1つの第1のトランジスタ(X)、抵抗(R1)および第2の区域(B)の第1のトランジスタ(E)を備えたトランジスタ回路を有し、前記第1のトランジスタ(X)は第1の区域(A)の接地電位(USS)と前記抵抗(R1)の間に接続されており、かつ第2の区域(B)の第1のトランジスタ(E)は前記抵抗(R1)と第2の区域(B)の電源電圧(UDD1)の間に接続されている。

(もっと読む)

高周波トランジスタモデル、および、その作成方法

【課題】レイアウト変更に対応するパラメータ値の変更が可能であり、レイアウト変更可能なトランジスタモデルを提供する。

【解決手段】高周波半導体回路のトランジスタユニットをコンピュータ上で表現するための高周波トランジスタモデルであって、高周波トランジスタの内在的(intrinsic)トランジスタ部Miと、内在的トランジスタ部Miに接続され、トランジスタユニットの電極、配線およびコンタクトのレイアウトの変更に応じて変化するレイアウトパラメータ、たとえばRg_layout,Rg_em,Cc_gb,Rsub_gb,Csub_gb, Cc_db,Rsub_db,Csub_dbおよびRsub1〜Rsub4等を含む寄生的回路とを有する。

(もっと読む)

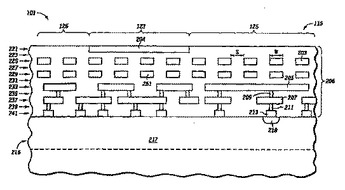

半導体の整合補助部

半導体デバイス用の整合補助部(115)に関する。整合補助部は、高い反射度を有する領域(123)と、低い反射度を有する隣接領域(125)とを備える。低い反射度を有する領域には、半導体デバイスの相互接続層(225)に配置され、かつ半導体デバイスの能動回路(218)の上方に配置されている、1層以上のタイル(203)が含まれる。一部の例では、整合補助部のタイルの走査方向への間隔は、整合補助部の走査に使用される光(例えば、レーザ光)の波長より短い。他の例では、整合補助部のタイルの走査方向への幅が、整合補助部の走査に使用される光の波長より短い。  (もっと読む)

(もっと読む)

61 - 66 / 66

[ Back to top ]