Fターム[5F038CA08]の内容

半導体集積回路 (75,215) | レイアウト (7,547) | チップ平面上でのレイアウト (5,921) | 熱的結合に関するもの (208)

Fターム[5F038CA08]に分類される特許

1 - 20 / 208

半導体装置

【課題】 過電流検出による保護と、温度検出による保護とを、好適に行うことが可能な半導体装置を提供する。

【解決手段】 半導体基板を有する半導体装置であって、半導体基板が、メイン素子領域と、メイン素子領域よりも小さい電流が流れるサブ素子領域を有しており、サブ素子領域が、半導体基板を平面視したときに半導体基板の中心と重なる位置に形成されており、半導体基板上であって、半導体基板を平面視したときにサブ素子領域と重なる位置に、温度検出素子が形成されている。

(もっと読む)

半導体装置、電子装置、車両、及び過熱検出方法

【課題】過熱検出回路の検出温度がばらつくことを抑制する。

【解決手段】コンパレータ170には、第1抵抗110と第1定電流源120の間の電圧Aと、ダイオード130と第2定電流源140の間の電圧Bが入力される。第1リーク電流源150は、ドレインが第1抵抗110と第1定電流源120の間に接続されており、ソース及びゲート電極が第1定電流源120と第2配線104の間に接続されている。第2リーク電流源160は、ドレインが第1配線102とダイオード130の間に接続されており、ソース及びゲート電極がダイオード130と第2定電流源140の間に接続されている。

(もっと読む)

温度検出回路

【課題】 消費電流を抑えるため間欠動作するようにした温度検出用半導体集積回路において、外部端子を増加させることなく回路の評価および検査が行えるようにする。

【解決手段】 発振回路(16)を備え、消費電流を抑えるため間欠動作する温度検出用半導体集積回路において、温度検出回路(11)の出力と基準電圧とを比較する電圧比較回路(13)の出力に対応した信号を出力する外部端子(DET)と、該外部端子に負電位が印加されたことを検出した場合に、温度検出回路と基準電圧回路と電圧比較回路を活性化させる信号を生成する制御回路(17)と、制御回路が活性化信号を出力しかつ温度検出回路の出力が基準電圧を超えたと電圧比較回路(13)が判定した場合に電流を流す電流回路(SW1,R0,SW2)とを設けるようにした。

(もっと読む)

半導体集積回路の設計装置及び半導体集積回路の設計方法

【課題】チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようにする。

【解決手段】熱解析部11は、設計する半導体集積回路のデータから熱解析を行い、温度分布を算出し、ベクトル生成部12は、算出された温度分布の温度勾配に応じたベクトルを生成し、ダミーパターン生成部13は、生成されたベクトルにしたがってダミーパターンを生成し、半導体集積回路のレイアウトデータに追加する。このようなダミーパターンを生成することで、温度分布が平均化され、チップ内の温度差が小さい高信頼性の半導体集積回路を提供できるようになる。

(もっと読む)

半導体装置

【課題】半導体装置の放熱効率を向上させる。

【解決手段】ぺルチェ効果によって吸熱する吸熱部(32、35、41)(37、40、43)と、ぺルチェ効果によって放熱する放熱部(31、35、41)(36、40、43)の両方が単一の半導体チップに集積化されている。このような構成によれば、半導体チップにおいて熱を拡散させ、全体としての放熱抵抗を低下させることができる。これは、放熱効率の向上に寄与する。

(もっと読む)

半導体装置

【課題】半導体基板に半導体素子と内部回路とが設けられた半導体装置において、半導体素子及び内部回路の各温度を検出するセンサを効率的に配置してレイアウトの自由度を高めることができ、且つ半導体素子及び内部回路の各温度をより正確に検出し得る構成を提供することを目的とする。

【解決手段】半導体基板5の一方面側に、スイッチング素子20と、このスイッチング素子20の配置領域から距離を隔てて内部回路30が配置されている。また、スイッチング素子20に隣接して、周囲に第1絶縁膜27が形成された第1温度検出素子24が設けられている。さらに、内部回路30よりもスイッチング素子20に近い側に、周囲に第2絶縁膜28が形成された第2温度検出素子25が設けられている。そして、第2絶縁膜28の厚さが第1絶縁膜27の厚さよりも大きくなるように構成されている。

(もっと読む)

半導体装置

【課題】抵抗素子を有する半導体装置に関し、集積度を低下することなく低消費電力化と高い回路精度とを実現しうる半導体装置を提供する。

【解決手段】半導体材料により形成された複数の抵抗素子と、複数の抵抗素子の近傍に配置された加熱用抵抗素子と、対向する2つの接続ノード間に加熱用抵抗素子が接続され、対向する他の2つの接続ノード間に電源線が接続された抵抗ブリッジ回路とを有する。

(もっと読む)

温度検出装置、温度検出回路およびパワー半導体モジュール

【課題】温度検出回路と絶縁素子とを同一の基板上に形成できるようにし、装置全体の小型化を容易にする温度検出装置を提供する。

【解決手段】温度検出回路200は、温度センサ35で検出された温度をデジタル値に変換するAD変換回路44とデジタル比較回路45を備えている。デジタル比較回路45の出力は、第1パルス発生器52、第2パルス発生器53を経由して絶縁トランス回路101に入力される。絶縁トランス回路101で発生する誘導電流によりパルス信号が信号復調回路102に伝達される。また、温度センサ35で検出された温度が限界温度を越えたときにコンパレータ49からパルス信号が生成され、同様に、信号復調回路102に伝達される。

(もっと読む)

半導体装置

【課題】半導体装置の定格温度(−50℃〜+150℃)において高精度の温度検出を行うことのできる半導体装置を提供すること。

【解決手段】n型基板1の第1主面に、p型ベース領域3と該ベース領域3表面層のn型エミッタ領域4と、前記基板1からなるn型ドリフト層1表面と前記エミッタ領域4表面とに挟まれるp型ベース領域3表面上にゲート酸化膜7を介して設けられるゲート電極8と、前記エミッタ領域4表面と前記ベース領域3表面に共通に接触するエミッタ電極6と、第2主面のp型コレクタ層2とを有するIGBTと、該IGBTに離間して第1主面に形成されるn型ウェル領域15表面層にn型カソード領域11とp型アノード領域12を有する温度センサダイオードを備え、前記n型ウェル領域15がp型ウェル領域16の表面層に形成され、前記温度センサダイオードのライフタイムが1μs以下に設定されている半導体装置とする。

(もっと読む)

垂直集積システム

【課題】コストのかかる空間をとらずに電子部品内に個別パッシブ部品を組み込むことが可能な垂直集積システムを提供する。

【解決手段】集積回路システム100は、半導体ダイ110の前面上に製造された第一のアクティブ層と、半導体ダイ110の裏面上の第二の予め製造された層とを含み、その第二の予め製造された層は、その中に埋め込まれた電気部品を有し、その電子部品は、少なくとも一つの個別パッシブ部品140を含む。また、集積システム100は、第一のアクティブ層及び第二の予め製造された層を結合する少なくとも一つの電気経路150も含む。

(もっと読む)

半導体装置

【課題】 温度検出素子を備えた半導体装置において、温度検出素子が半導体素子の発熱を検出する時間を短縮する。

【解決手段】P型領域とN型領域を有する温度検出素子を備えた半導体装置を提供する。この半導体装置の温度検出素子のP型領域は、P型コンタクト部と、P型コンタクト部から第1方向に延びるP型接合部とを有しており、N型領域は、N型コンタクト部と、N型コンタクト部からP型接合部に沿って第1方向と逆方向に延びると共にP型接合部と接合しているN型接合部とを有するN型領域とを有している。P型接合部の第1方向に直交する第2方向の幅は、P型コンタクト部の第2方向の幅よりも狭く、N型接合部の第2方向の幅は、N型コンタクト部の第2方向の幅よりも狭い。

(もっと読む)

半導体装置

【課題】放熱効率が高く低コストでの実装が可能な半導体装置を提供する。

【解決手段】第1の方向に延在するゲート電極を有する複数のトランジスタを有し、複数のトランジスタが第1の方向と交差する第2の方向に配置されたトランジスタアレイ54と、トランジスタアレイの第1の方向に配置され、複数のトランジスタのソース領域に電気的に接続されたパッド電極50とを有する。

(もっと読む)

電力増幅器

【課題】複数のトランジスタを均一に動作させ、低消費電力及び良好な歪特性を実現する。

【解決手段】高周波信号を増幅する電力増幅器100であって、上部電極120a及び下部電極120bを有し、高周波信号が入力される整合容量120と、整合容量120の下部電極120bから出力される高周波信号を増幅する複数のトランジスタ110が所定の方向に並んで配置されているトランジスタ列とを備え、トランジスタ列に隣り合う領域において、トランジスタ列の両端から略等しい距離には、接地されたビアホール170が形成され、下部電極120bは、ビアホール170を挟んで高周波信号が均等に分配されるように配置されたマイクロストリップ線路であり、複数のトランジスタ110のベース端子に接続される。

(もっと読む)

半導体装置およびそれを用いた無線通信機器

【課題】半導体装置の熱抵抗を低減すること、および小型化できる技術を提供する。

【解決手段】複数の単位トランジスタQを有する半導体装置であって、半導体装置は、単位トランジスタQを第1の個数(7個)有するトランジスタ形成領域3a、3b、3e、3fと、単位トランジスタQを第2の個数(4個)有するトランジスタ形成領域3c、3dとを有し、トランジスタ形成領域3c、3dは、トランジスタ形成領域3a、3b、3e、3fの間に配置され、第1の個数は、第2の個数よりも多い。そして、単位トランジスタは、コレクタ層と、ベース層と、エミッタ層とを備えており、エミッタ層上には、エミッタ層と電気的に接続されたエミッタメサ層が形成され、このエミッタメサ層上に、エミッタ層と電気的に接続されたバラスト抵抗層が形成されている。

(もっと読む)

高周波スイッチ

【課題】出力特性が優れた高周波スイッチを提供する。

【解決手段】本発明の実施形態の高周波スイッチは、入力端子ANT1と複数のスイッチング素子と複数の高周波信号線と複数の出力端子RF1〜RF8とからなる高周波スイッチ回路部を有する高周波スイッチICチップ10を備える。前記入力端子ANT1と前記複数の出力端子の各出力端子RF1〜RF8は、それぞれ等しい長さの高周波信号線H1〜H8で接続される。前記複数の出力端子RF1〜RF8は、前記高周波スイッチICチップの外周の表面上に配置される。前記入力端子ANT1は、前記高周波スイッチ回路部の中心に配置される。

(もっと読む)

半導体チップ及びそれを搭載した半導体モジュール

【課題】半導体チップに安定した電源電流を供給したり、電源から信号系へ混入する雑音を低くするための、半導体デバイスの電源流入及び電源流出端子の端子数の低減と、前記半導体チップを搭載した実装面積の低減を可能とする半導体モジュールを提供する。

【解決手段】半導体チップ20の両面に電源系と信号系の電気的接続端子を振り分けて配置する。大電流が流れる流路の許容電流値を大きくする構成により、少ない端子数でも安定な電源供給が可能、信号系への雑音混入を低減、ピン数の低減による実装面積の低減、放熱効果の増大などが可能となる。また、この半導体チップ20を搭載した半導体モジュールにより、大電流が流れる高速動作でも安定した特性を実現できる。

(もっと読む)

電流制御用半導体素子、およびそれを用いた制御装置

【課題】センス比の温度分布依存性を除去し、センスMOSFETによる電流検出の精度を向上できる電流制御用半導体素子、およびそれを用いた制御装置を提供することにある。

【解決手段】電流制御用半導体素子1は、同一半導体チップ上に、電流を駆動するメインMOSFET7と、メインMOSFET7に並列に接続し、メインMOSFETの電流を分流して電流検出を行うためのセンスMOSFET8とを有する。メインMOSFETは、複数のチャネルを有し、一列に配列されたマルチフィンガーMOSFETを使用して形成される。マルチフィンガーMOSFET7の中心から、最も遠いチャネルまでの距離をLとすると、マルチフィンガーMOSFETの中心から(L/(√3))の位置に最も近いチャネルを、センスMOSFET8のチャネルとして使用する。

(もっと読む)

インバータ回路

【課題】1チップ化しつつ、高温化による誤動作を抑制し、かつ、半導体パワー素子に流れる電流を低減し、チップサイズの増大を抑制することができるインバータ回路を提供する。

【解決手段】コンバータ電源回路部2の電源供給ライン8中、例えば、IPD20におけるパワーMOSFET220のハイサイド側に電流制限抵抗240を備える。この電流制限抵抗240によって電源供給ライン8に流れる電流の電流値を制限することができるため、パワーMOSFET220での発熱を抑制することが可能となる。したがって、インバータ回路1内の素子の定格温度を超えることを防止することが可能となり、誤動作が生じることを抑制できる。これにより、インバータ回路1の信頼性の向上を図ることが可能となる。また、パワーMOSFET220として必要な能力を軽減することが可能となり、大面積な素子としなくても済む。

(もっと読む)

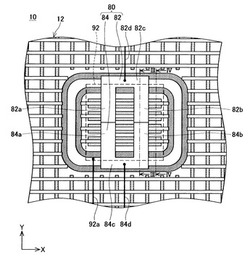

半導体装置およびその製造方法

【課題】絶縁膜の表面に対して平坦化する工程を行わなくても、コイルの延設方向が構成部材の積層方向に対して傾くことを抑制することができる半導体装置の製造方法を提供する。

【解決手段】平坦な一面を有する支持基板80を二枚用意する工程と、支持基板80それぞれの平坦な一面上に構成部材30〜60を形成する工程と、二枚の支持基板80に配置された構成部材30〜60を対向させて配置した後加圧しながら貼り合わせ、当該構成部材30〜60に備えられている支持基板80それぞれの平坦な一面を平行としつつ、構成部材30〜60それぞれの配線部32〜62を接続部32a、32b〜62a、62bを介して連結する工程を含む工程を行うことにより、配線部32〜62および接続部32a、32b〜62a、62bで構成されるコイル20を内部に含み、積層方向の両端部分に支持基板80を備えたコイル層21を形成する工程と、を行う。

(もっと読む)

半導体装置

【課題】dv/dtサージにより、支持基板と活性層との間の絶縁膜にて構成される寄生容量を充放電する変位電流による回路誤動作を防止する。

【解決手段】低電位基準回路部LVおよび高電位基準回路部HVを構成する絶縁分離された半導体素子の外周に、n型ガードリング42c等を形成すると共に、活性層2cの埋込絶縁膜2b側にn型ガードリング埋込層42c等と同じ導電型の深いn型拡散領域42b等を形成する。また、活性層2cにて構成されるn-型層42a等の中にp型ウェル42d等を形成し、このp型ウェル42d内に半導体素子を形成する。n型ガードリング42c等とp型ウェル42d等は、それぞれ逆バイアスまたは同電位となるように電位固定する。

(もっと読む)

1 - 20 / 208

[ Back to top ]