Fターム[5F038CA05]の内容

半導体集積回路 (75,215) | レイアウト (7,547) | チップ平面上でのレイアウト (5,921) | 領域設定 (1,104)

Fターム[5F038CA05]に分類される特許

1 - 20 / 1,104

半導体集積回路

半導体集積回路

【課題】回路規模を低減しつつ任意の論理を実現可能な半導体集積回路を提供する。

【解決手段】実施形態の半導体集積回路は、第1論理ブロックを少なくとも1つ含む第1回路群と、第1論理ブロックよりも多い数の第2論理ブロックを含む第2回路群と、入力データを第1論理ブロックまたは第2論理ブロックへ入力する機能、および、第1論理ブロックまたは第2論理ブロックから出力される出力データを外部へ出力する機能を有する入出力部とを含む。第1回路群は、第1スイッチブロックと、第1電源制御回路とを有する。第1電源制御回路は、第1回路群に含まれる第1論理ブロックおよび第1スイッチブロックに対する電力の供給および停止を共通に制御する。第2回路群は、第2スイッチブロックと第2電源制御回路とを有する。第2電源制御回路は、第2回路群に含まれる論理ブロックおよび第2スイッチブロックに対する電力の供給および停止を共通に制御する。

(もっと読む)

半導体装置

【課題】インダクタの下方に位置する素子分離膜に開口を設けてその開口内に半導体基板を残しつつ、インダクタの下方に位置する半導体基板に渦電流が発生することを抑制する。

【解決手段】インダクタ300は、多層配線層200に形成されており、素子分離膜12の上方に位置している。開口13は、素子分離膜12のうち少なくとも平面視でインダクタ300と重なる領域に形成されている。また、素子分離膜12とインダクタ300の間に位置するいずれの層にも、インダクタ300と半導体基板10の間をシールドするシールド導電部材は形成されていない。

(もっと読む)

半導体集積回路及びその設計方法

【課題】チップサイズを増大することなく、キャパシタの容量を増やすことができる半導体集積回路を提供する。

【解決手段】半導体基板10上にメインブロック11と周辺ブロック12とが混載された半導体集積回路において、半導体基板10上のメインブロック11に形成され、第1のトレンチキャパシタを有するメイン回路と、半導体基板10上の周辺ブロック12に形成され、第2のトレンチキャパシタを有するアナログ回路とを備える。

(もっと読む)

半導体装置

【課題】 過電流検出による保護と、温度検出による保護とを、好適に行うことが可能な半導体装置を提供する。

【解決手段】 半導体基板を有する半導体装置であって、半導体基板が、メイン素子領域と、メイン素子領域よりも小さい電流が流れるサブ素子領域を有しており、サブ素子領域が、半導体基板を平面視したときに半導体基板の中心と重なる位置に形成されており、半導体基板上であって、半導体基板を平面視したときにサブ素子領域と重なる位置に、温度検出素子が形成されている。

(もっと読む)

半導体集積回路のレイアウト設計方法

【課題】SETUP時間とHOLD時間のどちらも満足させるタイミングの調整が可能な技術を提供する。

【解決手段】半導体集積回路の配置配線レイアウトを決定した後に、所定の信号線を伝搬するデータのタイミング情報に基づいて、タイミング違反を有する違反データの遅延情報を抽出する。その抽出された遅延情報に基づいて、タイミング違反を解消するための追加すべき容量値を算出する。また、違反データを伝搬する配線のレイアウト配置情報に基づいて、違反データを伝搬する配線の近傍の電源容量セルを検出する。また、算出された容量値に基づいて、検出された電源容量セルを、電源容量セルとレイアウト外形・電源/GND配線配置位置が同じ調整容量セルに置き換える。そして、置き換えた調整用容量セルのゲートと違反データを伝搬する配線とを接続して再配線を実行する。

(もっと読む)

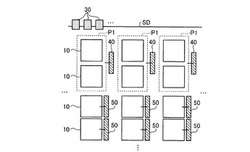

半導体集積回路、半導体集積回路の設計方法及び設計装置並びにプログラム

【課題】セルベースの半導体集積回路において、異なるセル高さを有するセルを効率良く配置するための技術を提供する。

【解決手段】半導体集積回路が、基準ハイトセル30、マルチハイトセル40、VDD電源配線、VSS電源配線を備え、マルチハイトセルは、Y軸方向に延伸するVDD側電源供給配線5B、VSS側電源供給配線6Bを備え、基準ハイトセルの高さをa、マルチハイトセルの高さをb、VDD、VSS電源配線の幅をwとしたときに、VSS側電源供給配線は、少なくとも、マルチハイトセルの下端からw/2高さ方向に離れた位置とマルチハイトセルの下端からb−a−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられ、VDD側電源供給配線は、少なくとも、マルチハイトセルの下端からa+w/2高さ方向に離れた位置とマルチハイトセルの下端からb−w/2高さ方向に離れた位置の間の高さ範囲をカバーするように設けられる。

(もっと読む)

半導体記憶装置

【課題】半導体記憶装置において誤動作が生じる蓋然性を低減する。

【解決手段】積層配置されるメモリセルアレイ(例えば、酸化物半導体材料を用いて構成されているトランジスタを含むメモリセルアレイ)と周辺回路(例えば、半導体基板を用いて構成されているトランジスタを含む周辺回路)の間に遮蔽層を配置する。これにより、当該メモリセルアレイと当該周辺回路の間に生じる放射ノイズを遮蔽することが可能となる。よって、半導体記憶装置において誤動作が生じる蓋然性を低減することが可能となる。

(もっと読む)

半導体装置

【課題】高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制する。

【解決手段】半導体装置1は、高周波配線、およびダミー導体パターン20(第2のダミー導体パターン)を備えている。ダミー導体パターン20は、高周波配線と相異なる層中に形成されている。ダミー導体パターン20は、平面視で、高周波配線と重なる領域を避けるように配置されている。これにより、高周波配線と相異なる層に設けられたダミー導体パターンに発生する渦電流を抑制できる。

(もっと読む)

半導体装置

【課題】バラスト抵抗の幅を広げることなく、バラスト抵抗の許容電流量を大きくする

【解決手段】バラスト抵抗200を構成する抵抗210の少なくとも一つは、第1抵抗212及び第2抵抗214を有している。第1抵抗212は、保護素子100内で電流が流れる方向である第1の方向(図1ではX方向)に延伸している。第2抵抗214は、第1抵抗212に並列に接続され、第1の方向に延伸している。そして第2抵抗214は、第1抵抗212と同一直線上に位置している。

(もっと読む)

半導体装置

【課題】半導体基板の上方にコイルが設けられた半導体装置において、コイル直下の半導体基板に回路を形成することができる半導体装置を提供する。

【解決手段】半導体装置は、一面11を有する半導体基板10と、半導体基板10の一面11に形成された絶縁層20と、絶縁層20の上方に形成されたコイル30と、を備えて構成されており、半導体基板10はコイル30の直下にスリット12を備えている。このスリット12は、コイル30のうち、半導体基板10の一面11に平行な面方向のうちの一方向に沿って形成された部分の直下に位置している。これにより、スリット12を境界として半導体基板10の渦電流面積が小さくなるので、半導体基板10に発生する渦電流による損失が低減し、コイル30の下部に位置する半導体基板10に回路を形成することが可能となる。

(もっと読む)

半導体装置およびその製造方法

【課題】窒化ガリウム(GaN)系のHEMTを保護するダイオード構造を備えた半導体装置とその製造方法を提供する。

【解決手段】基板10のうちGaN層13に2次元電子ガスが生成される領域が活性層領域40とされ、基板10のうち活性層領域40を除いた領域にイオン注入が施されていることにより活性層領域40とは電気的に分離された領域が素子分離領域50とされている。そして、ダイオード60は素子分離領域50の層間絶縁膜20の上に配置されている。このように、基板10のうちHEMTが動作する活性層領域40とは異なる素子分離領域50を設けているので、1つの基板10にGaN−HEMTとダイオード60の両方を備えた構造とすることができる。

(もっと読む)

半導体装置およびその試験方法

【課題】ワイヤボンディング時のストレスでボンディングパッド下の絶縁層のダメージを電気的に検出できる半導体装置および導入されたダメージを検出して良品、不良品を判定できる半導体装置の試験方法を提供すること。

【解決手段】酸化膜4上にポリシリコン5を配置し、このポリシリコン5にpnダイオード9を形成し、nカソード層6上に層間絶縁膜10を挟んで第1ボンディングパッド11を配置する。また、pアノード層7上に第2ボンディングパッド12を配設することで、層間絶縁膜10に導入されるダメージが層間絶縁膜10を貫通するか否かを電気的に検出できる半導体装置(パワーICなど)とすることができる。

(もっと読む)

半導体集積回路装置

【課題】半導体集積回路装置において、I/Oセルの高さを低減すると同時に幅の増大を防ぐことでI/Oセルの占める領域の面積を削減すること。

【解決手段】レベルシフタ回路、I/Oロジック回路およびI/Oバッファ回路を含むI/Oセルがコア領域の周囲に配置された半導体集積回路装置であって、I/Oロジック回路が配置されたI/Oロジック領域、および、I/Oバッファ回路が配置されたI/Oバッファ領域は、I/Oセルに対するパッドが配置された領域と重なり合うとともに、コア領域の辺に平行な方向に互いに並んで配置されている。

(もっと読む)

半導体装置

【課題】スパイラルインダクタを有する半導体装置における寄生容量の低減と、Q値の低下を抑制すること。

【解決手段】半導体基板と、前記半導体基板の表面近傍に設けられた複数個の素子分離領域と、前記素子分離領域間の半導体基板上に設けられた能動素子部と、基板上に積層された複数の配線層と、前記素子分離領域のうち第1の素子分離領域の鉛直上方であって、かつ、前記配線層のうち少なくとも最上の配線層に設けられたスパイラルインダクタとを備え、前記スパイラルインダクタが形成されたインダクタ形成領域の鉛直下方であって、かつ、前記第1の素子分離領域の半導体基板表面上にシリサイド形成防止膜が形成されていることを特徴とする半導体装置。

(もっと読む)

半導体装置

【課題】従来の半導体装置においては、配線の伝送特性が不安定となってしまう。

【解決手段】半導体装置1は、配線10、およびダミー導体パターン20を備えている。配線10は、5GHz以上の周波数を有する電流が流れる配線である。配線10の近傍には、ダミー導体パターン20が配置されている。ダミー導体パターン20の平面形状は、180°を超える内角を有する図形に等しい。

(もっと読む)

半導体ウエハ、半導体装置、および、半導体装置の製造方法

【課題】半導体チップのチップ面積の削減を図るとともに、半導体チップへの入力を記憶させる時間を短縮する。

【解決手段】本発明の半導体ウエハ1は、チップ領域10に形成され、絶縁膜を有し、電圧の印加による絶縁膜の絶縁破壊により導通状態となる複数のアンチヒューズ14を有するアンチヒューズ回路12と、チップ領域10を区画するダイシング領域20に複数のアンチヒューズ14の各々に対応して形成され、配線を有し、レーザー照射による配線の切断により非導通状態となる複数のレーザーヒューズ24を有するレーザーヒューズ回路22と、複数のアンチヒューズ14のうち、半導体チップへの入力に応じて非導通状態とされたレーザーヒューズ22に対応するアンチヒューズ14の有する絶縁膜に、電源からの電圧を印加させて、そのアンチヒューズ14を導通状態とする制御回路13と、を有する。

(もっと読む)

半導体装置

【課題】 貫通ビアを用い積層した半導体装置においては、信号を伝送する貫通ビアがオープンやショートした場合に、その貫通ビアを回避して積層チップ全体を正常動作させるために、複雑な回路を構成が必要であった。

【解決手段】 信号を伝送する貫通ビアにおいて、ビアの内壁を構成するシリコンに高い不純物の領域を形成して貫通導体とシリコン基板が接触したときに基板に接続されているVSSなどの基準電位に誘導する。故障モードを固定できるため、冗長化/復号化回路が簡単になるうえ、必要な冗長貫通ビアの本数を削減することができる。

(もっと読む)

半導体ウエハ、半導体ウエハ検査装置、及び半導体ウエハの検査方法

【課題】本発明は、半導体ウエハの検査において、半導体ウエハの裏面電極の端子としての機能を維持しつつ、半導体ウエハに過度の力がかかることを防止できる半導体ウエハ、半導体ウエハ検査装置、及び半導体ウエハの検査方法を提供することを目的とする。

【解決手段】本発明に係る半導体ウエハは、ダイシングラインを隔てて複数のチップが並ぶ半導体ウエハの表面側に形成された表面電極と、該半導体ウエハの裏面側に、該ダイシングラインを隔てて形成された複数の裏面電極と、該半導体ウエハの裏面側に、該ダイシングラインを跨いで該複数の裏面電極を電気的に接続する接続パターンと、を備える。該複数の裏面電極のうちの少なくともひとつは、該半導体ウエハのバイアホールを介して該表面電極と電気的に接続される。

(もっと読む)

半導体装置、半導体ウェハ及び半導体装置の製造方法

【課題】ダイシングの際にクラック発生を抑制できる半導体装置を提供する。

【解決手段】半導体基板の上に形成された複数の配線層と、前記複数の配線層の間に配置されたビア層と、前記複数の配線層に形成された導電膜と、前記ビア層の上下の前記配線層の前記導電膜と接続するビアプラグV5とを有し、スクライブ領域31は、チップ領域の外周であって前記半導体基板の縁に接して位置し、前記スクライブ領域31は前記縁に接するパッド領域33を有し、前記パッド領域33は、前記複数の配線層の各々に、平面視において相互に重なって配置され、前記複数の配線層は、第1の配線層と第2の配線層を有し、前記第1の配線層の前記導電膜は、前記パッド領域33の全面に形成された第1の導電パターン55を有し、前記第2の配線層の前記導電膜は、前記パッド領域の一部に形成された第2の導電パターン50を有する。

(もっと読む)

1 - 20 / 1,104

[ Back to top ]